Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсккх

Соцкалкстическнх

Реслублмк ()826417 (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.09.79 (21) 2806407/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл..3

G 11 С 11/00

Гееударстееннык кемнтет (53) УДК 681.327..66 (088.8) Опубликовано 30.04.81. Бюллетень № 16

Дата опубликования описания 05.05.81 о делам нзебретеннй и открытий

А. И. Савельев, В. И. Косов, Л. Ф. Соколов и И. И. Косов (72) Авторы изобретения

Московский ордена Трудового Красного Зн ени текстильный институт

I (71) Заявитель

1- (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах с повышенными требованиями к информационной надежностии.

Известно запоминающее устройство, содержащее блок памяти, подсоединенный через разделительные диоды к формирователям разрядных токов и непосредственно к формирователям адресных токов, подсоединенных к блоку управления и к входам усилителей считывания, соединенных с чйсловым регистром (1) .

В этом устройстве не предусмотрена коррекция разрядного тока при организации

ЗУ по принципу «ratchet»-записи, что снижает его информационную надежность.

Наиболее близким техническим решением к предлагаемому является устройство, в котором предусмотрена «ratchet»-запись, т. е. запись пачкой адресных токов и перекрывающим по времени эту пачку импульсов положительным разрядным током при записи «1» и отрицательным при записи «О» (2), В данном запоминающем устройстве не предусмотрено симметричное перемагничивание запоминающих ферритовых элементов при записи «1» и «О», так как последний импульс адресного тока записи всегда при

«ratchet»-записи положительный, а разрядные токи записи имеют разную полярность. Это приводит к тому, что амплитуды считанных сигналов «1» и «О» имеют различные значения, что в значительной мере снижает информационную надежность этого запоминающего устройства.

Цель изобретения — повышение инфор1в мационной надежности ЗУ за счет выравнивания аМплитуд считанных сигналов «1» и

«О».

Поставленная цель достигается тем, что в запоминающее устройство, содержащее блок памяти, к одним входам которого под ключены адресные формирователи, к другим — через разделительные элементы разрядные формирователи, а выходы блока памяти соединены с входами усилителей считывания, выходы которых подключены к входам числового регистра, блок управления, выход которого соединен соответственно с входами числового регистра, а второй— с входами адресных формирователей, вве826417

2О

35

Формула изобретения

55 дены дополнительные разделительные элементы, дополнительные разрядные формирователи, группы элементов И и счетчик, входы которого подключены к четвертому и пятому выходам блока управления, третий выход которого соединен с первыми входами элементов И, вторые входы которых соединены с выходами числового регистра, третьи входы элементов И одной из групп подключены к выходам счетчика, выходы элементов И соединены с входами соответствующих разрядных формирователей, соответствующие входы блока памяти через дополнительные разделительные элементы подключены к входам соответствующих дополнительных разрядных формирователей.

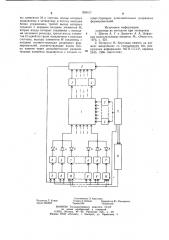

На чертеже представлена схема запоминающего устройства.

Запоминающее устройство содержит блок 1 памяти, соединенный с адресными формирователями 2, усилителями 3 считывания, с разделительными элементами 4, с дополнительными разделительными элементами 5. Разделительные элементы 4 подключены к разрядным формирователям 6, а дополнительные разделительные элементы 5 — к дополнительным разрядным формирователям 7. Входы разрядных формирователей 6 соединены с выходами элементов

И 8 первой группы, первые входы которых соединены с выходами числового регистра 9, соединенного с выходами усилителей 3 считывания, с первыми входами элементов И

10 второй группы, вторые входы которых подключены к вторым входам элементов И первой группы и к третьему выходу блока

11 управления, первый и второй выходы которого соединены соответственно с вторым входом числового регистра 9 и входами адресных формирователей 2. Четвертый и пятый входы блока 11 управления подключены соответственно к первому и второму входам счетчика 12, выход которого подключен к третьим входам элементов И 10 второй группы.

В режиме записи блок 11 управления вырабатывает на первом выходе управляющий сигнал, по которому в соответствии с кодом числа, находящегося в числовом регистре 9, подаются потенциалы на первые входы элементов И 8 первой группы и первые входы элементов И 10 второй группы, а импульс с третьего выхода блока 11 управления поступает на вторые входы элементов И 8 первой группы и на вторые входы элементов И 10 второи группы. Однако в каждом разряде срабатывает или разрядный формирователь 6, вырабатывающий положительный сигнал, поступающий на разделительный элемент 4 и далее в блок 1 памяти для записи «1», или разрядный формирователь 7, вырабатывающий отрицательный сигнал, поступающий на разделительные элементы 4, а затем в блок 1 памяти для записи «О» в зависимости от кода числа. Затем с некоторой задержкой по времени относительно вышеуказанных сигналов на втором выходе блока ll управления вырабатывается сигнал для запуска адресных формирователей 2. По этому сигналу запускаются адресные формирователи

2, вырабатывающие по соответствующему адресу заданное количество положительных и отрицательных импульсов тока, т. е. импульсов «ratchet»-записи.

В этом режиме при записи «I» амплитуда положительного разрядного тока постоянна, а адресные формирователи всегда выдают последний импульс «ratchet»-записи положительной полярности, который заканчивается немного раньше импульса раз рядного тока. Однако при записи «О», т. е. при записи отрицательным разрядным током, для исключения асимметрии считанных сигналов (для исключения уменьшения амплитуды считанного сигнала «О» по сравнению с амплитудой сигнала «1») должен возрасти разрядный ток записи при приходе последнего импульса в пачке адресных токов. Поэтому из блока управления 11, с пятого выхода, в счетчик 12 поступает текущее значение количества положительных импульсов и по последнему расчетному импульсу счетчик 12 вырабатывает управляющий потенциал, поступающий на третий вход элементов И 10 второй группы. По этому управляю-. щему потенциалу срабатывают дополнительные разрядные формирователи 7 тех разрядов, в которых происходит запись «О». Это увеличивает отрицательный разрядный ток в момент прихода последнего положительного адресного тока «ratchet»-записи. Такая запись «О» обеспечивает равные условия записи «1» и «О», т. е. обеспечивает при считывании получение одинаковых выходных считанных сигналов информационной «1» и информационного «О».

В режиме считывания в ЗУ обычным образом работают только адресные формирователи 2.

Запоминающее устройство, содержащее блок памяти, к одним входам которого подключены адресные формирователи, к другим — через разделительные элементы разрядные формирователи, а выходы блока памяти соединены с входами усилителей считывания; выходы которых подключены к входам числового регистра, блок управления, выход которого соединен соответственно с входами числового регистра, а второй с входами адресных формирователей, отличающееся тем, что, с целью повышения надежности устройства, в него введены дополнительные разделительные элементы, дополнительные разрядные формирователи, груп826417

СоставиТель Л. Амусьева

Техред A. Бойкас Корректор Ю. Макаренко

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4

Редактор Л. Кинив

Заказ 234 l/25 пы элементов И и счетчик, входы которого подключены к четвертому и пятому выходам блока управления, третий выход которого соединен с первыми входами элементов И, вторые входы которых соединены с выходами числового регистра, третьи входы элемен- 5 тов И одной из групп подключены к выходам счетчика, выходы элементов И соединены с входами соответствующих разрядных формирователей, соответствующие входы блока памяти через дополнительные разделительные элементы подключены к входам со4 ответствующих дополнительных разрядных формирователей.

Источники информации, принятые во внимание при экспертизе

1. Шигин А. Г. и Дерюгин А. А. Цифровые вычислительные машины. М., «Энергия», 1975, с. 221.

2. Петерсон М. Бортовая память на элемент микробиакс со считыванием без разрушения информации. МГП СССР, перевод

2433, 1966 (прототип).