Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ()826419 (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.08.79 (21) 2813935/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

G 11 С 11/00

Гееударстееннмй кемитет (53) УДК 681.327 (088.8) Опубликовано 30.04.81. Бюллетень № 16

Дата опубликования описания 05.05.81 пе делам изобретений

1 и еткрмтий с

В. И. Липко, Д. Д. Колос и Н. И. Ш1ак . . .. 1 .; .,;"

t и г .к .5 %кии1 (72) Авторы изобретения (7!) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам и может быть использовано во внешних устройствах ЭВМ.

Известно оперативное запоминающее устройство,предназначено для временного хранения, записи и чтения данных, выполнено с применением элементов памяти на интегральных микросхемах и содержит узел хранения, узел дешифрации адреса и узлы приема и выдачи информации (1).

Недостатком устройства является сложность управления узлом хранения, имеющим двухкоординатную систему выборки адреса, и необходимость использования специальных согласующих делителей входных напряжений.

Наиболее близким техническим решением к предлагаемому является оперативное запоминающее устройство (ОЗУ), содержащее накопители и блок для управления памятью, состоящий из генератора тактовых импульсов, счетчика тактовых импульсов, дешифраторов, формирователя управляющих сигналов, регистров адреса и слова, счетчика, делителей частоты, триггера, элементов И и ИЛИ (2).

Недостаток этого устройства состоит в больших аппаратурных затратах, приводящих к снижению надежности устройства и возвра стан ию потребляемой мощности от источника питания.

Цель изобретения — упрощение конструкции устройства и повышение его надежности при сохранении высокого быстродействия.

Поставленная цель достигается тем, что в оперативное запоминающее устройство, содержащее накопители, счетчик и элемент

ИЛИ, введены . триггеры, элементы 2И—

ИЛИ вЂ” НЕ и ИЛИ вЂ” НЕ и элемент НЕ, причем одни из входов накопителей подключены к одним из выходов счетчика, а другие—

is соответственно к выходам элементов 2И—

ИЛИ вЂ” НЕ и ИЛИ вЂ” НЕ, выход элемента

ИЛИ соединен со счетным входом счетчика, единичные выходы триггеров подключены к одним из входов элементов 2И вЂ” ИЛИ—

НЕ, другие входы которых соединены соответственно со входами элемента ИЛИ, являющимися соответственно входами чтения и записи устройства, один из входов элементов ИЛИ вЂ” НЕ соединены со входом за826419 писи устройства, другие — с выходом элемента НЕ, вход которого подключен ко входу чтения устройства, нулевой выход каждого триггера, кроме первого, подключен к одному из входов сброса предыдущего триггера, другие выходы счетчика соединены соответственно со входами установки тригге-. ров, кроме первого, вход сброса счетчика, вход установки первого триггера и вторые входы сброса триггеров являются входом установки устройства.

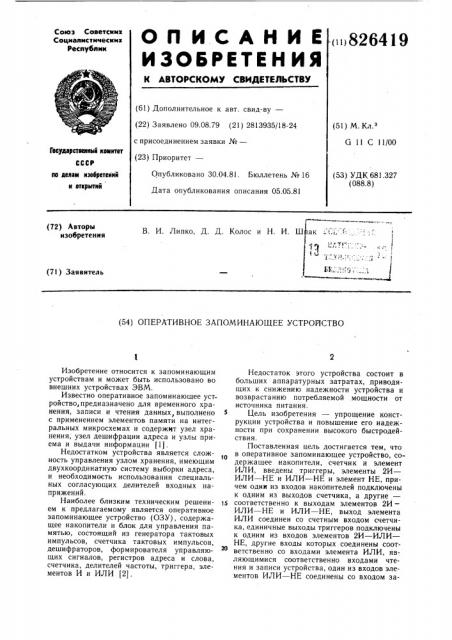

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит накопители 1 — 5, представляющие, например, блок интегральной оперативной памяти на 64 бит, организованный в 16 четырехразрядных ячеек памяти с дешифратором четырехразрядного двоичного кода адреса и выполненный по схеме последовательного ступенчатого накопления, семиразрядный двоичный счетчик 6, триггеры 7 — 11, представляющие тетрадные счетчики, элементы ИЛИ вЂ” HE 12—

16, 2И вЂ” ИЛИ вЂ” НЕ 17 — 21, ИЛИ 22, НЕ 23.

При этом адресные входы накопителей

1 — 5 соединены с одними из выходов счетчика 6, входы разрешения записи накопителей 1 — 5 соединены соответственно с выходами элементов ИЛИ вЂ” НЕ 12 — 16, а входы разрешения выборки — с выходами элементов 2И вЂ” ИЛИ вЂ” НЕ 17 — 21. Одни из входов элементов ИЛИ вЂ” HE 12 — 16 соединены с входом записи 24, другие входы элементов

ИЛИ вЂ” НЕ 12-16 соединены с выходом элемента НЕ 23, вход которого соединен с входом чтения 25. Выход элемента ИЛИ 22 соединен со счетным входом счетчика 6.

Единичные выходы триггеров 7 — 11 подключены к одним из входов элементов 2И—

ИЛИ вЂ” НЕ 17 — 21, другие входы которых соединены соответственно со входами элемента ИЛИ 22, являющимися соответственно входами чтения 25 и записи 24 устройства. Нулевой выход каждого триггера 8—

ll подключен к одному из входов сброса предыдущего триггера 7 — 10. Другие выходы счетчика 6 соединены соответственно со входами установки триггеров 8 — 11. Вход сброса счетчика 6, вход установки триггера 7 и вторые входы сброса триггеров 8—

11 являются входом установки 26 устройства.

Накопители 1 — 5 имеют три режима работы: хранение информации, запись информации и считывание информации. Для организации этих режимов работы они имеют два управляющих входа: вход разрешения выборки 27 и вход разрешения записи 28. При подаче напряжения логической единицы (высокого уровня) на входе разрешения выборки 27 не выбирается ни одна из 16 ячеек памяти, при этом накопители работают в режиме хранения независимо от того, какой уровень напряжения на входе разрешения записи 28.

При поступлении на вход записи 24 положительного импульса эаписи на соответствующем входе элемента 2И вЂ” ИЛИ вЂ” НЕ

l7 появляется высокий уровень, на его выходе и на входе разрешения выборки 27 накопителя 1 появляется низкий уровень напряжения, т. е. организуется режим выборки адреса ячейки памяти. На вход разрешения записи 28 накопителя 1 поступает постоянный низкий уровень с выхода элемента

ИЛИ вЂ” HE 12, при этом происходит запись информации первой колонки перфокарты.

По заднему фронту положительного импульса записи в счетчик 6 записывается «1», и на выходе элемента 2И вЂ” ИЛИ вЂ” НЕ 17 появляется высокий уровень напряжения, который поступает на вход разрешения выборки 27 накопителя 1, и, таким образом, до

Для записи информации в выбранную ячейку памяти необходимо снять запрет выборки, т. е. подать уровень логического нуля (низкий уровень) на вход разрешения выборки 27 и на вход разрешения записи

28. Считывание информации выбранной ячейки производится при снятии запрета и подаче высокого уровня на вход разрешения записи 28.

Для записи информации 80 колонной перфокарты накопители 1 — 5 содержат 5 ступеней. В исходном состоянии перед началом работы подготавливается первая ступень, после выборки первых 16 адресов организуется режим хранения информации первой ступени и подготавливается вторая ступень и т. д.

В режиме записи информации устройство работает следующим образом.

Перед началом работы устройство отрицательным импульсом по входу 26 приводится в исходное состояние. Счетчик 6 и

?О триггеры 8 — 11 сбрасываются в нулевое состояние, триггер 7 устанавливается в единичное состояние. На всех выходах счетчика 6 и на входах дешифраторов адреса накопителей 1 — 5 присутствует низкий уровень напряжения, при этом в счетчике 6 записывается «О». С единичного выхода триггера 7 высокий уровень напряжения поступает на входы элемента 2И вЂ” ИЛИ—

НЕ 17. С единичных выходов триггеров 8—

11 низкий уровень напряжения поступает зп соответственно на входы элементов 2И—

ИЛИ вЂ” HE 18 — 21. На входах записи 24 и чтения 25 присутствует низкий уровень напряжения, который поступает на входы элементов 2И вЂ” ИЛИ вЂ” НЕ 17 — 21, при этом на выходе элемента HE 23 и на одном из з5 входов элементов ИЛИ вЂ” HE 12 — 16 присутствует высокий уровень напряжения. С выходов элементов 2И вЂ” ИЛИ вЂ” НЕ 17 — 21 высокий уровень напряжения поступает на входы разрешения выборки 27 накопителей

4О 1 — 5 и запрещает выборку ячейки памяти, таким образом, накопители 1 — 5 находятся в режиме хранения.

826419 поступления следующего импульса первая ступень накопителей 1 — 5 находится в режиме хранения.

При поступлении на вход 24 второго импульса записи на выходе элемента 2И—

ИЛИ вЂ” НЕ 17 и на входе разрешения выборки 27 накопителя 1 появляется низкий уровень, а на вход разрешения записи 28 этого же накопителя поступает постоянный низкий уровень напряжения с выхода элемента

ИЛИ вЂ” НЕ 12, таким образом, происходит запись информации второй колонки перфокарты. По заднему фронту второго импульса записи происходит запись «2» в счетчик

6, и на входе разрешения выборки 27 накопителя 1 появляется высокий уровень напряжения, при этом первая ступень накопителей 1 — 5 до поступления следующего импульса находится в режиме хранения.

Описанная последовательность работы устройства сохраняется до поступления на вход записи 24 16 импульса. При поступлении 16 импульса записи происходит запись информации 16 колонки перфокарты, т. е. в счетчик 6 записывается число «!6». С одного из выходОв счетчика 6 высокий уровень напряжения поступает на триггер 8 и устанавливает его в единичное состояние.

С нулевого выхода триггера 8 низкий уровень напряжения сбрасывает триггер 7.

На единичном выходе триггера 7 появляется низкий уровень напряжения, который поступает на входы элемента 2И вЂ” ИЛИ вЂ” НЕ 17, при этом независимо от того, какой уровень напряжения присутствует на других входах, на выходе элемента 2И вЂ” ИЛИ вЂ” НЕ 17 и на входе разрешения выборки 27 накопителя 1 устанавливается высокий уровень напряжения. Таким образом, первая ступень накопителей 1 — 5 находится в.режиме хранения для всех последующих импульсов записи, которые поступают на вход записи

24. С единичного выхода триггера 8 высокий уровень напряжения подается на входы элемента ЗИ вЂ” ИЛИ вЂ” НЕ 18, при этом подготавливается работа второй ступени накопителей 1 — 5 и т. д.

В режиме считывания информации накопителей 1 — 5 устройство работает следующим образом.

Перед началом работы устройство при,водится в исходное состояние отрицательным импульсом по входу 26. Для этого счетчик 6 и триггеры 8 — 11 сбрасываются в нулевое состояние, триггер 7 устанавливается в единичное состояние. На всех выходах счетчика 6 и на входах дешифраторов адреса накопителей 1 — 5 .устанавливается низкий уровень напряжения, а на единичном выходе триггера 7 и на одних из входов элемента 2И вЂ” ИЛИ вЂ” НЕ 17 — высокий уровень напряжения, на единичных выходах триггеров 8 — 11 и на одних из входов элементов

2И вЂ” ИЛИ вЂ” НЕ 18 — 21 — низкий уровень напряжения. На входах записи 24 и чтения

25, на одних из входов элементов ИЛИ вЂ” HE

12 — 16 и на других входах элементов 2И—

ИЛИ вЂ 17 21 — низкий уровень напряжения. На другие входы элементов

ИЛИ вЂ” HE 12 — 16 поступает высокий уро» вень напряжения с выхода элемента НЕ 23.

С выходов элементов ИЛИ вЂ” НЕ 12 — 16 низкий уровень напряжения поступает на входы разрешения записи 28 накопителей 1 — 5, а на их входы разрешения выборки 27 передается высокий уровень напряжения и за о прещает выборку ячеики памяти, при этом накопители 1 — 5 находятся в режиме хранения.

При поступлении на вход чтения 25 положительного импульса чтения организуется режим выборки адреса ячейки памяти накопителя 1 (аналогично описанному ранее режиму выборки по управляющему входу 24), на входе разрешения выборки 27 которого появляется отрицательный уровень напряжения, разрешающий выборку.

С выхода элемента НЕ 23 низкий уровень напряжения поступает на входы элементов

ИЛИ вЂ” НЕ 12 — 16, на выходах которых устанавливается высокий уровень напряжения, который поступает на входы разрешения записи 28 накопителей 1 — 5 и разрешает считывание информации 1 колонки перфокарты. По заднему фронту импульса считывания записывается «1» в счетчик 6, на выходе элемента 2И вЂ” ИЛИ вЂ” НЕ 7 и на входе разрешения выборки 27 накопителя

30 1 появляется высокий уровень напряжения.

Таким образом, до поступления следующего импульса считывания первая ступень накопителей 1 — 5 находится в режиме хранения.

Аналогично описанному организуется считывание при поступлении следующих импульсов считывания. После считывания информации первой ступени подготавливается вторая ступень, затем третья и т. д.

Таким образом, предлагаемое устройстgy во обеспечивает режим хранения, записи и чтения данных, и за счет того, что в устройстве, благодаря схемному решению, для дешифрации адреса выбираемой ячейки памяти, кроме входов дешифратора адреса, 43 используются входы разрешения выборки и разрешения записи накопителей I — 5. В данном случае не требуется дополнительного оборудования, что значительно упрощает устройство и повышает его надежность.

Предлагаемое устройство, кроме того, щ предусматривает возможность ступенчатого наращивания объема памяти. Это обеспечивается тем, что в устройство для каждой ступени вводится свой триггер и элементы 2И—

ИЛИ вЂ” НЕ для управления выборкой и

И

ИЛИ вЂ” НЕ для управления записью, что позволяет при использовании счетчиков с большим числом разрядов строить устройство с большим объемом памяти при относительно простой схеме управления.

826419

Формула изобретения

Составитель В. Ф. Рудаков

Редактор С. Кинив Техред А. Бойкас Корректор Ю. Макаренко

Заказ 23М/25 Тираж ++5 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Использование изобретения в устройстве считывания информации с механического носителя позволяет значительно повысить техническую скорость ввода информации в

ЭВМ, т. е. сокращает время обмена информацией между устройством ввода и ЭВМ за счет того, что в предлагаемом информация считывается с,перфокарты, записывается в узел временного хранения и затем выдается в ЭВМ в течение времени, которое ограничено только быстродействием электронной части устройства.

1О

Оперативное запоминающее устройство, 1S содержащее накопители, счетчик и элемент

ИЛИ, отличающееся тем, что, с целью повышения надежности устройства, оно содержит триггеры, элементы 2И вЂ” ИЛИ вЂ” НЕ и

ИЛИ вЂ” НЕ и элемент НЕ, причем одни из входов накопителей подключены к одним из ze выходов счетчика, а другие — соответственно к выходам элементов 2И вЂ” ИЛИ вЂ” НЕ и

ИЛИ вЂ” НЕ, выход элемента ИЛИ соединен со счетным входом счетчика, единичные выходы триггеров подключены к одним из входоь элементов 2И вЂ” ИЛИ вЂ” НЕ, другие входы которых соединены соответственно со входами элемента ИЛИ, являющимися соответственно входами чтения и записи устройства, одни из входов элементов ИЛИ—

НЕ соединены со входом записи устройства, другие — с выходом элемента НЕ, вход которого подключен ко входу чтения устройства, нулевой выход каждого триггера, кроме первого, подключен к одному из входов сброса предыдущего триггера, другие выходы счетчика соединены соответственно со входами установки триггеров, кроме первого, вход сброса счетчика, вход установки первого триггера и вторые входы сброса остальных триггеров являются входом установки устройства.

Источники информации, принятые во внимание при экспертизе

1. Шигин А. Г., Дерюгин А. А. Цифровые вычислительные машины (Память ЦВМ) .

М., «Энергия», 1975, с. 230 — 265.

2. Авторское свидетельство СССР по заявке № 2797738/18-24, кл. G 06 F 9/00, 16.07.79(прототип) .