Запоминанмцее устройство с блошровкой неисправных ячеек памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик (1!) 826425 (6! ) Дополнительное к авт. свид-ву— (22) Заявлено 3.08. 79 (2! ) 2809535/18-24 с присоединением заявки М = (5! )М. Кл.

G 11 С 29/00

Гасуддрстеенный камнтет гссР по делам нзабретеннй и аткрытнй (23) Ириоритет—

ОпУбликовано 30. 04. 8 ° Бюллетень 1не 6

Дата опубликования описания 30.04.8 1 (53) УДК 681. .327(088.8) (72) Авторы изобретения

О.А. Терзян и Л.1!. Чахоян (7! ) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ

НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ

Изобретение относится к запомина-, ющим устройствам (ЗУ). .Известны ЗУ с блокировкой неисправных ячеек памяти (! 1, $2 ).

В одном из известных устройств реализована замена отказавших ячеек памяти (ЯП) основного накопителя исправными ЯП из дополнительного накопителя !), Недостатком этого устройства являются большие аппаратурные затраты.

Из известных устройств наиболее близким техническим решением к изобретению является ЗУ, содержащее ре-гистр адреса, основной накопитель, .первый и второй дополнительные накопители, работающие при считывании параллельно с основным накопителем. Первый дополнительный накопитель содержит резервные ЯП, заменяющие отказавшие ЯП основного накопителя, Во втором дополнительном накопителе запоминаются коды неисправных адресов основного накопителя. Замена

2 информации отказавших ЯП информацией из резервных ЯП производится выходным селектором, входы которого соединены с информационными выходами основного и первого дополнительного накопителей, а его управление производится сигналом от дополнительного накопителя, возникающим при совпадении поступающего в ЗУ кода адреса с одним из хранимых во втором допол1О нительном накопителе кодов неисправных адресов (2 1.

Недостатком этого устройства является большое время считывания из ЗУ, организованного таким образом, что

15 из основного накопителя в соответст. вии со старшими разрядами кода адреса производится выборка одновременно нескольких слов, из которых затем блок выборки одного слова, управляемый поступающими позднее (часто поз-же выборки слов из основного накопителя) младшими разрядамй кода адреса, пропускает на выход ЗУ одно слово.

8264

30

Увеличение времени считывания ЗУ с блокировкой в котором младшие разряды приходят позже остальных, происходит из-за необходимости сравнения всех разрядов поступающего в ЗУ кода адреса с хранимыми во втором дополнительном накопителе кодами неисправных адресов. В случае, если младшие разряды кода адреса приходят позже выборки слов из основного на- !0 копителя, то потребуется значительное время, прежде чем проанализируют то, является ли пришедший адрес неисправным, после чего выдается сигнал чтения из основного или первого 15 дополнительного накопителя и нужная информация поступает на выход.

Цель изобретения — повьппение бысЮ тродействия ЗУ с блокировкой неисправI ных ЯП, когда часть разрядов кода адреса поступает в ЗУ позже остальных и осуществляет на выходе устройства выборку одного из нескольких одновременно считанных из основного накопителя слов.

Поставленная цель достигается тем, что запоминающее устройство с блокировкой неисправных ячеек памяти, содержащее основной и дополнительные накопители, регистр адреса, схему сравнения, коммутаторы и блок выборки информации, причем один из выходов регистра адреса подключен ко входам основного и первого дополнительнрго накопителей и к первым входам схемы сравнения и второго дсполнительного накопителя, другой выход регистра адреса соединен со вторым входом второго дополнительного накопителя и одним из входов блока, выборки информации, первый входы коммутаторов подключены к выходам основного накопителя, вторые — к выходу первого дополнительного накопителя, первый выход второго дополнительного накопителя соединен со вторым входом схемы сравнения,. введен дешифратор кода заменяемого числа, один вход которого подключен ко второму выходу второго дополнительного накопителя, другой;— к выходу схемы сравнения, а выходы соединены с третьими входами коммутаторов, выходы которых подключены ко входам блока выборки информации.

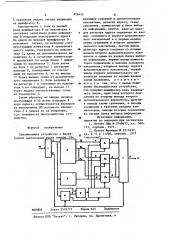

На чертеже изображена структур- 55 ная схема предлагаемого ЗУ.

Устройство содержит регистр 1 адреса, основной накопитель 2, пер25

4 вый 3 и второй 4 дополнительные накопители, схему 5 сравнения, коммутаторы 6, блок 7 выборки информации и дешифратор 8 кода заменяемого числа.

Первый и второй входы схемы сравнения подключены соответственно к одному из выходов регистра l и перво" му выходу накопителя 4, .второй выход которого соединен с первым входом дешифратора 8, второй вход ко- торого подключен к выходу схемы .5 сравнения. Первые, вторые и третьи входы коммутаторов 6 подключены соответственно к выходам накопителя

2, выходу накопителя 3 и выходам дешифратора 8. Накопитель 2 имеет выходы 9 -9 .

Устройство работает следующим образом.

При считывании поступающий на регистр 1 по входу 10 код адреса содержит две группы разрядов: А старших разрядов, поступающих на регистр

1 одновременно, и В яладших разрядов, поступающих значительно позже разрядов А.

Разряды А поступают на накопитель

2 и выбирают на его выход одновременно К=2 слов по К разрядов. В случае.

В исправной работы накопителя 2 все К слов передаются через коммутаторы 6 на блок 7 который под управлением пришедших позже В младших разрядов выдает на выходе ll одно из считанных из накопителей 2 слов, длиной

R разрядов, которое после проверки блоком контроля (не показан) передается на обработку.

Если в выдаваемом на выходе 11 слове обнаружена ошибка, вызванная отказом ячейки памяти накопителя 2, то правильная информация этого слова записывается в накопитель 3, а все разряды его кода адреса фиксируются в накопителе 4.

В дальнейшем при считывании из ЗУ по какому-либо адресу, в соответствии с кодом разрядов А происходит параллельная выборка К слов из накопителя 2, одного слова из накопителя 3 и кода неисправного адреса из накопителя 4 ° Схема 5 сравнения производит сравнение только разрядов

А, т.е. не ожидает прихода оставшихся В разрядов. В случае совпадения А разрядов, поступивших при считывании на регистр 1, с А разряда— ми, хранимыми в накопителе 4, схема

826425

Формула изобретения

ВНИИПИ Заказ 2519/72 Тираж 645 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

5 сравнения выдает сигнал включения на дешифратор 8.

Одновременно с этим на первый вход дешифратора 8 из накопителя 4 поступает записанная ранее информация В разрядов неисправного адреса

На одном иэ выходов дешифратора 8, возникает сигнал, по которому соответствующий коммутатор 6 пропускает вместо слова, считанного из накопителя 2, слово из дополнительного накопителя 3, а остальные коммутаторы

6 пропускают на входы блока 7 информацию из накопителя 2. Если. затем на блок 7 от регистра 1 поступают разряды В, совпадающие со считанными из накопителя 4, то на выходе

11 будет выдано слово из дополнительного накопителя 3. Если разряды В на регистре 1 и считанные из накопителя 4 не совпадают, на выходе ll будет выдано соответствующее слово из накопителя 2.

Таким образом, не ожидая анализа поступающих в ЗУ позже разрядов В кода адреса, осуществляется блокировка неисправных ЯП основного накопителя 3 и замена из на исправные, т.е. повышается быстродействие устройства.

Запоминающее устройство с блокировкой неисправных ячеек памяти,"со6 держащее основной И дополнительные накопители, регистр адреса, схему сравнения, коммутаторы и блок выборки информации, причем один из выходов регистра адреса подключен ко входам основного и первого: дополнительного накопителей и к первым входам схемы сравнения и второго доцолнительного накопителя другой выход

l6 регистра адреса соединен со вторым входом второго-дополнительного накопителя и одним as входов блока выбор-. ки информации, первые входы коммутаторов подключены к выходам основного

М накопителя, вторые-к выходу первого дополнительного накопителя, первый выход второго дополнительного накопителя соединен со вторым входом схемы сравнения, о т л и ч а ю "

26 щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержитдешифратор кода заменяемого числа, один вход которого aogключен ко второму выходу второго

2S дополнительного накопителя, другойк выходу схемы сравнения, а выходы соединены с третьими входами коммутаторов, выходы которых подключены ко входам блока выборки информации.

3О Источники информации, принятые во внимание при экспертизе

l. Патент США В .3748653, кл. 340173, опублик. 1973.

2. Патент Франции В 2312837, кл. G ll С ll/00, онублик..1977 (прототип).