Стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1i 11 828I7 Ъ

Ьовз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 07.06.79 (21) 2776248/24-07 с присоединением заявки № (23) Приоритет (43) Опубликовано 07.0581 Бюллстс. ь Л 17 (45) Дата опубликования описания 07.05.8! (51) М K

G 05F 1,/56

Государственный комитет (53) УДК 621.316.722. .1(088.8) по делам изобретений и открытий

r p фф 5 с, а(я,> ъ ó

1 (72) Автор изобретения

А. В. Плошинский (71) Заявитель (54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

Изобретение относится к области электротехники и может быть использовано для стабилизации постоянного напряжения в источниках электропитания различных радиоэлектронных устройств.

Известны стабилизаторы постоянного напряжения с регулирующим транзистором и цепью обратной связи, состоящей из дифференциального усилителя постоянного тока, одним входом соединенного с источником опорного напряжения, а другим входом — с выходом резистивного делителя напряжения, включенного параллельно выходу стабилизатора (1).

Наличие указанных делителей напряже- 15 ния снижает коэффициент стабилизации, так как не все изменение выходного напряжения подается на вход усилителя постоянного тока, и затрудняет стабилизацию низких напря>кений. К тому же питание усили- 20 теля постоянного тока осуществляется от дополнительных стабилизированных источников для уменьшения пульсаций выходного напряжения.

Известен также стабилизатор постоянно- 25 го напряжения (2), который по совокупности существенных признаков наиболее близок предлагаемому.

Стабилизатор содержит включенный в

Одну из силовых шин регулирующий тран- 30 зистор и цепь обратной связи, состоящую из дифференциального усилителя постоянного тока, один вход которого соединен с выходом источника опорного напряжения на стаоилитроне, второй вход — с делителем напряжения, включенным параллельно выходным зажимам стабилизатора, а выходной каскад нагружен на высокоомное управляемое сопротивление, выполненное на полевом транзисторе и токозадающем резисторе, к точке соединения которых подключен управляющий электрод регулирующего транзистора. Стабилизатор представляет собой систему автоматического регулирования компенсационного типа, в которой сигнал, пропорциональный разности выходного напряжения и опорного напря>кения, подается на вход регулирующего транзистора через усилитель отрицательной обратной связи. Введение управляемого высокоомного сопротивления позволяет застабилизировать ток выходного каскада усилителя и снизить влияние изменения входного напряжения питающей сети на выходное напряжение стабилизатора, что очень важно при питании от нестабилизированного пульсирующего выпрямителя, а также повысить коэффициент стабилизации, так как высокоомное управляемое сопротивление значительно превышает входное

828179 сопротивление регулирующего транзистора и не оказывает на него шунтирующего воздействия, Однако в известном стабилизаторе лишь частично снижены пульсации выходного напряжения и повышен коэффициент стабилизации. Во-первых, через управляемое сопротивление запитан только выходной каскад усилителя, а цепи питания усилителя и опорный стабилитрон остаются незащищенными от проникновения пульсаций входного напряжения, во-вторых, наличие управляющего падения напряжения на токозадаюшем резисторе управляемого сопротивления требует гасящего делителя на входе дифференциального усилителя, снижающего коэффициент стабилизации и затрудняющего стабилизацию низкого напряжения. По этим же причинам применение высококачественного дифференциального усилителя постоянного тока в интегральном исполнении для данной схемы снизит надежность стабилизатора и не позволит получить достаточно высокий коэффициент стабилизации.

Целью изобретения является повышение коэффициента стабилизации и надежности, уменьшение пульсаций выходного напряжения и обеспечение стабилизации низких напряжений.

Эта цель достигается тем, что стабилизатор постоянного напряжения, содержащий включенный в одну из силовых шин регулирующий транзистор, управляющий электрод которого подключен к выходу цепи обратной связи, состоящей из дифференциального усилителя постоянного тока, одним входом соединенного с выходом источника опорного напряжения на стабилитроне, и управляемое сопротивление на полевом транзисторе, который стоком подключен к коллектору регулирующего транзистора и входному зажиму стабилизатора, а затвором — к токозадающему резистору, снабжен дополнительным транзистором, коллектор которого соединен со стоком, база — с истоком полевого транзистора, а эмиттер — с токозадающим резистором.

При этом второй вход дифференциального усилителя подключен непосредственно к выходному зажиму стабилизатора, опорный стабилитрон включен между затвором полевого транзистора и общей шиной стабилизатора, а питающие выводы усилителя подключены соответственно к общей шине стабилизатора и точке соединения эмиттера дополнительного транзистора с токозадающим резистором.

Это позволяет поддерживать постоянной величину тока опорного стабилитрона, подвести стабилизированное питающее напряжение к усилителю и использовать все выходное напряжение стабилизатора для управления дифференциальным усилителем постоянного тока.

5 о

15 ю

55 ю

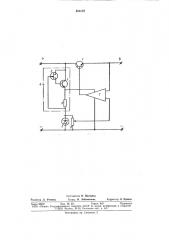

На чертеже представлена схема предла. гаемого стабилизатора.

Стабилизатор содержит включенный в одну из силовых шин регулирующий транзистор 1, управляющий электрод которого подключен к выходу цепи обратной связи, состоящей из дифференциального усилителя постоянного тока 2, одним входом соединенного с выходом источника опорного напряжения на стабилитроне 3, управляемое сопротивление 4, полевой транзистор 5, который стоком подключен к коллектору транзистора 1 и входному зажиму стабилизатора, а затвором — к токозадающему резистору 6, транзистор 7, коллектор которого соединен со стоком, база — с истоком полевого транзистора 5, а эмиттер с токозадающим резистором 6. Второй вход усилителя 2 подключен непосредственно к выходному зажиму стабилизатора, стабилитрон 3 включен между затвором транзистора 5 и общей шиной стабилизатора, а питающие выводы усилителя 2 подключены соответственно к общей шине стабилизатора и точке соединения эмиттера транзистора

3 может быть включен делитель напряжения 8, выходом соединенный с одним входо м ус ил ител я 2.

Стабилизатор постоянного напряжения работает следующим образом.

На управляющий электрод транзистора 1 с выхода усилителя 2 поступает сигнал, пропорциональный разности напряжений на

его входах, т. е. выходного напряжения стабилизатора и опорного напряжения, снимаемого со стабилитрона 3 (через установочный делитель 8) . Через силовой переход транзистора 1 протекает ток источника питающей сети, создающий напряжение на нагрузке стабилизатора, которое уравновешивает управляющую разность напряжений на входах усилителя 2. Таким образом, предлагаемый стабилизатор представляет собой систему автоматического регулирования компенсационного типа, в которой поддерживается постоянным выходное напряжение независимо от изменения входного напряжения и сопротивления нагрузки. Падение напряжения на резисторе 6 сопротивления 4 является автоматическим смещением, поступающим на затвор транзистора 5 и оказывающим отрицательную обратную связь на коллекторный ток транзистора 7.

Поэтому напряжение на токозадающем резисторе поддерживается постоянным, а следовательно, неизменен и ток, определяемый величиной этого резистора и протекающий через опорный стабилизатор 3, на напряжение стабилизации которого не влияют пульсации входного источника питания сети. Питание усилителя 2 осуществляется стабилизированным напряжением, поступающим с выхода эмиттерного повторителя на транзисторе 7, и равным сумме напряжений опорного стабилизатора 3 и падения напряже828179 ния йа резисторе 6. Транзистор 7 предназначен для согласования высокого выходного сопротивления транзистора 5 в режиме автоматического смещения с достаточно низким сопротивлениями по питанию усилителя 2 и стабилитрона 3. Подключение управляющего электрода транзистора 1 к выходу усилителя 2 позволяет подключить один из входов его непосредственно к выходному зажиму стабилизатора без гасящего делителя и улучшить режим работы усилителя

2, так как разность выходного и входного напряжений усилителя 2 оказывается равной небольшому напряжению управляющего перехода транзистора 1 (0,2 — 0,7 В), а также использовать все изменение выходного напряжения стабилизатора для управления усилителем 2. В совокупности стабилизация тока опорного стабилитрона и питающего напряжения усилителя 2, один из входов которого подключен непосредственно к выходному зажиму стабилизатора, повышают коэффициент стабилизации и надежность стабилизатора, уменьшают пульсации выходного напряжения и обеспечивают стабилизацию низких напряжений.

В предлагаемом стабилизаторе может быть применен операционный дифференциальный усилитель постоянного тока, выполненный на современной интегральной микросхеме, что значительно расширяетобласть применения стабилизатора. Величина выходного напряжения стабилизатора может регулироваться установочным делителем 8.

Таким образом, предлагаемый стабилизатор постоянного напряжения позволяет повысить коэффициент стабилизации и надежность, уменьшить пульсации выходного напряжения и обеспечить стабилизацию низких напряжений.

При применении в схеме стабилизатора регулирующего транзистора типа КТ602Б, дифференциальных усилителей постоянного тока К140УД1А и К153УД1А, опорных стабилитронов соответственно Д814А и трех последовательно соединенных стабилитрона

Д818Б, полевого транзистора КПЗОЗД и транзистора КТ201Б были получены следующие параметры стабилизаторов. Для усилителя обратной связи на микросхеме

Зо

К140УД1А в стабилизаторе пульсации выходного напряжения составили менее 1 мВ, а величина выходного напряжения регулировалась от 3,6 В до 9 В. Для стабилизатора с усилителем К15ЗУД1А пульсации— менее 0,1 мВ, а выходное напряжение—

8 — "2 B. Ток нагрузки в обоих случаях задавался 50 мА, а пульсации входного напряжения устанавливались пе менее 1 В.

Формула изобретения

Стабилизатор постоянного напряжения, содержащий включенный в одну из силовых шин регулирующий транзистор, управляю= щий электрод которого подключен к выходу цепи обратной связи, состоящей из дифференциального усилителя постоянного тока, одним входом соединенного с выходом источника опорного напряжения на стабилитроне, и управляемое сопротивление на полевом транзисторе, сток которого подключен к коллектору регулирующего транзистора и входному зажиму стабилизатора, а затвор — к токозадающему резистору, отличающийся тсм, что, с целью повышения коэффициента стабилизации и надежности, уменьшения пульсаций выходного напряжения и стабилизации низких напряжений, он снабжен дополнительным транзистором, коллектор которого соединен со стоком, база — с истоком полевого транзистора, а эмиттер — с токозадающим резистором, при этом второй вход дифференциального усилителя подключен непосредственно к выходному зажиму стабилизатора, опорный стабилитрон включен между затвором полевого транзистора и общей шиной стабилизатора, а питающие выводы усилителя подключены соответственно к общей шине стабилизатора н точке соединения эмиттера дополнительного транзистора с токозадающим резистором управляемого сопротивления.

Источники информации, принятые во внимание при экспертизе

1. Додик С. Д., Гальперин Е. И. Источники электропитания на полупроводниковых приборах. М., «Сов. радио», 1969.

2. Акцентованная заявка ФРГ № 1588838, G 05F 1/56, 1973 (прототип).

828179

Составитель В. Полякова

Техред И. Заболотиова

Корректор Л. Орлова

Редактор Л. Утехина

Типография, пр. Сапунова, 2

Заказ 909/9 Изд. № 321 Тираж 940 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5