Устройство допускового контролячастоты

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ТИЛЬСТВУ

Союз Сеаетскик

Сециалнстичесаии

Республик (61) Дополнительное к авт. сеид-ву (22) Заявлено 050779 (23) 2790943/ 18-21 с присоединением заявки N9 (23) Приоритет

Опубликовано 150581. бюллетень М 18

Дата опубликования описания 150 у1

<51) М. Кл.з

G 01 R 23/00

ГесудваственныФ квинтет

СССР

IIo дФдйи н306Рвтвння. н вткрытня (53) 621 317 72 (088.8) (72) Авторы изобретения

В.Г. Киясов, Н.Г. Руфина и В.A. Юдин. (7т) Заявитель (54) УСТРОИСТВО ДОПУСКОВОГО КОНТРОЛЯ ЧАСТОТЫ

Изобретение относится к автоматическому контролю и может быть использовано для контроля устройств, выдающих последовательность импульсов и требующих йепрерывного контроля в процессе своей работы.

Известно устройство допускового контроля частоты, содержащее счетчйк импульсов, входы которого соединены с выходами первого и второго ключей; триггер, вход которого соединен с выходом счетчика, а первый выход триггера — с выходом второго ключа, два блока сравнения, выходы которых соединены с входами логического блока, блок усреднения, вход которого соединен со вторым выходом триггера и входом первого ключа, а выход — с входами блоков сравнения, и датчик времени, соединенный с логическим блоком (11.

Однако устройства не позволяют контролировать допусковое отклонение частоты в автоматическом режиме и .не, обладает достаточным быстродействием.

Наиболее близким к предлагаемому является устройство, содержащее преобразователь контролируемой частоты, счетчики импульсов, триггер, элемент

И и регистратор (2).

Устройство характеризуется невысоким быстродействием при измерении средних и низких частот и невозможностью работы в автоматическом режиме.

Цель изобретения — повышение быстродействия устройства.

Эта цель достигается тем, что в устройство, содержащее последовательно соединенные триггер и элемент И, последовательно соединенные преобразователь контролируемой частоты и nep Iз вый счетчик, второй вход которого подключен к первому входу второго счетчика, второй вход последнего соединен с первым входом преобразователя контролируемой частоты, второй

20 вход которого подключен к второму выходу триггера, а выход элемента И соединен с первым входом регистратора, введены генератор опорной частоты, Формирователь импульсов, первый

25 дешифратор, элемент ИЛИ-НЕ, первый .элемент ИЛЙ и Последовательно сое. диненные второй дешифратор и второй ,элемент ИЛИ, второй вход которогО, подключен к первому выходу первого

ЗО дешифратора, первый вход последнего

830250

В случае отсутствия импульсон на входе триггера 1.(неисправность типа

5 отказ) импульсы, поступающие с гене ратора 4 опорной частоты на вход счетчика б импульсов переполняют счетчик и с дешифратора 8 через элемент 11 ИЛИ выдается сигнал на тре ð тий вход регистратора выхода частоты из заданного допуска,соответствующий сигналу Больше .

Такая структура предлагаемого устройства позволяет производить контроль частоты в автоматическом режиме без вспомогательных устройств и обладает большим быстродейстнием1 чем у известного устройства, а точность измерения повышается путем увеличения стабильности генератора опорной частоты.

Формула изобретения

ЗО

Контролируемый сигнал частоты f поступает на вход триггера 1.При при- 40 ходе первого импульса с прямого выхода триггера 1 сигнал поступает на преобразователь 2, разрешая прохождение импульсов с генератора 4 опорной частоты на, вход счетчика 5 им- 45 пульсов. С двоичных разрядов счетчика 5 импульсон текущее значение импульсов считывается в дешифратор 7, который вырабатывает сигналы Меньше, НоРма и Больше в дво- 5Q ичном коде. При приходе второго импульса на вход счетного триггера преобразователь закрывается и импульсы с генаратора опорной частоты перестают поступать на вход счетчика импульсов, а формирователь 3 импульсов формирует импульс, который через элемент 16 ИЛИ сбрасывает показания счетчиков импульсов, а с инверсного выхода триггера выдается сигнаЯ на элемент 9 И, разрешающий выход информации из дешифратора 7 в регистратор 12 выхода частоты из заданного допуска на входы регистратора ,соответствующие сигналам Меньше, Норма и Больше .

65 соединен с первым входом первого элемента ИЛИ, второй вход которого под-" ключен к выходу формирователя импульсов, вход последнего соединен с выходом триггера, при этом выход генератора опорной частоты подключен к второму входу второго счетчика импульсов, выход первого элемента ИЛИ

Ьо@динен с первым входом второго счетчика импульсов, вторые входы первого дешифратора подключены к выходам первого счетчика импульсов, второй выход первого дешифратора соеди.нен с вторым входОм элемента И, выход которого подключен к первому входу элемента ИЛи-НЕ,, второй вход последнего соединен с выходом второго элемента ИЛИ и с вторым входом регистратора, третий вход которого подключен к выходу элемента HJIH-НЕ, а входы второго дешифратора соедине,ны с выходами второго счетчика импульсов.

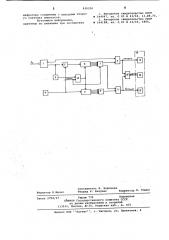

Яа чертеже изображена блок-схема устройства.

Устройство содержит триггер 1, преобразователь 2 KQHTpoJIHpyeMoA частоты, формирователь 3 импульсов, генератор 4 опорных импульсов, счетчики 5 и б импульсов, дешифраторы

7 и 8, элемент 9 И, элементы 10 .и

11 ИЛИ, регистратор 12 выхода частоты из заданного допуска, в состав которого входят индикаторы, 13-15, эле.мент 16 ИЛИ.

Устройство работает следующим об,разом.

По приходу третьего импульса на вход триггера 1 цикл понторяется

l и т.д.

Устройство допусконого контроля частоты, содержащее последовательно соединенные триггер и элемент И, последовательно соединенные преобразователь контролируемой частоты и .первый счетчик, второй вход которого подключен к первому входу второго счетчика, второй вход последнего соединен с первым входом преобразователя контролируемой частоты, второй вход которого подключен к второму выходу триггера, а выход элемента И соединен с перным входом регистратора, о т л и ч а ю щ е е с я тем, что, с целью. повышения быстродействия, н него внедены генератор опорной частоты, формирователь импульсов, первый дешифратор, элемент ИЛИ-НЕ, первый элемент .ИЛИ и последовательно соединенные второй дешифратор и второй элемент ИЛИ, второй вход которого подключен к первому выходу первого дешифратора, первый вход последнего соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу формирователя импульсов, вход последнего соединен с выходом триггера, при этом выход генератора опорной частоты подключен к второму входу счетчика -импульсов, йыход первого элемента,ИЛИ соединен с первым входом второго счетчика импульсов, вторые входы первого дешиф ратора подключены к выходам первого счетчика импульсов, второй выход первого дешифратора соединен с вторым входом элемента И, выход которого подключен к первому входу элемента

ИЛИ-НЕ, второй вход последнего соединен с выходом второго элемента ИЛИ и с вторым входом регистратора, третий вход которого подключен к выходу элемента ИЛИ-НЕ, а входы нторого де830250

Составитель Л. Воронина

Техред Н. Келушак Корректор Е. Рошко с

Редактор Н. Минко

Заказ 2794/27 . Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР. по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 шифратора соединены с выходами второго счетчика импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 544947, кл. G 05 В 23/02, 13.08.73, 2. Авторское свидетельство СССР

9 194188, кл. G 01 R 23/10, 19б5.