Микропрограммное устройствоуправления

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапистическик

Республик

<1ц8 30382

-Ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 110679 (21) 2778126/18-24 с присоединением заявки Но (23) Приоритет

Опубликовано 150581,Бюллетень N9 18

Дата опубликования описания 15,05.81 (5!)м. клз

G 06.F 9/22

Государственный комитет

СССР ио делам изобретений.и открытий (53) УДК 681. 326. .3(088.8) {72) Авторы изобретения

Ю.Я. Берсон, В.А. Киэуб, Н.П. Седов и В.И. Шагулин

Д4

t (71) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике, в частности к проектированию процессоров с микропрограммным управлением. 5

Известно устройство микропрограммного управления, содержащее память микрокоманд с адресным регистром, блок регистров и регистр микрокоманд, связанный с операционным бло- 10 ком, который соединен с блоком регистров и регистром признака результата Ц.

Недостаток этого устройства заключается в том, что установка признака результата требует выполнения отдельной микропрограммной процедуры, что снижает его быстродействие.

Наиболее близким по технической сущности к предлагаемому является 2Р микропрограммное устройство, содержащее блок регистров, адресный регистр, блок памяти микрокоманд, регистр микрокоманд; блок операций,, регистр признака результата, дешиф- 25 ратор 2 .

Недостаток данного устройства— невысокое быстродействие, обусловленное привязкой времени установки признака результата в регистр реэуль- 3Р тата к последней микрокоманде микропрограммы.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса микрокоманд, операционный блок, регистр микрокоманд, блок регистров, информационный выход регистра адреса микрокоманд соединен с адресным входом блока памяти микрокоманд, информационный выход которого соединен с информационным входом регистра микрэкоманд, адресный выход которого соединен с информационным входом регистра адреса микрокоманд, выход ветвления и первый выход микроопераций соединен соответственно с первым и вторым входами операционного блока, третий вход и первый выход которого соединены с первым выходом и первым входом блока регистров, введены регистр промежуточных результатов, и блок памяти признака результата и дополнительный блок памяти, вход которого соединен с вторым выходом микроопераций ре830382 гистра микрокоманд, управляющий вход соединен с выходом блока памяти признака результата и четвертым входом блока операций, второй выход которого соединен с информационным входом регистра промежуточных ре- 5 зультатов, информационный выход которого соединен с первым входом блока памяти признака результата, второй вход которого соединен с третьим выходом микроопераций регистра микрокоманд, четвертый выход микроопера- ций которого соединен с управляющим входом регистра промежуточных результатов, информационный выход дополнительного блока памяти соединен с пятым входом операционного блока. 15

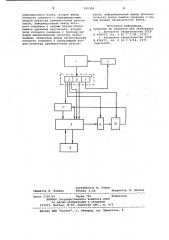

На чертеже представлена функциональная схема микропрограммного устройства управления.

Схема устройства состоит иэ блока

1 памяти микрокоманд, регистра 2 2О адреса микрокоманд, операционного блока 3, регистра 4 микрокоманд с полями: микроопераций 5, ветвления

6, адресными 7, блока 8 регистров, регистра 9 промежуточных реэульта- 25 тов, блока 10 памяти признака результата, дополнительного блока 11 формирования памяти.

Устройство работает следующим образом.

Код адреса текущей микрокоманды передается из поля 7 регистра 4 микрокоманд в регистр 2 адреса микрокоманд. По выбранному адресу иэ блока 1 памяти микрокоманд выбирается микрокоманда в регистр 4 микрокоманд. Информация в поле 6 ветвления регистра 4 микрокоманд передается в операционный блок 3 для органиэации ветвления микрокоманд. Поле 5 микроопераций регистра 4 микрокоманд 40 определяет тип микрооперации и управляет блоком 3 операций, регистром 9 промежуточных операций, блоком

10 и блоком 11. В одном иэ разрядов поля 5 микроопераций регистра 4 микрокоманд записывается признак приема промежуточной информации, необходимой для выработки признака результата, в регистр 9 промежуточных результатов из блока 3 операций. Блок

10 вырабатывает признак результата и передает его в операционный блок

3 в зависимости от значения управляющего блоком 10 разряда поля 5 микроопераций регистра 4 микрокоманд.

Таким образом, признак результата можно сформировать в любой момент микропрограммы после получения результата операции. Выбирать следующие команды можно непосредственно после получения результата операции. 6О

При выполнении команд условного перехода анализ условия и определение адреса следующей команды можно производить, не дожидаясь последней микрокс манды микропрограммы, с кото- Я рой совмещается команда условного перехода. В результате сокращаются потери времени при выполнении операций условного перехода.

При выполнении длинных команд типа умножения или деления управляющая информация в поле 5 микроопераций регистра 4 микрокоманд подается в блок 11, на выходы которого коды микроопераций выбираются в зависимости от значения промежуточных признаков результата, сформированных блоком 10, и передаются в операционный блок 3. Таким образом, с помощью нескольких микрокоманд обеспечивается выполнение и многоцифровых операций типа умножения и деления.

Введение дополнительного блока памяти позволяет в поле 5 микроопераций регистра 4 микрокоманд записывать не код микрооперации, а адрес микрооперации, записанной в дополнительном блоке памяти.

Таким образом, устройство позволяет формировать признак результата в любой микрокоманде микропрограммы после получения результата, а не в конце микропрограммы, что делает микропрограммирование более гибким, позволяет осуществлять совмещение выполнения команд, а также уменьшение времени выполнения длинных операций типа умножения т.е. данное техническое решение обеспечивает повышение быстродействия микропрограммного устройства управления.

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса микрокоманд, операционный блок, регистр микрокоманд, блок регистров, информационный выход регистра адреса микрокоманд соединен с адресным входом блока памяти микрокоманд, информацион-. ный выход которого соединен с информационным входом регистра микрокоманд адресный выход которого соеди1 нен с информационным входом регистра адреса микрокоманд, выход ветвления и первый выход микроопераций соединены с первым и вторым входами операционного блока соответственно, третий вход и первый выход которого соединены соответственно с первым выходом и первым входом блока регистров, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены регистр промежуточных результатов, блок памяти признака результатов и дополнительный блок памяти, адресный вход которого соединен со вторым выходом микроопераций регистра микрокоманд, управляющий вход — с выходом блока памяти признака результата и четвертым входом

830382

Составитель В. Усков

Техред A.Ач Корректор N. Демчик

Редактор Л. Повхан

Заказ 3350/55 Тираж 745 Подписное

BHEMGH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 операционного блока, второй выход которого соединен с информационным входом регистра промежуточных результатов, информационный выход которого соединен с первым входом блока памяти признака результата, второй вход которого соединен с третьим выходом микроопераций регистра микрокоманд, четвертый выход микроопераций которого соединен с управляющим входом регистра промежуточных результатов, информационный выход дополнительного блока памяти соединен с пятым входом операционного блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 648979, кл. G 06 F 7/38, 1976.

2, Авторское свидетельство СССР

9 456271, кл. G 06 F 9/14, 1975 (прототип).