Перестраиваемое микропрограммноеустройство управления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ («)830383

К АВТОРСКОМУ СВИДЕТИЛЬСТВУ (61) Дополнительное к авт. свид-ву р1)м. к .з (22) Заявлено 130679 (21) 2778839/18-24 с присоединением заявки Йо (23) Приоритет

ОпубликОваио 15.0581.бюллетень Н9 18

Дата опубликования описания 1505.81

G 06 F 9/22

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 681 З25

- (088.8) (72) Автор изобретения

Д.В. Полонский (71) Заявитель (54) ПЕРЕСТРАИВАЕМОЕ МИКРОПРОГРАММНОЕ

УСТРОЙСТВО УПРАВЛЕНИЯ

30

Изобретение относится к вычислительной технике и может быть исполь. зовано в устройствах управления цифровых вычислительчых машин. 5

Известно микропрограммное устройство управления, содержащее триггеры, коммутаторы, схемы И, регист- ры адреса, запоминающие блокн 11).

Недостаток устройства заключа- 1р ется в том, что в случае отказа одного из запоминающих блоков невозможна перенастройка на работу другого запоминающего блока, что снижает надежность устройства. Наиболее близким по технйческой сущности к предлагаемому является перестраиваемое микропрограммное устройство управления, которое содержит два запоминающих 20 блока, два регистра адреса, два коммутатора, два триггера управления,два элемента И и элемент ИЛИ (2 ).

Недостатком. данного устройства является то, что в случае отказа одного из регистров адреса невозможна перенастройка на работу по программе обработки отказов либо по подпрограмме. решения задачи по усеченному алгоритму. Это снижает надежность устройства.

Цель изобретения — повышение на.дежности устройства.

Поставленная цель достигается тем, что в пересматриваемом микропрограммном устройстве управления, содержащем два запоминающих блока, два регистра адреса, два элемента

И, два коммутатора, два триггера управления и элемент ИЛИ, первые входы первого и второго коммутаторов соединены соответственно с нулевьваи выходами первого и второго триггеров управления, выходы и",рвого и второго коммутаторов соединены соответственно с первыми информационными входами первого и второго регистров адреса, информационные выходы которых соединены соответственно cадресными входами первого и второго запоминающих блоков, управляющие входы которых соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены соответственно с пер вым и вторым управляющими входами устройства l . co вторыми входами

830383

2О

65 второго и первого коммутаторов, вторые входы первого и второго элементов И соединены соответственно с единичными выходами второго и первого триггеров управления, счетные входы которых соединены соответственно с установочными входами второго и первого регистров адреса и с управляющими выходами первого и второго запоминающих блоков, операционные выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является операционным выходом устройства, адресные выходы первого и

Ф второго запоминающих блоков соединены соответственно с третьими входами второго и первого коммутаторов и с четвертыми входами первого и второго коммутаторов.

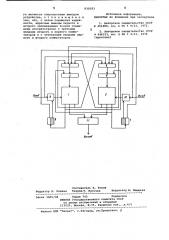

На чертеже представлена функциональная схема устройства.

Устройство содержит первый запоминающий блок 1, второй запоминающий блок 2, первый регистр 3 адреса, второй регистр 4 адреса, первый коммутатор 5, второй коммутатор 6, первый триггер 7 управления, второй триггер 8 управления, первый элемент И 9, второй элемент

И 10, элемент ИЛИ 11. (Устройство работает следующим образом.

Пусть в исходном состоянии первый триггер 7 управления и второй триггер 8 управления находятся в единичном состоянии и пусть на регистре 3 (4) адреса находится адрес микрокоманды, подлежащей считыванию. Так как триггеры 7 и

8 управления находятся в единичном состоянии, то они разрешают прохождения поступившего на вход тактового импульса через элементы И 9 (10) и обеспечивают прохождение на выход коммутатора 5 сигналов с запоминающего блока 2, а на выход коммутатора б сигналов с выхода за поминающего блока 1. На адресном выходе запоминающего блока 1 (2) появляется считанная микрокоманда, и адрес следующей микрокоманды через коммутатор б (5) поступает и регистр 4 (3) адреса. На выходе устройства микрооперации с операционных выходов запоминающих блоков появляются поочередно.

При отказе одного запоминающего блока, например 1, и (или) одного регистра адреса, например

4, происходит перестройка микропрограммного устройства, а именно: с управляющего выхода блока 1 на вход регистра 4 адреса подается сигнал, устанавливающий на этом регистре фиксированный адрес. С этого же выхода запоминающего блока 1 подается сигнал на счетн и вход триггера 8, который ус танавливает его в нулевое состоя- ние. При этом триггер закрывает элемент И 9, блокируя запуск запоминающего блока 1, и одновременно коммутатор б обеспечивает прохождение на вход регистра 4 адреqa сигнала с адресного выхода запоминающего блока 2. Адрес сле,дующей микрокоманды, считанный с выхода работающего запоминающего блока 2, поступает на вход коммутатора б, и далее в регистр адреса 4. По данному адресу запоминающий блок 2 выдает микрооперацию на элемент ИЛИ 11 и далее на выход устройства, а адрес следующей микрокоманды на коммутатор 6.

Таким образом, повышение надежности устройства достигается тем, что в случае .отказа одного из запоминающих блоков или регистра адреса, другой запоминающий блок перестраиваемого микропрограммного устройства продолжает работать и по фиксированному адресу устройство переходит на программу обработки отказов.

Формула и обретения

Перестраиваемое микропрограммное устройство управления, содержащее два запоминающих блока, два регистра адреса, два элемента И, два коммутатора, два триггера управления и элемент ИЛИ, первые входы первого и второго коммутаторов соединены соответственно с нулевыми выходами первого и второго триггеров управления, выходы первого и второго коммутаторов соединены соответственно с первыми информационными входами первого и второго регистров адреса, информационные выходы которых соединены соответственно с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены соответственно с выходами первого и второго элементов

И, первые входы которых соединены соответственно с первым и вторым управляющими входами устройства и со вторыми входами второго и первого коммутаторов, вторые входы первого и второго элементов И соединены соответственнос единичными выходами второго и первого триггеров управления, счетные входы которых соединены соответственно с установочными входами второго и первогс регистров адреса и с управляющими выходами первого и второго запоминающих блоков, операционные выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которо830383

Swxcrd

Составитель В. Усков

Редактор Л. Повхан Техред Т. Маточка Корректор Н. Швыдкая т

Заказ 3Q55/38 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д.4/5

Филиал ППП "Патент", r.Óæãoðoä, ул.Проектная, 4 го является операционным выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, адресные выходы первого и второго запоминакхцих блоков соеди,нены соответственно с третьими входами второго и первого коммутаторов и с четвертыми входами первого и второго коммутаторов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 451080, кл. G 06 F 9/12, 1972.

2. Авторское свидетельство. СССР

9 646333, кл. G F 9/12, 1976 (прототип)