Микропрограммное устройство управ-ления

Иллюстрации

Показать всеРеферат

Союз Сооеетскив

Социаанстичесних

Респубанк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

<11830384 ?? l (61) ???????????????????????????? ?? ??????. ????????-???? (51) x 3 (22) ???????????????? 1406.79 (21) 2785262>

Опубликовано 1505.8 1,бюллетень Н9 18

Дата опубликования описания 150581 G 06 F 9/22

Госуварствеииый комитет

СССР яо лелам изобретений н открытий (53) УДК 681. 325 (088. 8) (72) Авторы изобретения

А.Л.Хлюнев и A.A.Êóçíåöoâ (7! ) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОИСТВО УПРАВЛЕНИЯ

Из обретени е относится к вычислительной технике.

Известно микропрограммное устройство управления, содержащее триггеры, коммутаторы, элементы И, регистры адреса, запоминающие блоки (1).

Недостаток устройства — избыток оборудования, так как оно содержит два коммутатора и два регистра адреса.

Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее,два запоминающих блока, соединенных с соответствующи- 15 ми регистрами адреса, два блока.проверки условий, два триггера блокировки и два элемента И (2) .

Недостатком данного устройства является избыток оборудования, обус- 20 ловленный наличием двух блоков проверки, двух триггеров блокировки, двух регистров адреса, работающих поочередно.

Цель изобретения — упрощение устройства.

Цель достигается тем, что в устройство, содержащее запоминающие блоки, элементы И, триггер блокировки и регистр адреса, первый разрядный выход которого соединен с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены с выходами первого и второго Элементов И соответственно, первые входы которых соединены с первым управляющим входом устройства, первые выхо1вю первого и второго запоминающих блоков соединены с первым и вторым управляющими выходами устройства, введен блок проверки условий, выход которого соединен со входом триггера блокировки, выход триггера блокировки соединен со вторыми входами первого и второго элементов И, третий вход первого элемента И соединен со вторым разрядным выходом регистра адреса, третий вход второго элемента И соединен с третьим разрядным выходом регистра адреса, первый вход регистра адреса соединен со вторым выходом первого запомин ающе го бло ка, второй вход регистра адреса соединен со вторым выходом второго запоминающего блока, третьи выходы первого и второго запоминающих блоков соединены с первым и вторым входами блока проверки условий соответственно, третий вход ко830384 торого соединен со вторым управляющих входом устройства.

Кроме того, блок проверки условий содержит две схемы сравнения и элемент ИЛИ, причем гервые входы первой и второй схем сравнения соединены соответственнс с первым и вторым входами блока, вторые входы первой и второй схем сравнения соединены с третьим входом блока, выходы первой и второй схем сравнения соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с выходом блока.

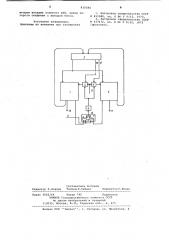

На чертеже приведена функциональная схема устройства.

Устройство содержит запоминающие 15 блоки 1 и 2,,регистр 3 адреса, элементы И 4 и 5, триггер б блокировки, блок 7 проверки условий, управляющие входы 8 и 9, управляющие выходы

10 и 11 единичный выход 12 триггера 2О младшего разряда регистра 3 адреса, нулевой выход 13 этого триггера, первая схема 14 сравнения, вторая схема

15 сравнения, элемент ИЛИ 1б.

Устройство работает слецуюшчм образом.

При поступлении тактового сигнала на управляющий вход 8 по адресу, находящемуся в регистре 3 адреса, происходит считывание микрокоманды из одного из запоминающих блоков 1 и 2.

Выбор запоминающего блока, из которого должна быть считана микрокоманда п роиэ водится следующим образ ом. При

У наличии 1, в младшем разряде регистра 3 адреса управляющий сигнал зч с выхода 12 открывает элемент И 4, при этом по тактовому сигналу со входа 8 производится считывание микрокоманды из запоминающего блока (т.е. из запоминающего блока 1 про- 40 изводится считывание микрокоманд с нечетными адресами).При наличии "0" в младшем разряде регистра адреса управляющий сигнал с выхода 13 открывает элемент И 5 и по тактовому сиг- 45 налу с управляющего входа 8 производится считывание микрокоманд из запоминающего блока 2 (т.е. из запоминающего блока 2 производится считывание микро .оманд с нечетными адресами). Считанная из запоминающего блока 1 или 2 микрокоманда реализует микрооперации на выходах 10 или 11 запоминающих блоков и устанавливает в регистре 3 адреса адрес следующей микрокоманды. В том случае, когда при выполнении некоторой микрокоманды, например считанной из запоминающего блока 2, устройство должно перейти в режим ожидания по условию, подаваемому на управляющий О вход 9, с соответствующего выхода запоминающего блока 2 на вход блока

7 проверки условий поступает сигнал адреса условия. Если условие ожидания подано на управляющий вход 9, то с выхода блока элементов, И-ИЛИ производится установка триггера блокировки б в единичное состояние. При этом сигнал с ьыхоца триггера б блокировки закрывает элементы И 4 и 5, тем самым запрешая поступление тактовых сигналов на входы запоминающих блоков 1 и 2. При снятии условия ожидания с управляющего входа 9, триггер б устанавливается в нулевое состояние, тем самым разблокируя эл менты И 4 и

5 и разрешая дальнейшую работу устройства по тактовым сигналам с управляющего входа 9. таким образом, устройство упрощается в связи с тем, что оно содержит один регистр адреса.

Формула изобретения

1. Микропрограммное устройство управления, содержащее запоминающие блоки, элементы И, триггер блокиоовки и регистр адреса, первый разрядный выход которого соединен с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены соответственно с выходами первого к второго элементов

И, первые входы которых соединены с первым управляющим входом устройства, первые выходы первого и второго запоминающих блоков соединены с первым и вторым упоавляющими выходами устройства, о т л и ч а ю щ е е с я тем,. что, с целью упрощения устройства, оно содержит блок проверки условий„ выход которого соединен со входом триггера блокировки„ выход триггера блокировки соединен со вторыми входами первого и второго элементов

И, третий вход первого элемента И соединен со вторым разрядным выходом регистра адреса, третий вход второго элемента И соединен с тре:ьим разрядным выходом регистра адр-.;са, первый вход регистра адреса соединен со вторым выходом первого запоминающего блока, второй вход регистра адреса соединен со вторым вы-.îäoì второго запоминающего блока, третьи выходы первого и второго запоминающих блоков соединены с первым и вторым входами блока проверки условий соответствен но, третий вход которого соединен со вторым управляющим входом устройства.

2. Устройство по и. 1, о т л и ч а ю щ e e сc я т еeмM, что блок проверки условий содержит две схемы сравнения и элемент ИЛИ, причем первые входы первой и второй схем сравнения соединены соответственно с первым и вторым входами блока, вторые входы первой и второй схем сравнения соединены с третьим входом блока, выходы первой H второй схем сравнения соединены соответственно с первым и

830384

Составитель В.усков

Редактор Л. Повхан Техред М. Рейвес Корректор О. Билак

Заказ 3502/64 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 вторым входами элемента ИЛИ, выход которого соединен с выходом блока.

Источники информации, принятые во внимание при экспертизе

1 ° Авторское

Р 451080, кл. G

2. Авторское

9 437072, кл. G (прототип). свидетельство СССР

06 F 9/12, 1973. свидетельство GÑÑÐ

06 F 9/12, 1973