Устройство для обработки цифровыхданных

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТВЛЬСТВУ

Союз Советски»

Социалистически»

Республик («) 830394 (61) Дополнительное к ввт. свид-ву(51)М. Кл. (22) Заявлено 1402,79 (21) 2750251/18-24 с присоединением Заявки Ио— (23) Приоритет

G 06 F 15/06

Госудврственный комитет

СССР ио делам изобретений и открытий

Опубликовано 150581.Бюллетень Ио 18 (53) УДК 68 1. 32 7. 17 (088. 8) Дата опубликования описания 15.05,81 (72) Авторы изобретения

И. В. Бурковский, Л.О. Беспалов и В. Г. ташков C

\ (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ

Изобретенце относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных машинах, в устройствах для отладки программ задач цифровых вычислительных управляющих систем.

Известны устройства для обработки цифровых данных, содержащие постоянные запоминающие устройства (ПЭУ} и полупостоянные запоминающие устройст ва (ППЗУ }, подключенные через блок приема и вывода к числовым шинам, распределитель, осуществляющий выбор информации из ПЗУ или ППЗУ в зависимости от текущего адреса и состояния регистров установки, причем по одним и тем же адресам информация может быть считана из ПЗУ или из ППЗУ (Q.

Недостатком этих устройств является низкая пропускная способность, так как отсутствует режим одновременного считывания информации из ПЗУ и

ППЗУ и формирования на ее основе новых кодовых комбинаций.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее постоянное запоминающее устройство, полупостоянное запомииающее устройство, регистр адреса, подключенный выходом ко входам 30 постоянного и полупостоянного запоминающихх устройств, вторые входы которых связаны с шиной опроса, регистр базового адреса, подклаченный выходом к третьему входу постоянного запоминающего устройства, выход которого и выход полупостоянного запоминающего устройства подключены к соответствующим входам регистра (2).

Недостатком данного устройства является низкая пропускная способность, что обусловлено отсутствием средств формирования на выходе устрсйства кодовых комбинаций на основе информации, одновременно считанной из постоянного и полупостоянного запоминающих устройст в.

Обычно в вычислительных машинах

ППЗУ используется для хранения инфор" мации, которая может либо формироваться автоматически в процессе ре" щения какой-либо задачи, либо записывается оператором для использования в течении заданного времени.

Эта информация не имеет самостоятельного значения и дополняет основную, которая хранится à ПЗУ. Этим достигается, например, сокращение общего объема и оптимизация программ, фиксируемых в ПЗУ. Однако укаэанное

830394 свойство устройства не позволяет

Формировать кодовые комбинации на основе информации, считанной одновре менно из ПЗУ и ППЗУ, что значительно повышает эффективность использования ППЗУ при повышении пропускчай способности устройства. Например, в команде перехода, хранящейся в ПЗУ, может быть заменен адрес перехода, если эта часть команды приформировывается из ППЗУ, в другом случае в команде может быть заменен

10 код операции, либо признаки ее модификации.

Цель изобретения — повышение пропускной способности устройства, Поставленная цель достигается твм, что в устройство, содержащее блок постоянной памяти, соединенный первым входаМ с выходом регистра адреса и первым входом блока полупостоянной памяти, вторым входом — со вто- Д рым входом блока палупостояннай памяти и входной шиной опроса, а третий вход - с выходом регистра базового адреса, введены блок анализа кодов . блок анализа признаков, причем первая группа информационных входов блока анализа кодов соединена с груп- " пой выходов блока постоянной памяти, вторая группа информационных входов с группой выходов информационных разрядов блока палупостояннай памяти, а группа управляющих входов с соответствующими выходами блока анализа признаков, первый, второй и третий входы которого подключены соответственно к первому и второму выходам дополнительных разрядов бло-, ка полупостоянной памяти и выходу регистра базового адреса, выходы блока анализа кодов являются соответствующими выходными кодовыми ши- 4Q нами устройства,.а также тем, что блок анализа кодов содержит первую и вторую группы элементов И, группу элементов ИЛИ, выходы которых являются соответствующими выходами блока, и группу элементов НЕ, входы которых являются соответствующими управляющими входами блок Ь, первый входы элементов И первой группы подключены к соответствующим входам первой группы информационных входов блока, а вторые входы - ко входам соответствующих элементов НЕ, группы первые входы элементов И второй группы соединены с соответствующими входами второй группы информационных. входов блока, а вторые входы — с,выходами соответствующих элементов НБ группы, первые входы элементов ИЛИ группы соединены с выходами соответствующих элементов И первой группы, Щ а вторые входы — с выходами соответствукщих элементов И второй группы, а также тем, что блок анализа признаков содержит два регистра, входы которых являются соответственно я первым и вторым входами блока, схему сравнения, первый вход которой подключен к выходу второго регистра, второй вход - к третьему входу блока, а выход — через элементы HE— к первым входам элементов ИЛИ группы, выходы которых являются соответствую. щими выходами блока, а вторые входы подключены к выходам соответствукщих элементов И групПы, первыми. входами соединенных с выходами соответствующих разрядов первого регистра, а вторыми входами — с выходом схемы сравнения.

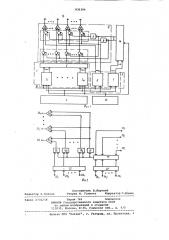

На фиг. 1 представлена блок-схема устройства; на фиг, " — функциональная схема .блока анализа признаков.

Устройство садер>кит блок 1 постоянной памяти, состоящий из N модулей 2 постоянной памяти и группы элементов 3 ИЛИ, регистр 4 адреса, блок 5 палупостояннай памяти, состоящий из модулей 6 и 7, блока 8 Формирования кодов, состоящего из элементов 9 НЕ группы, элементов 10 ИЛИ группы, элементов 11 И первой группы и элементов 12 И второй группы, выходные кодовые шины 13 устройства, блок 14 анализа признаков, регистр

15 базового адреса и входную шину

16 опроса. Блок 14 анализа признаков включает схему 17 сравнения, элементы 18 И группы, элементы 19 ИЛИ группы, выходы 20 блока, элемент 21

НЕ, первый 22 и второй 23 регистры, второй 24, третий 25 и первый 26 входы блока.

Устройство работает следующим образ ом.

По коду в регистре 15 выбирается один из модулей 2 блока 1 настоянной памяти, а па коду в регистре 4 при появлении сигнала на шине 1б производят считывание информаций из выбранных модулей 2,б и 7, причем из модуля б — информационные разряды, а из модуля 7 — разряды управляющих признаков. Информация, считанная из модуля 7, расшифровывается в блоке 14, который, в первую очередь, прои зводит сравнение кода управляющих признаков на входах 24 с содержимым регистра 15, поступающим по входам 25. Если код текущего базового адреса на входах 25 не совпадает с кодом управляющих признаков на входах 24, то с элемента 21

НЕ на элементы 19 ИЛИ и выходы 20 блока на входы элементов 12 И выдается запрещающий сигнал, а на управлякщив входы элементов 11 И вЂ” разрешающий сигнал. Информация, считанная с одного из модулей 1, проходит через элементы 3 ИЛИ, 11И и 10 ИЛИ на выходные шины 13, а информация, считанная из модуля б, блокируется на элементах 12 И, в результате информация

830394 на ныходах 13 точно соответствует информации, считанной из блока 1.

Если же коды на входах 24 и 25 совпадают,. то в блоке 14 через элементы 18 И формируется сигнал запрета определенных элементов 11 И. С помо- l щью этого же сигнала, инвертированного на элементе 9 НЕ, открываются одноименные элементы 12 И. В резулвтате этого на выходных шинах 13 формируется кодовая комбинация, состав- ленная из информации, считанной из модулей 2 и 6, Таким образом, информация, записанная в модуле 7, указывает номера. модулей блока 1 постоянной памяти, а также адреса, при обращении к которым группа разрядов, также указанная в модуле 7, будет замаскирована и заменена группой разрядов, считанных из модуля 6, Таким образом, устройство обеспечивает повышение пропускной способ- 20 ности и повышает эффективность использования запоминающих устройств.

По сравнению с известными устройствами для обработки цифровых данных предлагаемое позволяет сократить емкость ППЗУ, что снижает общую стоимость оборудования.

Формула изобретения

1..устройство для обработки цифровых данных, содержащее. блок постояНной памяти, соединенный первым входом и с выходом регистра адреса и первым входом блока полупОстоянной памяти, вторым входОм — со вторым входом блока полупостоянной памяти и входной шиной опроса, а третий входс выходом регистра базового адреса, о т л и ч а ю щ е е с я тем, что, 40 с целью повышения пропускной способности устройства, в него введены блок анализа кодов и блок анализа признаков, причем первая группа информационных входов блока анализа 45 кодон соединена с Группой выходов блока постоянной памятй, вторая группа информационных входов - с группой выходов информационных разрядов, блока полупостоянной памяти, а группа уп-. равляющих входов — с соответствующи-. ми выходами блока анализа признаков, первый, второй и третий входы которого подключены соответственно к первому и второму выходам дополнительных разрядов блока полупостоянной памяти и выходу регистра базового адреса, выходы блока анализа кодов являются соответствующими выходными кодовыми шинами устройства.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок анализа кодов содержит первую и вторую группы элементов И, группу элементов ИЛИ, выходы которых являются соответствующими выходами блока, и группу элементов НЕ, входы которых являются соответствукщими,управляющими входами блока, первые входы элементов И. первой группы подключены соответственно к входам первбй группы информационных входов блока, а вторые входы — ко входам соответстнующих элементов НЕ группы, первые входы элементов И второй группы соединены соответственно со второй группой информационных входов блока, а вторые входы. — с выходами соответствующих элементов НЕ группы, первые входы элементов ИЛИ группы соединены с выходами соответствующих элементов И первой группы, а вторые вхоцы— с выходами соответствующих элементов И второй группы.

3. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок анализа признаков содержит дна регистра, входы которых являются соответственно первым и вторым входами блока, схему сравнения, первый вход которой подключен к выходу второго регистра, второй нход - к третьему входу блока, а выход через элементы

HE - к первым входам элементов ИЛИ группы, выходы которых являются соответствующими выходами блока, а вторые входы — подключены к выходам соответствующих элементов И группы, первыми входами соединенных с выходами соответствующих разрядов первого регистра, а вторыми нходами — с выходом схемы сравнения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 489107, кл G 06 F 11/00, 1973.

2. Авторское свидетельство СССР по заявке Р 2412295/18-24; кл. G 06 ьГ 15/06, 1976 (прототип).

830394 гп, Рог.2

Составитель В. Вертлиб

Техред М. Голинка Корректор C,Ùoìàê

Редактор Л.Повхан

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж"35, Раушская наб., д. 4/5

Заказ 2732/18

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4