Устройство для определения дисперсии

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<111830397

gO,.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополннтельное к авт. свид-ву (22) Заявлено 060479 (21) 2749372/18-24 с присоединением заявки Йо— (23) Приоритет

Опубликовано 15.05.8L Бюллетень Н9 18 (51)М. Кл.з

G 06 Г 15/Зб

Государственный «омнтет

СССР оо делам мэобретемнй м открытмй (53) УДК 681, 3 (088. 8) Дата опубликования описанмя 1505.81 (72) Автор изобретения

С. С. Кукушкин (71) Заявитель (54) УСтрОИстао для опредЕЛЕния ДИСПерСии

ИэобрЕтение относится к автоматике и вычислительной технике и может быть использовано для оперативной обработки быстроменяющихся случайных процессов.

Известно устройство для измерения дисперсии, содержащее. блок вычитания, первый вход которого непосредственно, а второй через элемент задержки подключен к первому входу устройства, накапливающий сумматор, кващ»атор (1).

Наиболее .близким по техническому решению к предлагаемому является устройство для определения диспер- сии, содержащее (Ф-1) последовательно соединенных блоков вычитания, между первым и вторым входами каждого из которых подключен элемент задержки, блок определения абсолютной разности, между первым и вторым входами которого подключен элемент задержки, первый вход блока определений абсолютной разности соединен с выходом (3-1) -ro блока вычитания, первые входы блоков вычитания и блока определения абсолютной разности соединены через сдвоенный многопозиционный переключатель с первым входом устройства, блок умножения, к первому входу которого через сдвоенный многопозиционный переключатель подключены выходы блока памяти,квадратор и накапливающий сумматор.

Недостатком известных устройств является невозможность получения текущих (скользящих) оценок дисперсии и повышения на их основе качества сглаживания временной .функции оценок дисперсии.

Цель изобретения — повышение точности определения. Поставленная цель достигается тем, что в устройство для опреде. ления дисперсии, содержащее (Q-1) последовательно соединенных блоков вычитания, выход (Ф-1) -го блока вычитания подключен ко входу блока определения абсолютной разности, сдвоенный многопозиционный переключатель, первый подвижный контакт которого соединен с первым входом устройства, первая группа неподвиж ных контактов сдвоенного многопоэиционного переключателя соединена со входами (к-1) блоков вычитания, со входом блока определения абсолютной разности и со входами элеменЗО тов задержки, выходы элементов

830397

3Î

5Î

60 эадержк и подключены к соот вет ст вующим входам (k-1) блоков вычитания и блока определения абсолютной разности, блок умножения, первый, вход которого соединен со вторым подвижным контактом сдвоенного многогоэиционного переключателя, вторая группа неподвижных контактов которого соединена с выходами блока памяти, и квадратор, введены два дополнительных блока памяти, (1(+1) элемент задержки, Ъ -тый блок вычитания, элемент запрета, элемент И, реверсивный счетчик, при этом вход перво-о дополнительного блока памяти объединен с первыми входами элемента запрета, элемента И и подключен к выходу (+1) -го элемента задержки, вход которого объединен со входом второго дополнительного блока памяти, со вторым входом элемента запрета и соединен с выходом блока определения абсолютной разности, выход элемента . запрета через сумматор под» ключен ко второму входу элемента И, выход которого объединен с первым выходом 1(-го блока вычитания и подключен к первому входу реверсивного счетчика, второй вход которого соединен со вторым выходом к -го блока вычитания, первый и второй входы которого подключены соответственно к выходам первого и второго дополнительных блоков памяти, выход оеверсивного счетчика соединен со вторым входом блока умножения, выход которого подключен ко входу квадратора, выход которого является выходом устройства.

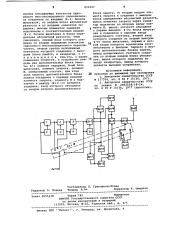

На чертеже приведена структурная схема устройства.

Схема устройства содержит блоки

1,3,5...,2 М-3 вычитания, блок

21-1 определения абсолютной разности, элементы 2, 4, б,...,2)(, 21+1 зад =ржки, элемент 2%+2 запрет, блок

2 +11 памяти, накапливающий сумматор 2%+5, элемент И 2М+б, реверсивный счетчик 23(+7, 1< ый блок 2%+8 вычитания, блок 2%+9 умножения, сдвоенный многопозиционный переключатель 21+10, первый и второй дополнительные блоки 24 +3 и 2 + 4 памяти, квадратор 21 +12.

Устройство работает следующим образом.

Последовательность случайных величин поступает на первый вход выбранного переключателем блока вычитания или блока определения абсолютной разности, где определяются разности (Q-1) -го порядка и абсолютные разности -го порядка между значениями исследуемого случайного процесса. Вычисленные первые N значений абсолютных разнос ей запоминаются в блоке 2к+3 памяти .и одновременно накапливаются

4 в накапливающем сумматоре 2 (+5.

Элемент 2Ъ+1 задержки в первые

N тактов определения абсолютных разностей закрыт, и в блок 2)(+4 памяти запишется (N+1)-ое и последующие значения. В блоке 2%+8 вычитания определяются разности между абсолютными значениями разностей, отстоящими друг от друга на И тактов (на время накопления статистической выборки). В зависимости от знака + или разности распределяются по соответствующим выходам блока 21(+8. Сигнал на выходе элемента 2((+1 задержки запрещает прохождение абсолютных разностей через элемент ЗАПРЕТ для накопления в сумматоре 2М+5 и одновременно открывает элемент И 2 +б, разрешая перезапись суммы абсолютных разностей в реверсивный счетчик 2%+7

Записанная в реверсивном счетчике

27+7 сумма корректируется подачей на вычитающие и суммирующие входы реверсивного счетчика разностей, вычисленных в блоке 2)(+8 вычитания и преобразованных в число-импульсный код. Абсолютные разности усредняются в реверсивном счетчике путем вывода чисе:л со старших разрядов счетчика.

Средние значения -,бсолютных разностей умножаются в блоке 2 К-+9 умножения на соответствующий порядку разности коэффициент пропорциональности, хранящийся в блоке 2%+11 памяти. Результаты вычислений на выходе блока умножения представляют собой оценки среднеквадратического отклонения значений случайного процесса. Последние, возведенные в квадрат в квадраторе 6, характеризуют дисперсию исследуемого случайного процесса. устройство выгодно отличается от известных устройств высоким качеством сглаживания последовательности определяемых оценок дисперсии, Используемая в устройстве рекуррентная процедура позволяет хранить наименьшее количество данных от предыдущих шагов вычислений. Дополнительным и весьма существенным с практической точки зрения преимуществом является готовность к выдаче результата на любом промежуточном шаге вычислений.

Формула изобретения

Устройство для определения дисперсии, содержащее (%-1) последовательно соединенных блоков вычитания, выход (4-1)-ro блока вычитания подключен ко -входу блока определения абсолютной разности, сдвоенный многопозиционный переключатель, первый подвижный контакт которого соединен с первым входом устройства, первая

830397

Составитель Л. Григорьян-Чтенц

Редактор Л. Повхан Техред А-Ач Корректор Н. Швыдкая

Заказ 3055/38 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35; Раушская наб., д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 группа неподвижных контактов сдвоенного многопозиционного переключателя соединена со входами (3-1) блоков .вычитания, со входом блока абсолютной разности и со входами элементов задержки, выходы элементов задержки 5 подключены к соответствующим. входам (Ъ-1) блоков вычитания и блока определения абсолютной разности, блок умножения, первый вход которого соединен со вторым подвижным контактом сдвоенного многопозиционного переключателя, вторая группа неподвижных контактов которого соединена с выходами блока памяти, и квадратор, о тл и ч а ю щ е е с я тем,что, с целью повышения точности, в устройство вве- 5 дены.два дополнительных блока памяти, +1 элемент задержки, Ф-ый блок вычитания, элемент запрета, элемент

И, реверсивный счетчик, при этом вход первого дополнительного блока 2О памяти объединен с первыми входами элемента запрета, элемента И и подключен к выходу (1+1)-го элемента задержки, вход которого объединен со входом второго дополнительного блока памяти, со вторым входом элемента запрета и соединен с выходом блока определения абсолютной разности, выход элемента запрета через сумматор подключен ко второму входу элемента И, выход;. которого объединен с первым выходом к-го блока вычитания и подключен к первому входу реверсивного счетчика, второй вход которого соединен оо вторым выходом

К-го блока вычитания, первый и второй входы которого подключены соответственно к выходам первого и второго дополнительных блоков памяти, выход реверсивного счетчика соединен со вторым входом блока умножения, выход которого подключен ко входу квадратора, выход которого является выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 377704, кл. 6 06 F 15/36, 1971.

2. Авторское свидетельство СССР по заявке 9 2462558/18-24, кл. G 06 F 15/36, 1977 (прототип).