Аналоговое множительное устройство

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

С.В. Валицкий, P.Â. Бегота и Л/А. Дускдщ

/, --,,:, .;., T; .;., „, /

Львовский ордена Ленина полите ничейный мйаткууЛ;,".;

Ф

/ (73) Заявитель (54) АНАЛОГОВОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к электрическим вычислительным устройствам с логарифмическим преобразованием сигналов и может быть использовано в . аналоговых вычислительных машинах.

Известно множительное устройство содержащее пару логарифмических пре образователей сумматор, блоки потенцирования и управления (I) .

Однако это устройство обладает малым диапазоном входных сигналов.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является аналоговое множительное устройство, содержащее первый и второй логарифмические преобразователи, выходы которых соединены с соответствующими входами аналогового сумматора, выход которого подключен ко входу антилогарифмического преобразователя, инвертор С29.

Недостатком этого устройства является сравнительно небольшой диапазон изменения входных сигналов., Цель изобретения — расширение диапазона входных сигналов.

Поставленная цель достигается тем, что в устройство введены пер5 вый и второй блоки вьщеления модуля, первый и второй усилители-ограничители, сумматор по модулю 2 и первый .и второй ключи, причем входы первого и второго блоков выделения модуля со10 единены соответственно со входами первого .и второго усилителей-ограничителей и являются входами устройства,.выходы первого и второго блоков вьщеления модуля подключены

l5 ко входам первого и второго логарифмических преобразователей соответственно, выходы первого и второго усилителей-ограничителей присоедийены к соответствующим входам сумматора по модулю 2, выход которого подключен к управляющим входам первого и второго ключей, выход антнлогарифмического преобразователя соединен с одним выводом первого ключа, вт >3 8 рой вывод которого является выходом устройства, выход антилогарифмического преобразователя через последовательно соединенные инвертор и второй ключ подключен ко второму выводу первого ключа.

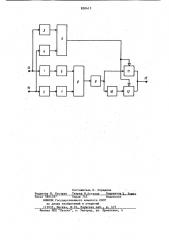

На чертеже изображена функциональная схема аналогового множительного устройства.

Устройство содержит первый и второй блоки 1 и 2 выделения модуля, первый и второй усилители-ограничители 3 и 4, сумматор 5 по модулю 2, первый и второй логарифмические преобразователи 6 и 7, аналоговый сумматор 8, антилогарифмический преобразователь 9, инвертор 1О, первый и второй ключи Il и 12, первый и второй входы 13 и 14 и выход 15 устройства.

Перемножаемые сигналы с первого и гвторого входов 13 и 14 поступают одновременно на входы первого и второго усилителей-ограничителей 3 и 4 и первого и второго блоков 1 и 2 выделения модуля. Первый и второй блоки 1 и 2 выделения модуля без изменения пропускают положительные и инвертируют отрицательные значения входных сигналов.

Преобразованные сигналы логарифмируются первым и вторым логарифмическими преобразователями 6 и 7, по.— добранными с одинаковыми характеристиками, суммируются аналоговым сумматором 8 и потенцируются в антилогарифмическом преобразователе 9. г

Первый и второй усилители-ограничители 3 и 4 в зависимости от полярности входных сигналов формируют два потенциала, причем отрицательному значению сигнала соответствует уровень логического О, а положительному — логической 1. Эти потенциалы поступают на входы сумматора 5 по: модулю 2.

При совпадении знаков входных сигналов этого блока на управляющие входы первого и второго ключей ll и 12 поступает сигнал логического

О. Первый ключ 11 замыкается, а второй .ключ 12 размыкается и выход антилогарифмического преобразователя

9 непосредственно подключается к выходу 15.

В случае несовпадения знаков на ...л.. выходе сумматора 5 по модулю 2 формируется сигнал, соответствующий ло30413 4 гической l первый ключ 11 размыкается, а второй ключ 12 замыкается.

В результате чего выходное напряжение аналогового множительного устройства инвертируется по отношению к выходу антилогарифмического преобразователя 9.

Таким образом, предлагаемое аналоговое множительное устройство

l0 .способно перемножать знакопеременные сигналы, а величины входных сиг-. налов увеличиваются почти в два раза по сравнению с известным устройством.

Формула изобретения Аналоговое множительное устройство, содержащее первый и второй логарифмические преобразователи, выходы которых соединены с соответствующими входами аналогового сумматора, выход которого подключен ко входу антилогарифмического преобразователя, инвертир, о т л и ч а.— ю щ е е с я тем, что, с целью расширения диапазона входных сигналов, в него введены первый и второй блоки выделения модуля, первый и второй усилители-ограничители, сумматор по модулю 2 и первый и второй ключи, причем входы первого и второго блоков выделения модуля соединены соответственно со входами первого и второго усилителей-ограничителей и являются входами устройства, выходы первого и второго блоков вьщеления модуля подключены ко входам первого и второго логарифмических-преобразователей соответственно, выходы первого и второго усилителей-ограничителей присоединены к соответствующим входам сумматора по модулю 2, выход которого подключен к управляющим входам первого и второго кл@чей, выход антилогарифмического преооразователя соединен с одним выводом первого ключа, второй вывод которого является выходом устройства, выход антилогарифмического преобразователя через последовательно соединенные инвертор и второй ключ подключен . ко второму выходу первого ключа.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии № 47-6781, кл. 97(8), В 12, опублик. 1972.

2. Авторское свидетельство СССР

¹ 586465, кл, G 06 G 7/16, 1975. (прототип}.

830413

Составитель О. Отраднов

Редактор И. Касаода Техвед И.Асталош Корректо Ц„ Рд11ц9?

Заказ 3804/87 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Раушская наб. д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4