Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Союз Советскнн

Соцнапнстнческнн

Рескубпнк

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()830587 (61) Дополнительное к авт, свил-ву (5I )М. Кл.

G 11 С 29/00 (22) Заявлено 09.07 ° 79 (21) 2792627/18-24 с присоелиненнем заявки J%

Всударстнвнный клмнтет (23) Приоритет

CCPP ао аллам нзобретеннй н втррнтнй

Опубликовано 15.05.81 Бюллетень Ж 18

Дата опубликования описания 25 .05 .81 (53) УДК681.327. .6(088.8) (54) ЗАПОМИНАЮП1ЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к вычислительной технике, .в частности к запоминающим устройствам (ЗУ), выполненным нз полупроводниковых элементах.

Известно устройство, содержащее накопитель, адресный блок и блок формирования данных, подключенные к блоку управления, счетчик, регистры и блок сравнения 1).

Недостатком данного устройства является невозможность проверки исправности электронного обрамления".

Наиболее близким техническим решением к изобретению является эапо15 минающее устройство, содержащее блок памяти, соответствующие входы которого соединены с выходами дешифратора адреса и регистра ввода, а выходы — со входами регистра вывода, выходы которого соединены со входами блока контроля, выход блока контроля подключен ко входу генератора тактовых импульсов, выход которого подключен ко входу счетчика адреса, выходы счетчика адреса соединены с соответствующими входами дешифратора адреса. После предварительной записи тестов логического Оп или логической "1" производится считывание информации с ряда запоминающих ячеек и ее контроль на схемах совпадения j2).

Однако такая структура ЗУ не позволяет определить неисправность электронного "-обрамления" запоминающих элементов — дешифраторов адреса, что может привести к неправильному функционированию ЗУ в целом. В то же время для проверки

ЗУ требуются специальные схемы совпадения, отвечающие данным логическим уровням, считываемым с ряда запоминающих элементов, что усложняет устройство в целом и снижает его надежность.

Цель изобретения — повышение надежности устройства.

830587 4 вестным в том, что исключаются схемы совпадения, определяющие соответствие считываемых сигналов уровням логического "0" или логической "1", осуществляется возможность контроля

5 встроенных в блок памяти дешифраторов адресов. При этом проверка блока памяти производится при помощи стандартного устройства контроля по

1О модулю два

Формула изобретения

Поставленная пель достига тся тем, что в устройство введены блок формирования тестовых кодов, вход которого соединен с выходом генератора тактовых импульсов, а выход— со входом регистра ввода.

При этом блок формирования тестовых ксдсв вьп1олнен на триггере Т.

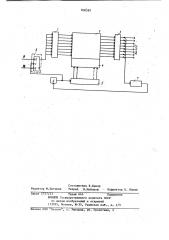

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит регистр ввода, блок 2 памяти, регистр 3 вывода, дешифратор 4 адреса, счетчик

5 адреса, генератор 6 тактовых импульсов, блок 7 контроля> блок формиро,а::ия тестов1,1х кодов. выпол11ен. ..1..й 11а Т-триггере 8, шина 9 устало «. --..-1-. "1", 1ш;на 1e: установки "0", Устро11ство работBPT следующим обра си.

8 режиме контроля "а шины 9 и 10 уста11оьки "1" . "0" поступают в проти— воф,-1зс логические сигналы. Ь зависимости От камбинац фаз на шинах

9 и 10 на выходе Т вЂ” триггера 8 устанаtttt

5 вл111"ается сигнал логической или лог1г1еского "0", который при работе ге1 «ратора б тактовых импульсов заппсь1ваотся В блОк 2 памяти а

1 ри Одновременном поступлении сигналов логическои "1 на шины 9 и 10 разрсшаетсл работа Т-тр1гггера 8 по счетному входу С, 3 этсм случае при работе генератора, в блок 2 памяти

- поочередно, байтами записываются сигналы логической "1" и логического "0".

Проверка исправности блока памяти осуществляется путем считывания контрольных тестов при помощи блока

7 коитроля на четное число Одноуровневых символов в байте. При обнарукении ошибки сигнал с выхода блока

7 контроля блокирует работу генератора тактовых импульсов, 45

Предлагаемое запоминающее устройство имеет преимущества перед из1. Запоминающее устройство с самоконтролем, содержащее блок памяти,соответствующие входы которого соединены с выходами дешифратора адреса и регистра ввода, а выходы — со входами регистра вывода, выходы которого соединены со входами блока контроля, выход блока контроля подключен ко входу генератора тактовых импульсов, выход которого подключен ко входу счетчика адреса, выходы счетчика адреса соединены с соответствующими входами пешифрптора адреса, о т л и ч а ю— щ е е с я тем, что, с целйо повышения надежности устроиства, оно

Ъ содержит блок фсрмирования тестовых кодов, вход которого соединен с выходом гейератора тактовых импульсов, а выход — со входом регистра ввода.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем,что блок формирования тестовых кодов выполнен на триггере Т.

Источники информации, принятые во внимание при экспертизе

i. Авторское свидетельство СССР

601762 кл. G 11 С 29/00, 1976.

2, Патент США gt 4055754, кл. 235-302„ опублик. 1977 (прототип).

830587

Заказ 2757 23 Тираж 6 5 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород ул. Проектная, Составитель В.Вакар

Редактор М.Циткина Техред Н.Майорош - . Корректор О.-Билак