Долговременное запоминающее устройствосо встроенным контролем

Иллюстрации

Показать всеРеферат

ОП ИСАЙИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскии

Социапистических

Респубпик

< 330588 (61) Дополнительное к авт. свид-ву (22) Заявлено 13. 07. 79 (21) 2 795940/18-.24 с присоединением заявки J% (23) Приоритет (51) M. Кл.

G 11 С 29/00

G 11 С 17/00

Гооударстввиимй комитет

СССР ло делам изобретений и открытий

Опубликовано 15.05 ° 81 Бюллетень,% 18

Дата опубликования описания 25 .05 .81 (53) УДК681.327. .66(088.8) Г.А.Бородин, Л.А.Колосков, В.N.Ko и Л.В.Лемуткин (72) Авторы изобретения (7!) Заявитель (54) ДОЛГОВРЕМЕННОЕ:ЗАПОИИНАЛЦЕЕ УСТРОЙСТВО

СО BCTPOEHHblM КОНТРОЛЕМ вания 1 11.

Изобретение относится к вычислительной технике, а именно к долговременным запоминающим устройствам (ДЗУ) на интегральных эатоминающих микросхемах словарного типа, и может быть использовано для защиты информации от разрушения в отдельных сегментах памяти.

Известно запоминающее устройство с защитой информации от разрушения, в котором производится периодическое восстановление хранимой информации с помощью перезаписи после каждого цикла считывания,. что необходимо для запоминающих элементов с разрушением информации в цикле считыОднако такое устройство затруднительно применять в случаях, когда регенерация информации производится через большое количество циклов считывания.

Известно запоминающее устройство, содержащее регистр запоминания кода времени хранения информации 2 .

Однако при отключении питания информация в регистре может быть по теряна, что в ряде случаев недопустимо.

Известно запоминающее устройство, в котором учитывается технологический разброс за счет введения специальных ячеек-датчиков, управляющих частотой регенерации информации в запоминающем устройстве 1 31.

Однако вследствие предназначения его для оргакизации регенерации в динамических полупроводниковых ОЗУ его затруднительно использовать для защиты информации в долговременных запоминающих устройствах. Не защищено оно и от сбоев из-sa снижения напряжения источников питания.

Наиболее близким по технической сущноСти к предлагаемому является запоминакяцее устройство с защитой

15

25 35

45

55

83 информации от разрушения, содержа;шее блок ППЗУ íà MHOTI-транзисторах, входной и выходной регистры, датчик контрольного сигнала на МНОП-транзисторе, пороговый элемент, формирователь сигнала регенерации. В

Таком устройстве регенерация производится для всего объема памяти 4) .

Однако известно, что очень часто долговременные запоминающие устройства исйользуются для отладки программ, микрокЬманд, констант для

ПЗУ в специализированных управляющих вычислитег-.ьных устройствах. Поэтому в процессе отладки возникает необходимость изменять отдельные команды, . константы в блоке памяти, а сегментная организация памяти подобных уст. ройств заставляет менять даже из-за одной команды содержимое всего сегмента памяти. После смены информации в нем время до будущей перезаписи для этого сегмента будет значительно больше,.чем для других сегментов, в которых подобная перезапись происходит значительно раньше, Перезапись всего объема памяти из-за одной команды и нерациональна и невыгодна, ибо тратится ресурс по циклам перезаписи в MHOII-транзисторе, который сильно ограничен (для серийно выпускаемых микросхем он составляет всего 10 циклов). Кроме того, один контрольный датчик не позволяет учесть условия эксплуатации технологический разброс и многое другое, что сказывается на времени хранения информации в различных сегментах памяти. Все это не позволяет рационально использовать реально возможный срок службы для каждого сегмента в отдельности.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в долговременное запоминающее устройство со встроенным контролем, содержащее блок памяти, входы которого соединены с выходами дешифратора, регистр адреса, выход которого подключен к одному из входов дешифратора, блок управления, первый выход которого соединен со входом регистра адреса, второй выход блока управления подсоединен к другому входу дешифратора, и пороговый элемент, введены два последовательно соединенных буферных регистра, компаратор и счетчик, вход кото0588 4 рого соединен с одним из выхоцов компаратора, выход счетчика подключен к одному иэ, входов блока управления, другой вход которого подсоединен к другому выходу. компаратора, первый и второй входы компаратора соединены. соответственно с выходами буферных регистров, выход порогового элемента подключен к одному из входов первого буферного регистра, другой вход которого соединен с выходом регистра адреса, второй вход второго буферного регистра подсоединен к третьему выходу блока управления, четвертый выход которого соединен с одним из входов порогового элемента, выход порогового элемента подсоединен к третьему входу второго буферного регистра, пятый выход блока управления соединен с третьим входом компаратора, другой вход порогового элемента подключен к выходу блока памяти.

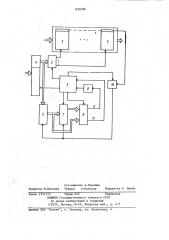

На чертеже представлена функциональная схема предлагаемого устройстВа °1, Устройство содержит блок 1 памяти, состоящий из запоминающих .сегментов 2, дешифратор 3, регистр

4 адреса, блок 5 управления, буферные регистры б и 7, компаратор 8, счетчик 9, пороговый элемент IQ выходы.11 и 12 компаратора 8.

Устройство работает следующим образом.

Для обеспечения работы устройства в дополнительный контрольный разряд каждого слова в режиме записи записывается логическая "единица"

Известно, что наибольшему разрушению от всех разрушающих факторов подвергается при хранении "единица" °

В процессе считывания информации из ДЗУ изменяющаяся величина выходного сигнала записанной "единицы" с дополнительной разряда поступает на пороговый элемент Iд, порог срабатывания которого выбран выше, чем у остальных (информационных) разрядов блока 1 памяти. Это позволяет ранее чем перестанут надежно срабатывать усилители считывания информационных разрядов блока 1 памяти определить момент наступления регенерации информации. При этом, еали произошло однократное срабатывание порогового элемента 10, то выходной сигнал с него записывает в регистр 6 код адреса сегмента, 830588 6

50 средств на изготовление нового подобного ДЗУ для отладки программ.

Формула изобретения

5 поступающего со старших разрядов регистра 4 адреса. Поскольку однократный сбой может быть случайным, то устройство ожидает следующего сбоя. Когда поступает следующий

5 сбой, код адреса сегмента с предыдущим сбоем поступает в регистр 7, а в регистр 6 записывается код адреса сегмента с новым сбоем. По сигналу из блока 5 управления в компа- 1о раторе 8 производится сравнение кодов, поступающих из регистра 6 и регистра 7., Если коды разные, то это означает, что причина выхода из области устойчивой работы общая (скачок питания, изменение климатических условий больше допустимого предела и т.п.), и необходимо устранить причины, порождающие эти сбои. Информация о несравнении кодов 2о поступает в блок 5 управления по

1 шине 11. Если коды равны, то это означает, что происходят сбои в одном сегменте 2 памяти, что означает, в свою очередь, что ресурс хра- д нения информации в данном сегменте исчерпан. Необходимое число сбоев о принятии решения считается в счетчике 9 по сигналу сравнения, поступающему по шине 10. После этого gp должен быть организован процесс перезаписи информации в сегменте, адрес которого хранится в регистре 6.

Использование изобретения позволяет более точно определять момент

35 регенерации информации для каждого отдельного сегмента памяти, что обеспечивает гибкость в отладке программ, микрокоманд и констант.

Поскольку ресурс хранения в норч 4р мальных условиях и во всем диапазоне климатических изменений сильно различается (для МНОП-структур серийного производства в 1,5 раза), то без применения данного изобретения было бы необходимо период регенерации производить по наихудшему варианту для наихудшей ячейки сразу во всем блоке памяти. Однако условия эксплуатации различны в реальных gp условиях (ппохие сменяются хорошими и наоборот), и поэтому недоиспользован ресурс по хранению для каждого сегмента в отдельности. Применение предлагаемого устройства позволяет в 1,5 раза повысить срок службы

ДЗУ, а это эквивалентно экономии до

Долговременное запоминающее уст ройство со встроенным контролем, содержащее блок памяти, входы которого соединены с выходами дешифратора, регистр адреса, выход которого подключен к одному из входов цешифратора, блок управления, первый выход которого соединен со входом регистра адреса, второй выход блока управления подсоединен к другому входу дешифратора, и пороговый элемент, о т л и ч а ю щ е е с я тем, что, с целью .повышения надежности устройства, в него введены два последовательно соединенных буферных регистра, компаратор и счетчик, вход которого соединен с одним из выходов компаратора, выход счетчика подключен к одному из входов блока управления, другой вход которого подсоединен к другому выходу компаратора, первый и второй входы компаратора соединены соответственно с выходами буферных регистров, выход порогового элемента подключен к одному из входдв первого буферного регист-. ра, другой вход которого соединен с выходом регистра адреса, второй вход второго буферного регистра подсоединен к третьему выходу блока управления, четвертый выход которого соединен с одним из входов порогового элемента, выход порогового элемента подсоединен к третьему входу второго буферного регистра, .пятый выход блока управления соединен с третьим вхо" дом компаратора, другой вход порогового элемента подключен к выходу блока намяти.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции Ф 2204012, кл. G 11 С 7/00, опублик. 1974.

2. Патент США У 3737879, кл. G 11 С 7/00, опублик. 1973.

3. Патент СПЖ N - 3796998, кл. 340-173, опублик. 1974.

4. Авторское свидетельство СССР

9 580587, кле G ll С 29/00, опублик, 1978 (прототип).

830588

Составитель А.Воронин

Редактор М.Циткина Техред Н.Майорош Корректор О. Билак

Заказ 2757 23 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул, Проектная, 4