Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

III> 830589

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Социалистические

Ресттубпнк (61} Дополнительное к авт. саид-ву (22) ЗаЯвлено 22.08. 79 (21} 2814122/18-24 с присоединением заявки,% (23) Приоритет (5E)M. Кл.

6 11 С 29/00, Гасударственный кемнтет лO делам нзебретеннй н открытий

Опубликовано 15. 05. 81 ° Бюллетень J% 18

3ата опубликования описания 25.05 .81 (53) УДК681.327. .6(088.8) (54) ОПЕРАТИВНОЕ ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известны запоминающие устройства, содержащие регистр адрес, дешифратор адреса, накопитель, информационные регистры, блок контроля, производящий контроль записываемой и считываемой информации на соответствие информационных и контрольных разрядов и восстановление информа10 ции в случае сбоя в адресном тракте

Недостатком этих устройств является то, что.в них разрешается запись и считывание информации иэ любой ячейки.

Наиболее близким но технической сущности к изобретению является запоминающее устройство с расширенными функциональными воэможностями, содержащее регистр и дешифратор адреса, накопитель, блок усилителей записи — считьп 33иии, цополнитель2 ный регистр слова блок контроля, схемы не, и или 21 .

Недостатком данного устройства является низкое быстродействие при осуществлении контроля считываемой и записываемой информации.

Цель изобретения — увеличение быстродействия оперативного запоминающего устройства.

Поставленная цель достигается тем, что в оперативное запойинающее устройство, содержащее накопитель, адресные входы которого подключены к выходам дешифратора, а его информационные входы — выходы — к входам-выходам блока усилителей, входы адресного дешифратора подключены к выходам адресного регистра, вторые входы блот а усилителей подключены к соответствующим выходам информационного регистра и к выходам инверторов, блок управления, выходы которрго подключены к управляющим входам адресного регистра, блока

0589 4

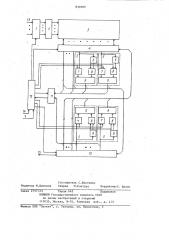

В режимах "Запись", "Запись с инверсией контрольных разрядов" и "Запись с проверкой" адрес ячейки, находящийся на шинах 13, и записываемое слово, находящееся на шинах

l5 фиксируются соответственно на адресном регистре 1 и на ннформационнбм регистре 103 и производится подключение выходов информационного регистра 10 к блоку 11 контроля, который контролирует записываемую информацию. В случае появления на выходе блока II контроля сбоя инфор45 мация в накопитель не записывается.

При отсутствии сигнала ошибки на выходе блока 11 контроля и работе в режиме записи информационные разряды напрямую, а контрольные — прохо50 дя с помощью управляющих сигналов через элементы И 7 и ИЛИ 9 — поступают на блок усилителей и с его выходов записываются в накопитель.

Режим "Запись с инверсией контроль55 ных разрядов" отличается от режима

"Запись" тем, что их значения инвертируются с помощью элементов НЕ 6. В, этом случае в ячейку записывается

3 83 усилителей, инверторов и блока кон троля, выход блока контроля подключен ко входу блока управления, введены дополнительные инверторы, входы которых подключены к соответствующим выходам блока усилителей, одни входы блока контроля подключены к соответствующим выходам блока усилителей, к выходам дополнительных инверторов и ко входам информационного регистра, управляющие входы дополнительных инверторов подключены к соответствующим выходам блока управления.

На чертеже приведена структурная схема устройства.

Устройство содержит адресный регистр 1, дешифратор 2, накопитель 3, блок 4 усилителей, инверторь1 5, эле-! менты НЕ 6, первые элементы И 7, вторые элементы И 8, элементы ИЛИ.9, информационный регистр 10, блок 11 контроля, блок 12 управления, адресные шины 13 управляющие шины 14 и информационные шины 15 »

Устройство работает в следующих режимах: "Запись", "Запись с инверсией контрольных разрядов", "Запись спроверкой", "Считывание", "Считывание с инверсией контрольных разрядов".

40 слово с инвертированными контрольными разрядами.

В режиме "Считывание" происходит считывание информации из накопителя в соответствии с адресом, хранимым в адресном регистре 1. Считанная информация появляется на выходах блока усилителей. Информационные разряды напрямую, а контрольные— через элемент И 7 и через элемент

ИЛИ 9 поступают на блок ll контроля и информационный регистр 10. Появление сигнала ошибки на выходе блока

11 контроля свидетельствует о несоответствии информационных и контрольных разрядов. При отсутствии сигнала ошибки на выходе блока ll контроля информация записывается в информационный регистр 10 и выдается на шины 15.

Работа в режиме "Считывание с ин-, версией контрольных разрядов" отличается от режима "Считывание" тем, что на выходах элементов ИЛИ 9 появляются контрольные разряды, инвертированные элементами НЕ 6. Отсутствие сигнала ошибки на выходе блока

il контроля свидетельствует о пра-.вильной работе устройства.

При работе устройства в режиме

"Запись, с проверкой" сразу же начинается считывание слова по адресу, хранимому в адресном регистре 1, и контроль записываемого слова. Это возможно, так как считывание слова является более инерционным процессом и моменты контроля записываемого и считываемого слова можно разнести во времени. Если на выходе блока ll контроля сигнал ошибки не появляется, то осуществляется запись слова через блок 4 усилителей в накопитель 3 °

Таким образом, устройство выдает сигнал ошибки в следующих случаях . при сбое входной информации, при попытке записи данных в режиме "3aпись с проверкой" в ячейки, в которые данные при начальной загрузке были записаны в режиме "Запись с инверсией контрольных разрядов", при попытке считывания данных в режиме "Считывание" из ячеек, в которые данные при начальной загрузке были записаны в режиме. "Запись с инверсией контрольных разрядов". Выи- . грыш в быстродействии получен за счет отсутствия такта записи считан5 830589 6 ной из накопителя информации в допол- ров и блока контроля, выход блока нительный регист в ежима р режимах "Считы- контроля подключен ко входу блоха ванне" и "Считывание с инверсией управления ва, отличающееся контрольных разрядов" н за счет сов- тем,, что,.с целью повышения быстроначала моментов считывания 5 действия устройства, B него введены из накопителя и контроля записыва- дополнительные инверторы, входы емой информации в режиме "Запись с которых подключены к соответствуюtt проверкон щим выходам блока усилителей, одни входы блока контроля подключены к соответствующим выходам блока усилиФормула изобретения телей, к выходам дополнителъных инверторов и ко входам информационного регистра, управляющие входы дополнительных инверторов подключены к соответствующим выходам блока управления.

Оперативное запоминающее устройство, содержащее накопитель, адресные входы которого подключены к выходам дешифратора, а его информа" ционные входы — выходы — к входам-выходам блока усилителей, входы дешифратора подключены к выходам адресного регистра, вторые входы блока усилителей подключены к соответствующим выходам информационного регистра и к выходам инверторов, блок управления, выходы которого подключены к управляющим входам адресного ре.гистра, блока усилителей, ннвертоИсточники информации,,принятые во внимание при экспертизе

1. Авторскае свидетельство СССР

У 528614, кл. G 11 С 29/00,, 26.07.74.

2. Авторское свидетелватво СССР по заявке В 2571643/18-24, кл. G !1 С 29/00, 18.01.79 (прототип).

830589

Составитель С,Шустенко

Редактор М.Циткина Техред M.Êoøòóðà Корректор О. Билак

Заказ 2757 23 Тираж 645. Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород. ул. Проектная, 4