Цифровой фильтр

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИЕЛЬСТВУ (1830635

Ф ф (61) Дополнительное к авт. свид-ау (22) Заявлено170579 (23) 2801726/18-24 (51 1М. Кл.з

Н 03 Н 17/04 с присоединением заявки Мо (23) Государственный комитет

СССР но делам изобретений и открытий

Приоритет .

Опубликовано 150591. Бюллетень 89 18 (53) УДК681 З (088. 8) Дата опубликования описания 15g 581 (72) Авторы изобретени

В.М. Ерухимович, Б.M. Зелкин и (71) Заявитель (54) ЦИФРОВОЙ ФИЛЬТР

Изобретение относится к вычислительной технике и. предназначено для цифровой фильтрации сигналов.

Известен аналого-цифровой фильтр, в котором применяется преобразование двоичных "кодов в случайные последовательности с помощью блоков вероятностного округления. Применение вероятностно-импульсного кодирования позволило существенно упростить аппаратурную реализацию аналогового фильтра, в частности для умножения используется элемент Равнозначность, для сложения — элемент 2И-ИЛИ, а интегрирование осуществляется с помощью реверсивного счетчика импульсов (1).

Недостатком данного устройства является значительная погрешность интегрирования, обусловленная стохастической структурой последовательностей на входе счетчика.

Наиболее близким по технической сущности является цифровой фильтр, который содержит два блока умножения, элемент задержки, регистры коэффициентов и регистратор отсчетов входного сигнала, подключенные соответственно ко входам блоков умножения, сумматор, соединенный входами с выходами блоков умножения, а выходом со входом элемента задержки(2).

Недостаток данного цифрового фильтра заключается в.большой слож-. ности его аппаратурной реализации.

Цель изобретения — упрощение цифрового фильтра.

Поставленная цель достигается тем, что цифровой фильтр, содержащий регистр отсчетов входного сигнала, вход которого является входом фильтра, два регистра коэффициентов, выходы которых соединены соответственно с первыми входами двух блоков ум15 ножения, выходы которых соединены соответственно с первым и вторым входами сумматора, выход которого через элемент задержки связав со вторым входом первого блока умноже2О ния, второй вход второго блока умножения соединен с выходом регистра отсчетов входного сигнала, содержит регистр сдвига, две .группы элементов И, причем одни выходы регистра сдвига подключены соответственно к третьему и четвертому входам сумматора и к первым входам элементов И первой и второй групп, выходы которых соединены соответственно с третьими

30 и четвертыми входами первого и второ830635

25 го умножителей, выходы элементов И первой группы соединены со вторым входом элемента задержки.

При этом сумматор содержит сумматор по модулю два, входы которого являются третьим и четвертым входами сумматора соответственно, а выходы — подключены к первым входам элементов И, вторые входы которых являются первым и вторым входами сумматора соответственно, выходы элементов И подключены соответственно к первому и второму входам элемента

ИЛИ, выход которого является выходом сумматора.

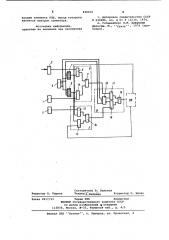

На чертеже представлена блок-схема цифрового фильтра.

Схема содержит регистры 1 и 2 коэффициентов, регистр 3 отсчетов входного сигнала, блоки 4 и 5 умножения, регистр 6 сдвига (с обратной связью), две группы элементов И 7 и 8 . Блок

4 умножения содержит коммутаторы 9 и 10, элемент Равнозначность 11, блок 5 — коммутаторы 12 и 13 и элемент Равнозначность 14, кроме того, схема содержит сумматор 15,.состоящий из элемента ИЛИ 16, двух элементов И 17 и 18, сумматора 19 по модулю два, элемент 2С задержки на интервал дискретизации. Группа элементов И 7, подключенная входами к выходам регистра б сдвига, а выходами ко вторым входам коммутаторов 9 и 13, первые входы которых соединены с выходами регистров 2 и 3, составляют преобразователь двоичного числа регистров 2 и 3 в псевдослучайную последовательность. С аналогичными

"вязями группа элементов И 8, коммутаторы 10 и 12, регистр 1 составляет преобразователь двоичного числа регистра 1 в псевдослучайную последовательность. Элемент Равнозначность 11 с входами, подключенными к выходам коммутаторов 9 и 10, выполняют роль умножителя в блоке 4 умножения. В блоке 5 умножения роль умножителя выполняет элемент Равнозначность 14, входы которого соединены с выходами коммутаторов 12 и

13. В сумматоре 15 элемент ИЛИ 16 подключен входами к выходам элементов И 17 и 18, первые входы которых соединены с выходами элементов Равнозначность 11 и 14, а вторые входы с прямым и инверсным выходами сумматора по модулю два, подключенного входами к выходам всех разрядов регистра 6 сдвига °

Цифровой фильтр работает следующим образом.

На выходах регистра 6 сдвига генерируются псевдослучайные последовательности, которые поступают на входы элементов И 7 и 8. Последовательности с выходов элементов И 7 и

8 поступают на первые входы коммутаторов 9„10,12 и 13, ко вторым вхо30

ЬО

65 дам которых подключены выходы разрядов регистров 1,2,3. Последовательности с выходов коммутаторов 9,10

12 и 13 поступают на входы элементов

11 и 14, с выходов которых на первые входы элементов И 17 и 18 . На вто рые входы элементов H 17 и 18 подаются несовместные последовательности с прямого и инверсного выходов сумматора 19 по модулю два, причем эти последовательности некоррелированы с последовательностями с выходов элементов Равнозначность 11 и

14. Формируемые на выходах элементов

И 17 и 18 несовместные последовательности подаются на входы элемента

ИЛИ 16. Последовательность с выхода элемента ИЛИ 16 представляет собой сумму двух чисел с весовым коэффициентом 1/2.

Данный цифровой фильтр выгодно отличается от известного тем, что уменьшает аппаратурные затраты при сохранении заданной точности.

Формула изобретения

1. Цифровой фчльтр, содержащий регистр отсчетов входного сигнала, вход которого является входом филь-.. тра, два регистра коэффициентов, выходы которых соединены соответственно с первыми входами двух блоков умножения, выходы которых соединены соответственно с первым и вторым входами сумматора, выход которого через элемент задержки связан со вторым входом первого блока умножения, второй вход второго блока умножения соединен с выходом регистра отсчетов входного сигнала, о т л ич а ю шийся тем, что, с целью упрощения устройства, фильтр содержит регистр сдвига, две группы элементов И, причем одни выходы регистра сдвига подключены соответственно к третьему и четвертому входам сумматора и к первым входам элементов И первой и второй групп, выходы которых соединены соответственно с третьими и четвертыми входами первого и второго умножителей, выходы элементов

И первой группы соединены со вторым входом элемента задержки.

2. Фильтр по п. 1, о т л и ч аю шийся тем, что сумматор содержит сумматор по модулю два, входы которого являются третьим и четвертым входами сумматора соответственно, а выходы — подключены к первым входам элементов И, вторые входы которых являются первым и вторым входами сумматора соответственно, выходы элементов И подключены соответственно к первому и второму

830635

Составитель В. Вальков

Техред A.8ä He . корректор О. Билак

Редактор Л. Тюрина

Заказ 2917/33

Тираж 98& -Подписное

ВНИИПИ Государственного комитета СССР по- делам иэобретений открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. ужгород, ул. Проектная, 4 входам элемента ИЛИ, выход которого является выходом сумматора.

Источники информации, принятые во внимание нри экспертнэе

1. авторское свидетельство СССР

Р 634286, кл. G 01 F 15/34, 1974.

2. Гольденберг Л.М. Цифровые фильтры. М.i Связь r 1974 (прототип).