Синтезатор частот

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬ6РЕТЕН ИЯ

К . АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советск на

Социалистических

Республик

S .г » (61) Дополнительное к авт. сви««-ву— (22) Заявлено 12, 11, 79 (21) 2841979/25-08 (5l )NL. Кл.

Н 03 1, 7/08 с присоединением заявки,рй—

Веудврстевнный кемнтет

СССР но делам нзебретеннй н открытн11

{23) Приоритет—

ОпУбликовано 15.05.81. Бк«ллетеиь .ле 18 (53) УДК 621.373. .42 (088. 8) Дата опубликования описания 17.05.8 1 (72) Автор. изобретения з

Р»

" - А .Ю1::0-,д,-, «

Всесоюзный заочный электротехнический ифтитутти@ЙЙЙ-- ;

В.Н. Кочемасов (71) Заявитель (54) СИНТЕЗАТОР ЧАСТОТ

Изобретение относится к радиотехнике и может использоваться для синтеза изменяющихся по заданному закону частот в радиолокации, радиовысотометрии, технике связи и т.д .

Известен синтезатор частот, содер- з жащий соединенные в кольцо управляемый генератор, смеситель, блок деления частоты, импульсно-фазовый детектор, блок коррекции и сумматор, другой вход которого подключен к выходу модулятоl0 ра, а также последовательно соединенные генератор эталонной частоты и синхронизатор, первый, второй, третий и четвертый выходы которого соедине1$ ны соответственно с входом модулятора, другим входом импульсно-фазового детектора, с установочным и управлятещим. входами блока деления частоты, при этом управляющий вход блока коррекции подключен к другому выходу блбка деления частоты (1).

Однако в данном синтезаторе частот относительно низка точность воспроиз2 ведения выходной частоты из-за низкого быстродействия кольца автоподстройки, связанного с ограниченной полосой пропускания фазового детектора, вследствие чего кольцо автоподстройки не отслеживает высокочастотных возмущений .

Цель изобретения — повышение точности воспроизведения выходной частоты .

Для достижения цели в синтезатор частот, содержащий соединенные в кольцо управляемый генератор, смеситель, блок деления частоты, импульсно-фазовый детектор, блок коррекции и сумматор, другой вход которого подключен к выходу модулятора, а также последовательно соединенные генератор эталонной частоты и синхронизатор, первый, второй, третий и четвер«ь«й выходы которого соединены соответственно с входом модулятора, другим вхоpом импульсно-фазового детектора, с установочным и управляющим входами

830652

25 у у У

4 4 т

4 4 шению пе иода пискретизации по сравне-, .нию с Tg(9f в У2 раза.

При формировании колебаний линей50 ным законом изменения частоты (фиг.2) синтезатор работает следующим образом.

До начала модуляции йайО в синте55 заторе осуществляется стабилизация начапьной частоты f При этом моду3 блока деления частоты при этом yeas ляющий вход блока коррекции подключен к другому выходу блока деления частоты, между пятым выходом синхронизатора и другим входом смесителя введены последовательно соединенные блок управления и фазовращатель, сигнальный вход которого подключен к выходу генератора эталонной частоты, при этом другой вход блока управления соединен с первым выходом блока деления частоты.

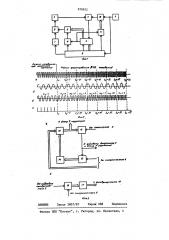

На фиг. 1 представлена структурная электрическая схема предлагаемого синтезатора частот; на фиг. 2— временные диаграммы работы; .на фиг. 3 пример конкретного выполнения блока деления частоты и блока управления.

Синтезатор частот содержит управляемый генератор 1, смеситель 2, блок

3 деления частоты, импульсно-фазовый детектор 4, блок 5 коррекции, сумма-, тор 6, модулятор 7, синхронизатор 8, генератор 9 эталонной частоты, фазовращатель 10, блок II управления.

Ф Ф Ф Ф Ф . Ф Ф .Ф

6 7 3Г 0 „.и, 0 у 0 У 0

2 2 2 2

Ji 9Я О, 9Д у дг 0

8 2 8 8 2 8

У у 9, 2Ю 37 17Т 0

Значения Ф представляют собой систематическую ошибку, которая вносилась бы при измерении по методу фаэовой дискретизации. В предлагаемом синтезаторе эта систематическая погрешность компенсируется с помощью фазовращателя 10, обеспечивая после появления каждого очередного,импульса с выхода блЬка 3 деления частоты необходимый фазовый сдвиг 1фиг. 2 б1,, например, в соответствии с таблицей, можно уменьшить пе иод дискретизации по. сравнению с 1g/4(. Эпюры, представ5

4

Синтез а тор час тот р аб отает следующим образом.

В случае формирования колебаний с линейной частотной модуляцией (ЛЧИ) блок 3 деления частоты состоит иэ включен ых в кольцо делителя 12 с переменным коэффициентом деления (ДПКД), счетчика 13, делителя 14 и сумматора

15 (фиг. 2 а), а блок 11 управления из последовательно включенных реверсивного счетчика 16, вход установки нулевого состояния которого подключен к синхронизатору. Известно, что минимально возможный период дискретизации Т =©% определяется значениями девиации % и длительности сигнала

В случае, когда выборки ЛЧИ колебания берутся чаще, значения фазового набега, связанного с частотной модуляцией, оказываются некратными целому числу

2Х рад. В таблице приведены значения Ф,, равные фазе3(— 3 ЛЧИ колебас ния за вы4етом 2ЛЪ рад, где и=

9 . О 12 13 -Ф 6. р o — o y. o T o

2 2. У У 97f 0 9// 7f 7f 0

8 2 8 8 2 8

1 7 Т1 2Я, 97 /7 g 0

У,16 4 16 16 4 16 ленные на фиг. 2, соответствуют уменьлятор 7 откпючен, реверсный счетчик

16 установлен в нулевое состояние и преобразователь кодов 17 вырабаты830652 6 вает команду, обеспечивающую нуле,вой фазовый сдвиг в фазовращателе 10 (фиг. 2 б), а блок 3 деления частоты работает в режиме обычного деления частоты в Мр раз . В момент времени

О 5 (фиг. 2), соответствующий подаче команды на формирование ЛЧМ колебаний, включается модулятор 7, с реверсивного счетчика 16 снимается напряжение установки нуля, а блок 3 деления час- 10 тоты переходит в режим с переменным делением частоты N<=f (R) где R- номер импульса, появляющегося на выходе блока 3 деления частоты, В общем случае коды, поступающие от синхрониза- 15 тора 8, в режимах стабилизации начальной частоты и формирования ЛЧМ колебаний могут быть различными, например (на фиг. 2) Ng=l,a N=4. Кроме того, из эпюр, приведенных на фиг. 2 в и г, 20 следует, что N =11 =4 > N =N =5

-1 - 3 + и =й =6 и т.д. в отличие от ранее известных схем, блок 3 делениА частоты меняет свой коэффициент деления лишь после появления каждого -го импульса на его выходе, гдес =У/Ф,. Периодичность изменения систематической ошибки (см. таблицу) позволяет использовать реверсивный счетчик 16 для получения периодически повторяющихся кодов, подаваемых на вход преобразо. вателя 17 кодов, в котором формируются команды, управлякщие сдвигом фазы в фазовращателе 10 . Входящий в состав блока 3 деления частоты делитель-,З5

14 предназначен для того, чтобы обест печить постоянство коэффициента деления ДПКД 12 на периоде измерения фа зовых сдвигов Ф . Дпя приведенных в таблице случаев (Ф =Til2, л /4, 7/8, 4О

Т/16), его коэффициент деления составляет соответственно 2.,4,8 и 16.

В режиме стабилизации начальной частоты на счетчик 13 с синхронизатора

8 подается напряжение, обеспечиваю- 45 щее установку нулевого числа на выходе счетчика 13. После начала модуляции это напряжение снимается и код с выхода счетчика 13> сортветствующий номеру импульса на выходе ДПКД 12, а значит и всего блока 3 деления частоты, подается через делитель 14 к сумматору 15> s котором осуществляется его суммирование с кодом, поступающим от синхронизатора 8. Помимо своего55 прямого назначения код с выхода сумматора 15 используется и для изменения коэффициента усиления по кольцу обратной связи с целью выравнивания чувствительности к измеряемым в импульсно-фазовом детекторе 4 ошибкам.

В случае, когда ф =К/Ф =2, где

P — целое число, необходимость в делителе 14 отпадает, поскольку деление в 2 раз осуществляется простым сдвигом разрядов.

Достигаемое в предлагаемом синте-: заторе расширение полосы пропускания фазо3ого детектора увеличивает быстродействие кольца автоподстройки ЧМ колебаний, что приводит либо к повышению точности воспроизведения заданного закона ЧМ, либо к снижению требований к характеристикам управляемого.генератора и модулятора.

Формула изобретения

Синтезатор частот, содержащий соединенные в кольцо управляемый генератор, смеситель, блок деления частоты, импульсно-фазовый детектор, блок коррекции и сумматор, другой вход которого подключен к выходу модулятора, а также последовательно соединенные генератор эталонной частоты и синхронизатор, первый, второй, третий и четвертый выходы которого соЕдинены соответственно. с входом модулятора, другим входом импульсно-фазового детектора, с установочным и управляющим входами блока деления частоты, при этом управлякщий вход блока коррекции подключен к другому выходу блока деления частоты, о т л и ч а ю щ и йс я тем, что, с целью повышения точности воспроизведения выходной часто» ты, между пятым выходом синхронизатора и другий входом смесителя введены последовательно соединенные блок управления и фазовращатель, сигнальный вход которого подключен к выходу генератора эталонной частоты, при этом другой вход блока управления соединен с первым выходом блока деления частоты.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N- 640418, кл . Н -03 В 3/04, 1977 (ррототип) .

83D652 ф Р м (+Ут ф!н2 ф У kp04f уф !

1,т, I

I I I . I !! . t I !

Л =4, yl=S I МÇ=J I Nq 6 NS*7I ebea 4137 !

I 1 ь тт тгт sv (Риа2-, у g Я аррелуии

ClPtOAf f

fe счмеФФ i 4FwR d о Хрспф л Ю

ВНИИПИ Заказ 3807/87 Тираж 988 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

В» цоррв4еве лугафаж/а ююл.ю У!

I I! !

1 !

I! I