Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советсккк

Соцкалнстическмк

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()832598 (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.07.79 (21) 2795999/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

G l l С 9/06

Гееударстееллык комитет (53) УДК 681.327..66 (088.8) Опубликовано 23.05.81. Бюллетень № 19

Дата опубликования описания 28.05.81 по делам изобретений и открытий

С. М. Рожков и Б. М. Оржевский (72 } А вторы изобретения

I

Ч C

Московский автомобильный завод им. И. А. Л(ихачева - (Производственное объединение ЗИЛ)) (71) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств хранения и выдачи дискретной информации, когда не требуется большая частота выборки, например в случае автоматического управления выдачей тех или иных изделий со склада по предварительно введенным в буферное запоминающее устройство командам, каждая из которых автоматически выдается на исполнительное устройство после выполнения предыдущей.

Известно буферное запоминающее устройство, содержа шее блок памяти, блок управления на триггерах, тактовые шины (1).

Недостатком этого устройства является большое количество оборудования блока управления (два триггера и три элемента И на один разряд), что снижает надежность.

Наиболее близким к предлагаемому по технической сущности является буферное запоминающее устройство, включающее в себя блок памяти, тактовую шину, блок управления, содержащий в каждом разряде основной и вспомогательный триггеры и элемент ИЛИ вЂ” НЕ, нулевой выход вспомогательного триггера каждого -разряда соединен со входами триггеров блока памяти, выходы которых соединены со входами последуюших триггеров (2).

Однако наличие большого числа аппаратуры блока управления (два триггера и од5 на схема "ИЛИ вЂ” НЕ "на один разряд) отрицательно влияет на надежность ) стройства.

Кроме того, в связи с тем, что количество заполненных разрядов блока памяти однозначно связано с состоянием триггеров блока управления, переключение которых

1о происходит как при вводе информации, так и при выводе ее, то в случае сбоя в блоке управления, например при вводе, произойдет искажение информации, хранимой в блоке памяти, что также приводит к снижению надежности устройства.

Цель изобретения — повышение надежности буферного запоминаюшего устройства.

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее регистры сдвига, каждый из кото2о рых выполнен на 1К-триггерах, триггеры унравления и тактовую шину, введены элемент ИЛИ, триггер окончания сдвига и элемент И, выход которого соединен со счетным входом первого триггера управления, счет832598

Формула изобретения ный вход каждого триггера управления соединен с единичным выходом последующего триггера управления, единичный выход каждого триггера управления подключен к R-входам каждого 1К-триггера регистров сдвига, выходы последних 1К-триггеров регистров сдвига соединены со входами элемента ИЛИ, выход которого подключен ко входу триггера окончания сдвига, один из выходов триггера окончания сдвига соединен с первым входом элемента И, второй вход которого подсоединен к тактовой шине, другой выход триггера окончания сдвига подключен к

К-входам триггеров управления.

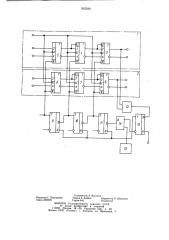

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит регистры 1 и 2 сдвига (на чертеже показаны только два регистра сдвига), выполненные на 1К-триггерах 3 — 8 (на чертеже каждый из регистров содержит три триггера), триггеры 9, 10 и 11 управления (их количество равно числу триггеров регистров сдига), элемент ИЛИ 12, триггер 13 окончания сдвига, элемент И 14, тактовую шину 15.

Устройство работает следующим образом.

В исходном положении триггеры 3 — 8 регистров 1 и 2 сдвига и триггеры 9 — 11 управления выключены, а триггер 13 окончания сдвига включен. Ввод информации и ее сдвиг в регистрах 1 и 2 сдвига происходит по заднему фронту импульса записи.

При выводе информации из регистров 1 и 2 сдвига сигналом считывания триггер 13 сбрасывается, элемент И 14 открывается и тактовые импульсы с тактовой шины 15 поступают на триггер 11 управления (триггеры управления соединены по схеме однотактного счетчика) .

В процессе счета включается каждый из триггеров 9 — 11, они сбрасывают соответствующие триггеры регистров сдвига того же разряда. При этом перепад с «1» на «О» на их единичных выходах (в случае, если триггер был до этого включен) включает последующий триггер. Таким образом, во время переключений триггеров 9 — 11 информация, записанная в одном из триггеров 3 — 8 регистров 1 и 2 сдвига, ближайшая к выходу, поразрядно сдвигается до тех го

25 зо

45 пор, пока не попадет в последние триггеры

5 и 8 регистров и 2. На выходе элемента

ИЛИ 12 появляется сигнал «1» который включает триггер 13, элемент И 15 запирается и подача тактовых импульсов на триггеры

9 — 11 управления прекращается, а сам он гасится.

Таким образом, триггеры управления 9—

11 работают только при выводе информации, все остальное время они находятся в выключенном состоянии и не переключаются. Это позволяет исключить случаи искажения информации из-за сбоев в устройстве, например при вводе. Кроме того, указанное выполнение буферного запоминающего устройства позволяет сократить число триггеров управления, приходящихся на од. л разряд.

Буферное запоминающее устройство, содержащее регистры сдвига, каждый из которых выполнен на 1К-триггерах, триггеры управления и тактовую шину, отличающееся тем, что, с целью повышения надежности устройства, в него введены элемент ИЛИ, триггер окончания сдвига и элемент И; выход которого соединен со счетным входом первого триггера, счетный вход каждого триггера управления соединен с единичным выходом последующего триггера, управления, единичный выход каждого триггера управления подключен к R-входам каждого 1Ктриггера регистров сдвига, выходы последних 1К-триггеров регистров сдвига соединены со входами элемента ИЛИ, выход которого подключен ко входу триггера окончания сдвига, один из выходов триггера окончания сдвига соединен с первым входом элемента И, второй вход которого подсоединен к тактовой шине, другой выход триггера сдвига подключен к R-входам триггеров управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 407396, кл. G 11 С 19/00, 1973.

2. Авторское свидетельство СССР № 616654, кл. G 11 С 19/00, 1978 (прототип).

832598

Редактор С. Патрушева

Заказ 3339/39

Составитель А. Воронин

Техред А. Бойкас Корректор Н. Швыдкая

Тираж 645 Подписное

ВНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4