Элемент памяти для регистра сдвига

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

«i>832600

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 120779 (21) 2796639/18-24 с присоединением заявки Ио— (23) Приоритет—

Опубликовано 230581. Бюллетень Й9 19 . Дата опубликования описания 2505.81 (51)М. Клз

G 11 С 19/28

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 327. .66(088.8) (72) Авторы изобретения

Ы,;":„".!Щ q р, g ! 4 и

Йекрафар" -" -",—.. у е ;

В. И. Золотаревский и В. М. (71)заявители (54) ЭЛЕМЕНТ ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

10

Изобретение относится к автоматике и вычислительной технике и пред-. назначено для построения быстродействующих квазистатических регистров

5 сдвига. . Известны ячейки памяти для регистра сдвига, имеющие два противофазных выхода, а также выход переноса информации, которые построены на трех или четырех инверторах, образующих квазистатические триг=еры, которые управляются одним или двумя управляющими тактовыми сигналами (1) и (2).

Наиболее близким к предлагаемому по технической сущности к изобретению 15 является элемент памяти для регистра сдвига, содержащий квазистатический триггер, состоящий из двух последовательно соединенных инверторов .вход первого инвертора через первый согласующий каскад подключен к входной шине, третьего инвертора, вход которого через второй согласующий каскад соединен с выходом первого инвертора, а выход с выходной шиной. Управляющие входы согласующих каскадов соединены соответствующими управлякщими ши аамие (3).

Однако эти устройства из-за наличия дополнительного инвертора имеют более з0 низкое быстродействие и более высокую потребляемую мощность по сравнению с двухинверторными квазистатическими триггерами, которые не имеют противофазных синхронных выходов.

Цель изобретения . — повышение быстродействия и снижение мощности потребления регистра сдвига.

Поставленная цель достигается тем, что в элемент памяти для регистра сдвига, содержащий квазистатический триггер, выполненный на двух инверторах, вход перво1:о,нз которых соединен через первый согласующий элемент со входом элемента памяти, третий,инвертор, вход которого соединен через второй согласующий элемент с выходом первого инвертора, выход третьего инвертора йодсоединен к выходу элемента памяти, управлякшие входы согласукщих элементов соединены соответственно с первой и второй шинами управления, введены два ключа, управляющие входы которых подсоединю ны к шинам управления, первые выходы ключей соединены со входом первого инвертора,, вторые выходы ключей соединены соответственно с выходами второго инвертора.

832600

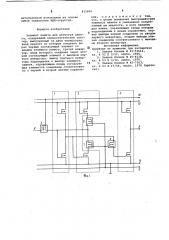

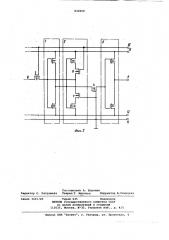

На фиг. 1 изображена функциональная схема предложенного устройства выполненного на МДП-транзисторах одного типа проводимости; на фиг. 2 — вариант. выполнения предложенного устройства, выполненного на дополняющих МДП-транзисторах.

Устройство .содержит первый и второй инверторы .1 и 2, первый и второй согласукщий элементы 3 и 4 третий инвертор 5, ключи б и 7, вход 8 и вйход 9 элемента памяти,. шины 10.и 11 управления, шину 12 нулевого потенциала и шину 13 питания.

Устройство работает следующим образом.

На шины 10 и 11 подаются противо- 15 фаз ные управляющие сигналы.

Рассмотрим работу регистра сдвига, выполненного на р-канальных МДПтранзисторах (фиг. 1).

Питание регистра сдвига осуществля-Щ ется ат источника напряжения отрицательной полярности (источник подключен к шине 13 питания).

* В режиме хранения информации на вторую шину 11 управления подается отрицательное напряжение, поддерживающее в открытом состоянии второй согласукщий элемент 4 и ключи б и 7, а на первую шину 10 управления подается напряжение, величина которого близка к нулю, удерживающее первый согласующий элемент 3 в закрытом состоянии. При этом второй инвертор 2 находится в рабочем состоянии и образует с первым инвертором 1 триггер с непосредственными связями, а выход третьего инвертора 5 подключен к, вы; ходу первого инвертора 1..

С приходом управляющих сигналов на первую и вторую шины 10 и 11 уп.равления: (на первую шину 10 посту- 40 пает импульс отрицательной полярности, а на вторую шину 11 — нулевой сигнал), согласующий элемент 4 закрывается и отключает вход третьего инвертора 5 от выхода первого инверто- ра 1, ключи б и 7 также закрываются и отключают соответственно управляющий и нагрузочный транзисторы второго инвертора 2 от входа первого инвертора 1, а согласукщий эле- О мент 3 включается. При этом через открытый согласукщий элемент 3 входное напряжение поступает на вход первого инвертора 1 и переводит его в новое логическое-.состояние или подтверждает его предыдущее состояние. Так как управляющий .и нагрузочный транзисторы второго инвертора 2 отключены, то напряжение на выходе второго инвертора 2 устанавливается равным напряжению на входе первого gp инвертора 1 раньше, чем у известного устройства на величину задержки ча его втором инверторе 2.

При снятии управляющих сигналов с шин 10 и 11 управления, первый согласующий элемент 3 . закрывается, а второй согласующий элемент 4 и ключи б и 7 открываются и квазистатический триггер, выполненный на инверторах 1 и 2 переходит в режим хранения информации, При построении регистра сдвига на допрлнякщих МДП-транзисторах,в квазистатическом триггере, выйолненном на инверторах 1 и 2, нагрузочные транзисторы инверторов 1 и 2 выполняются п-канальными, а их затворы соединяют с соответствующими .затворами управляющих транзисторов своих инверторов (фиг. 2). При использовании в качестве ключей б и 7 МДП-транзисторов с одинаковым типом проводимости. канала, например с каналом р-типа, максимальное напряжение на выходе второго ин.вертора. 1 по абсолютной величине ниже величины напряжения источника питания на величину порогового напряжения

МДП-транзистора на котором выполнен ключ 6. Это исключает возможность использования регистра сдвига при низких питающих напряжениях.

Для обеспечения возможности ис-. пользования регистра сдвига, выполненного на дополняющих МДП-транзисторах, при низких питающих напряжениях ключ б выполнен на и-канальном МДПтранзисторе (фиг. 2), а его затвор подключается к первой шине 10 управления. При таком включении ключи б и 7 одновременно открываются и закрываются, обеспечивая функционирование устройства подобно квазистатическому триггеру на транзисторах одного типа проводимости.

Электронные устройства выполненные на дополняющих МДП-транзисторах, в статическом состоянии мощности почти не потребляют.. Основное потребление мощности имеет место только в динамическом режиме при переходе инверторов из одного состояния в другое за счет протекания сквозных токов. В предложенном элементе памяти для регистра сдвига второй инвертор 2 во время действия управляющих (тактавых) сигналов отключается. Таким образом, в каждом квазистатическом триггере регистра сдвига мощность в основном потребляется только первым 1 и третьим инверторами 3, что дает в экономию в мощности потребления окало 30% по сравнению с известным устройством, выполненным на дополняющих МДП-транзисторах

Время установления квазистатического элемента памяти для регистра сдвига меньше, чем у известного устройства на величину задержки на его Втором инверторе, что соответствует повышению быстродействия почти в 1,4 раза.

Предложенный элемент памяти для .регистра сдвига можно реализовать и

832600 интегральном исполнении на основе любой технологии МДП-структур.

Формула изобретения

Элемент памяти для регистра сдви5

ra, содержащий квазистатический триггер, выполненный на двух инверторах, вход первого из которых соединен через первый согласующий -элемент со входом элемента памяти, третий инвертор, вход которого соединен через второй согласующий элемент с выходом первого инвертора, выход третьего ннвертора подсоединен к выходу элемента памяти, управлякщие -входы согласую- 15 щих элементов соединены соответствен но с первой и. второй шинами управления, от ли чающий ся тем, что, с целью повышения быстродействия элемента памяти и уменьшения потребляемой им мощности, в него введены два ключа, управлякщие входы которых подсоединены к шинам управления, первые выходы ключей соединены со входом первого инвертора, вторые выходы ключей соединены соответственно с выходами второго инвертора.

Источники информации, принятые во внимание при экспертизе

1. Заявка Японки Р 41-51612, кл. H 03 К 3/12, опубл. 1966.

2. Заявка Японии Р 45-4128, кл. Н 03 К 3/12, опубл. 1970.

3. Заявка Японии Р 45-7263, кл. Н 03 К 17/00, опубл. 1970 (протогип).

832600

Фиг. 2

Заказ 3421/45

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель A. Воронин

Редактор с. Патрушева Техред т ° маточка Корректор В.синицкая