Устройство для контроля блоковоперативной памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических республик

< 832603

=®

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 170779 (21) 2795993/18-24 с присоединением заявки ¹ (23) Приоритет— (Опубликовано 230581. Бюллетень Н9 19

Дата опубликования описания 25,0581 (5i) . g„

G 11 С 29/00

Государственный комитет

СССР по дедам изобретений и открытий (53) УДК б81. З27 (088.8) фу р

Г. И, Белов, К. И. Дид енк о Л. В. Де буновй4" (®ДХу „ и В. A. Сирченко 1, .),!,47,.»

" .1,: ; .!: r» .

6 -.-ф (72) Авторы изобретения

Специальное конструкторское бюро си управления и Харьковский ордена Лен институт им. В. И; Лени (71) 3 аявители (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ОПЕРАТИВНОЙ

ПАМЯТИ

10

Изобретение относится к запоминаю- щим устройствам.

Известно устройство для контроля блоков оперативной памяти, содержащее 5 адресный блок, блок формирования данных, блок управления, счетчик, реги стры и блок сравнения t1).

Недостатком этого устройства является низкая надежность.

Наиболее близким к предлагаемому техническим решением является устройство, содержащее блок формирования теста, подключенный к блоку управле ния, блок контроля считанной информа- 15 ции, первые входы которых подключены ко входу устройства, первый счетчик, один из выходов которого соединен со входом второго счетчика, блок сравнения., первый вход которого подключен 20 к.другому выходу первого счетчика, третий счетчик, вход. которого под.— ключен к выходу второго счетчика, а выходы соединены соответственно со вторым входом блока сравнения и одним из входов блока управления, вторые входы блоков контроля считанной информации подключены .к выходам бло ка сравнения и блока управления выхо. ды блоков контроля считанной информа- 30 ции соединены с другими входами блоков управления (2).

Недостатками этого устройства яв" ляются примэнение в нем длинных тестов.для обнаружения константных логических.неисправностей, отсутствие проверки схемы выбора кристалла полупроводникового накопителя и большие аппаратурные затраты для реализации устройства, что снижает быстродействие, точность контроля и надежность устройств а.

Цель изобретения — по в ьше ние точности контроля, быстродействия и надежности устройства.

-Поставленная цель достигается тем, что в устройство для контроля блоков оперативной памяти, содержащее формирователь тестовых сигналов, счетчик, блок управления, блок индикации, и схему сравнения, причем одни из входов блока индикации подключены соответственно к первому входу схемы срав" нения и входу устройства, к выходу схемы сравнения и первому входу блока управления, ко второму входу схемы сравнения, выходу формирователя.тестовых сигналов и контрольному выходу устройства, другие входы блока индикации подключены к адресным выходам

832603 устройства, один из которых соединен со вторым входом блока управления, первый, второй и третий выходы блока управления подключены соответственно ко входу формирователя тестовых сиг налев, управляющему выходу устройства и ко входу счетчика, введены блок свертки по модулю два, коммутаторы и элемент з адержки, причем одни. из входов блока свертки по модулю два под1 ключены к одним из выходов счетчика, первые входы одних иэ коммутаторов соединены с выходом блока свертки по модулю два, а первые входы других

c....одними из входов счетчика, вторью входы коммутаторов подключены соответственно к другим выходам счетчика, другой вход блока свертки по модулю два и третьи входы коммутаторов соединены соответственно с четвертым и с пятым выходом блока управления, выходы коммутаторов подключены сост- 20 ветственно к адресным выходам устройства, вход элемента задержки соединен со вторым выходом блока управления, а выход — с третьим входом схемы сравнения. 25

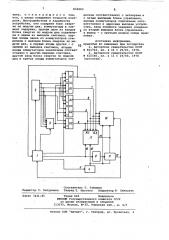

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит блок 1 управления, счетчик 2, служащий для формирования старших разрядов кода адреса, блок 3 свертки по модулю два, служащий для формирования младшего разряда кода адреса, формирователь 4 тестовых сигналов, имеющий вход 5, коммутаторы 6.1 и 6.2, имеющие выходы

7 и 8 соответственно, элемент 9 задер жки, блок 10 индикации, схему 11 сравнения с выходом 12, вход 13 устройства, адресные выходы 14.1 и 14.2 контрольный 15 и управлякщий 16 вы ходы устройства. Одни иэ входов блока 40 индикации 10 подключены соответственно к первому входу схемы 11 сравнения и входу 13 устройства, к выходу 12 схемы 11 сравнения н первому входу блока| 1 управления ко второмУ входу 45 схемы 11 сравнения„ выходу формирователя 4 тестовых сигналов и контрольному выходу 15 устройства. Другие входы блока 10 индикации подключены к адресным выходам 14.1 и 14.2 уст- щ ройства, один из которых соединен со вторым входом блока 1 управления.

Первый, второй и третий выходы блока

1 управления подключены соответственно ко входу формирователя 4 тестовых сигналов, к управляющему выходу 16 устройства и ко входу счетчика 2.

Одни из входов блока 3 .свертки по юдулю два подключены к выходам счетчика 2. Первые входы одних иэ коммугаторов 6,1 и 6.2 соединены с выхо- 60

qoM одних из коммутаторов 6.1 и 6.2 соединены с выходом блока 3 свертки по модулю два; а первые входы других коммутаторов 6.1 и 6.2 с одними из выходов счетчика 2. Вторые входы коммутаторов 6.1 и 6.2 подключены соответственно к другим выходам счетчика

2. Другой вход блока 3 свертки по модулю два и третьи, входы коммутаторов б .1 и б .2 соединены соответственно с,четвертым и с пятым выходами блока 1 управления. Выходы 7 и 8 коммутаторов 6.1 и 6.2 подключены соответственно к адресным выходам 14.1 и

14.2 устройства. Вход элемента 9 задержки соединен со вторым выходом блока 1 управления, а выход - с третьим входом схемы 11 сравнения. Адресные выходы 14.1 и 14.2 устройства подключаются соответственно к адресным входам и ко входам выбора кристалла контролируемого блока 17 оперативной памяти. Контрольный 15 и управляющий 16 выходы и вход 13 устройства подключены к соответствующим входам и выходу контролируемого блока. 17 оперативной памяти.

Устройство работает следующим образ.ом.

В исходном состоянии счетчик 2 устанавливается,в нулевое состояние.

На втором и четвертом выходах блока

1 управления формируется сигнал логическая единица.

После пуска устройства в первом цикле контроля счетчик 2 и блок 3 свертки по модулю два генерируют первое подмножество адресов A причем на выходе блока 3 свертки по модулю два формируется логический сигнал нуль, если число единиц кода счетчика 2 четно, и логическая единица, если число единиц в коде счетчика 2 нечетно.

При этом, в зависимости от технической реализации контролируемого блока 17 оперативной памяти, в первое подмножество А ячеек записывает тестовый код, содержащий единицы или нули во всех разрядах. Генерация тестового кода обеспечивается формирователем 4 тестовых сигналов. Первый цикл контроля .заканчивается при появлении отрицательного фронта сигнала на.входе одного из коммутаторов

6.1, с выхода 7 которого сигнал поступает на второй вход блока 1 управления. При этом количество ячеек, в ко торых записан тестовый код, определяется по формуле +К -1

2 где Ь вЂ” число. разрядов в .коммутаторе

6.1, блокируемых при выборе кристалла контролируемого блока оперативной памяти;

k — число разрядов в коде адреса выбора кристалла.

В начале второго цикла контроля блок 1 управления устанавливает счетчик 2 в нулевое состояние и на четвертом выходе блока 1 управления формирует логический нуль, затем с

832603 третьего выхода блока 1 управления на вход счетчика 2 поступают импульсы, при этом счетчик 2 и блок 3 сверт\. ки по модулю два генерируют .второе подмножество адресЬв A причем формируется логический ноль, если ° число единиц кода счетчика 2 нечетно, и логическая единица, если число единиц в коде счетчика 2 четно.

Во второе подмножество ячеек записывается тестовый код, содержащий . нули (единицы) во всех разрядах.

В третьем и четвертом цикле контроля считывается информация с ячеек контролируемого блока 17 оперативной памяти в порядке ее записи, для чего на втором выходе блока 1 управления 15 формируется логическая единица. Считанная информация сравнивается с эталонной в схеме 11 сравнения, .для чего формирователь 4 тестовых сигналов генерирует эталонные тесты в той же Щ последовательности, как и при записи.

При несовпадении считанной информации с эталонным тестом схема 11 сравнения формирует на своем выходе 12 сигнал неисправности, который поступает в блок 1 управления и блок 10 индикации, причем блок 1 управления прекращает подачу импульсов на счетчик 2, а в блоке 10 индикации фиксируется и отображается информация о типе и месте неисправности.

В пятом цикле контроля единичный код записывается во второе А подмножество ячеек, для чего на четвертом выходе блока 1 управления формируется логический сигнал "0", сигнал записи на втором выходе блока 1 управления и логический сигнал "единица". на входе 5 формирователя 4 тестовых сигналов.

В шестом цикле контроля нулевой 40 код записывается в первсе A" подмножество ячеек, для чего блок 1 управления формирует логическую единицу на своем четвертом выходе и логический ноль на входе 5 формирователя 4 45 тестовых сигналов.

В седьмом и восьмом. цикле контроля блок 1 управления обеспечивает считывание информации первого и второго подмножества ячеек в порядке записи и сравнение ее с эталонной в схеме 11 сравнения. После успешного окончания восьмого цикла контроля заканчивается контроль схем выбора кристалла, контролируемого блока оперативной памяти, для осуществления которого потребовалось m = 4 2 обК+ Ь ращений к памяти.

Для дальнейшего контроля блока 17 оперативной памяти блок 1 управления устанавливает счетчик 2 в нулевое Я) состояние, затем подает логическую единицу на третьи входы коммутатора

6, тем самым подключает к старшим разрядам кода адреса выходы счетчика 2, а к младшему разряду — выход блока Я

3. На остальных выходах блока 1 управленияя уст анавлив аются те же си гналы, что и в первом цикле контроля. При этом генерируется третье подмножество адресов А, которому принадлежат все двоичные адреса с четным числом единиц в коде. Работа устройства в девятом цикле контроля аналогична работе устройства в первом цикле контроля.

В десятом цикле контроля на всех выходах, за исключением четвертого, блока 1 управления, формируются те же сигналы, что и .во втором цикле контроля. При этом генерируется четвертое подмножество адресов A,,которому принадлежат двоичные адреса с нечетным числом единиц в коде.

Дальнейшая работа устройства в десятом — шестнадцатом циклах контроля аналогична работе его в первых восьми циклах, за исключением того, что запись и считывание тестовой информации осуществляется по третьим А и четвертым А4 подмножествам адресов.

Таким образом, для обнаружения кон . стантных неисправностей в блоке оперативной памяти потребуется L обращений к памяти, определяемое по формуле

4N+ я

Технико-э кономические преимущества предложенного устройства заключают-. ся в том, что оно обеспечивает контроль схемы выбора кристалла контролируемого полупроводникового блока оперативной памяти, за счет чего повышена точность контроля, причем для реализации предложенного устройства требуется меньше аппаратурных затрат, чем для известного, за счет чего повышены быстродействие и надежность устройства.

Формула изобретения

Устройство для контроля блоков оперативной памяти, содержащее фор-. мирователь тестовых сигналов, счетчик, блок управления, блок индикации и схему сравнейия, причем одни из входов блока индикации .подключены соответственно к первому входу схемы сравнения и входу устройства, к выходу схемы сравнения и первому входу блока управления, ко второму входу схемы сравнения, выходу формирователя тестовых сигналов и контрольному выходу устройства, другие входы блока индикации подключены к адресно выходам устройства, один из которых соединен со вторым входом блока управления, первый, второй и третий выходы блока управления подключены соответственно ко входу Формирователя тестовых сигналов, к управляюще— му выходу устройства, и ко входу счет832603 Составитель Т. Зайцева

Редактор С. Патрушева. Техред T. Маточка Корректор В- Синицкая

Заказ 3421/45 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 чика, о т л и ч а ю щ е е с я тем, что, с целью повышения точности контроля, быстродействия и надежности . устройства, оно содержит блок свертки по модулю два, коммутаторы и элемент задержки;, причем одни из входов блока свертки по модулю два подключены к одним из выходов счетчика, первые входы одних из коммутаторов соединены с выходом блока свертки по модулю дaa a ep xo x с . 10 одними из выходов счетчика, вторые входы кбммутаторов подключены.:соответственно к другим. выходам. счетчика, другой вход блока свертки по модулю

:два и третьи входы коммутаторов сое8 динены соответственно с четвертым и с пятым выходами блока управления, выходы коммутаторов подключены соответственно к адресным выходам устройства, вход элемента задержки соединен со вторым выходом блока управления, а выход — с третьим входом схемы сравнения.

Источники информации, принятйе во внимание при экспертизе

1 Авторское свидетельство СССР

Ю 601762, кл . G 11 С 29/00, 1978.

2. Авторское свидетельство СССР

9 615546 кл. G 11 С 29/00, 1978 (прототип).