Устройство для передачи и приемасигналов дельта-модуляции

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапистическик

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 16.0779 (21) 279492.1/18-09

<„1832717,® (51)м. Кл.з

Н 03 К 13/22

H L 25/40 с присоединением заявки ¹

Государственный комитет

СССР

А0 делам изобретениИ н открытий (23) Приоритет (S3) ДК 621 ° 376. . 56 (088. 8) Опубликовано 2 3,05.8 1. Бюллетеиь ЙЯ 19

Дата опубликования описания 25,0581.., г,.

1

В. A. Геранин, Н. А. Мелешко, Г. Н. Розоринов-, Л, A. Середа и О.A. Янушевский !,,, !

Киевский ордена Ленина политехнический инс%Ътут» им. 50-летия Великой Октябрьской социалистической революции (72) Авторы изобретения (71) Заявитель (54) УСТРОЧСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ

ДЕЛЬТА-МОДУЛЯЦИИ

Изобретение относится к технике связи и может использоваться для передачи и приема аналоговых сообщений, выраженнЫх в дискретной форме.

Известно устройство для передачи и приема сигналов дельта-модуляции, содержащее на передающей стороне сдвигающий регистр и элемент И, первые входы которых объединены, а..выхрды элементов И подключены к входам сумматора, на приемной стороне — первый формирователь сигналов и первый элемент ИЛИ, первый вход которого соединен с выходом элемента И, к первому входу которого подключен выход триггера, тактовый вход которого соединен с вторым входом элемента И (1).

Однако известное устройство обладает недостаточной пропускной способностью, Цель изобретения — повышение пропускной способности.

Поставленная цель достигается тем, что в устройство, содержащее на передающей стороне сдвигающий регистр и элементы,И,первые входы которых объединены, а выходы элементов И под- . ключены к входам сумматора, на приемной стороне — первый формирователь сигналов и первый элемент ИЛИ, первый вход которого. соединен с выходом элемента И, к первому входу которого подключен выход триггера, тактовый вход которого соединен с вторым входом элемента И, на передающей стороне введены элемент .И-НЕ и статический регистр, выходы которого подключены к вторым и третьим входам элементов

И и элемента И-НЕ, первый вход которого соединен с первыми входами элементов И и тактовым входом статического регистра, к информационным входам которого подключены выходы сдвигающего регистра, при этом выход элемента И-НЕ соединен с соответствующим входом сумматора, а на приемной стороне введены второй формирователь сигналов и второй элемент ИЛИ, выход которого подключен к информационному входу триггера, причем вход второго формирователя сигналов соединен с входом первого формирователя сигналов, выход которого подключен к второму входу первого элемента ИЛИ и первому входу второго элемента ИЛИ, второй вход которого соединен с выходом второго формирователя сигналов.

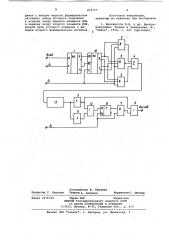

На чертеже изображена структурная электрическая схема предлагаемого устройства.

832717

Устройство содержит сдвигающий регистр 1, элементы 2 и 3 И, сумматор 4, первый формирователь 5 сигналов, первый элемент б ИЛИ, элемент

7 И, триггер 8, элемент 9 И-НЕ, статический регистр 10, второй формирователь 11 сигналов, второй элемент

12 ИЛИ, тракт 13 передачи.

Устройство работает следующим образом.

Информационный дельта-.модулированный сигнал 0в„, в котором единицы

10 представлены высокйми уровнями напряжения, а нули — низкими, поступает на вход сдвигающего регистра 1. На сйнхронизирующий вход сдвигающего регистра 1 подается тактовая синхропоследовательность 0 . В результате, на выходе первого разряда сдвигающе-. го регистра 1 формируется напряжение о

U<, а на выходе второго разряда — U задержанные относительно 0в на вре- 2ц мя, равное такту и двум тактам, соответственно. Сигналы 0 и U записыI ваются в статический регистр 10, а затем считываются из него с частотой, вдвое меньшей тактовой частоты. Для этого на синхронизирующий вход статического регистра 10 подается синхросигнал Ugg.

ЭлементЫ 2 и 3 И и элемент 9 И-НЕ представляют собой дешифраторы комбинаций "01", "11" и "10", соответственно, и информационной последовательности 0В . Например, на выходе элемента 2 И вырабатывается импульс

U< всякий раз, когда на единичном 35 выходе первого разряда статического регистра 10 присутствует высокий потенциал, а на единичном выходе второго разряда регистра — низкий. Импульсы, вырабатываемые элементом д»

9 И-НЕ, дешифратором комбинаций "11", дополнительно инвертируются. Сигналы .0 -U 9 суммируются на сумматоре 4, в резулътате чего образуется последовательность разнополярных импульсов 04., следующих с частотой, вдвое меньшей тактовой. Таким образом, сигнал 04 представляет собой дельта-модулированный сигнал, преобразованный по алгоритму

ОΠ— — 0

D1I +1

11 -1

Сигнал 04 поступает в тракт 13 передачи, после чего принимается на при Я емном конце и подается на входы пер-. ,вого и второго формирователей 5 и 11 сигналов. Второй формирователь 11 выделяет из сигнала 04 импульсы 04 положительной полярности, а первый фор- N мирователь 5 выделяет из сигнала 04 импульсы U отрицательной полярности, которые при этом дополнительно инвестируются. Импульсы Ug и U,ñíaìàå., мые с выходов первого и второго форми-15 рователей 5 и 11,смешиваются на вто- ром элементе 12 ИЛИ и подаются на информационный вход триггера 8. На инверсный синхронизирующий вход триггера 8 поступают синхроимпульсы 0у< тактовой частоты. На единичном выходе триггера 8 формируется напряжение

0в, задержанное относительно передних фронтов импульсов U, на время, равное длительности импульсов Ug< на элементе 7 И, в результате чего на выходе элемента 7 И формируются импульсы Uz, представляющие собой задержанные на такт импульсы 0<< . Импульсы 0> смешиваются с импульсами

0 на первом элементе б ИЛИ и поступают на вход устройства.

Описанные преобразования не являются Обратимыми и характеризуются дополнительными искажениями. Однако влияние этих искажений на качество перЕдачи сигнала относительно невелико, а применение соответствующих преобразований сигнала черезвычайно эффективно.

Технико-экономическая эффективность применения изобретения определяется повышением пропускной способности устройства, а также обеспечением вдвое меньшей частоты следования информационного сигнала по срав- . нению с известным устройством, при тех же необратимых искажениях.

Формула изобретения

Устройство для передачи и приема сигналов дельта-модуляции, содержащее на передающей стороне сдвигающий регистр и элементы И,первые входы которых объединены, а выходы элементов И подключены к входам сумматора, на приемной стороне — первый формирователь сигналов и первый элемент ИЛИ, первый вход которого соединен с выходом элемента И, к первому входу которого подключен выход триггера, тактовый вход которого соединен с вторым входом элемента И, отличающееся тем, что, с целью повиаения пропускной способности, на передающей стороне введены лементы И-НЕ и статический регистр, выходы которого подключенык вторым и третьим входам элементов

И и элемента И-НЕ, первый вход которого соединен с первыми входами элементов И и тактовым входом статического регистра, к информационным входам которого подключены выходы сдвигающего регистра, при этом выход элемента И-HE соединен с соответствующим входом сумматора, а на приемной стороне введены второй формирователь сигналов и второй элемент ИЛИ, выход которого подключен к информапионному входу триггера, причем вход второго формирователя сигналов сое832717 ход

Составитель И. Грачева

-Редактор Г. Кацалап Техред ь. Бакинец Корректор С. Шекмар

Заказ 347б/52 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР. по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 динен с входом первого формирователя сигналов, выход которого подключен к второму входу первого элемента ИЛИ и первому входу второго элемента ИЛИ, второй вход которого соединен с выходом второго формирователя сигналов.

Источники информации, принятые во внимание при экспертизе

1. Венедиктов N.Ä. и др. Дельтамодуляция. Теория и применение. М., "Связь", 1976, с. 223 (прототип).