Устройство тактовой синхрониза-ции

Иллюстрации

Показать всеРеферат

О П И С А Н И Е () 832758

ИЗОВРЕТЕН ИЯ

Союз CoQBTcKNK

Социалистичвскик

Реснублии

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт, свид-ву— (5l)M. Кл. (22) Заявлено 25. 06. 79 (21) 2807654/18-09

Н 04 L 7/02 с присоединением заявки М

Гоаударотееинмй комитет

СССР (23) Приоритет (53) УДК 621.394, .662(088.8) ло делам изебретеиий и открытий

Опубликовано 23.05.81; Бюллетень Ж19

Дата опубликования описания 05. 05 . 8 1 (72) Авторы изобретения

В.Н.Вучин и А И Доброскок (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к радиотехнике и может использоваться в системах передачи и- обработки дискретной информации.

Известно устройство тактовой син-. хронизации, содержащее на входе фазовый детектор, выход которого соединен через усредняющий блок с первым управляющим входом первого блока па мяти, последовательно соединенные

f0 задающий генератор, первый делитель частоты, формирователь сигналов фазовых зон и последовательно соединенные первый блок памяти, дешифратор, элемент ИЛИ, выход которого соединен

1$ .со вторым входом фазового детектора, управляющий вход формирователя сигналов фазовых эон подключен к информационному входу, управляющие входы дешифратора соединены с соответствующими выходами первого делителя частоты P 1.

Однако известное устройство имеет низкую помехоустойчивость.

Цель изобретения — повышение помехоустойчивости.

Поставленная цель достигается тем, что в устройство тактовой синхронизации, содержащее на входе фазовый детектор, выход которого соединен через усредняющий блок с первым управляющим входом первого блока папяти, последовательно соединенные задающий генератор, первый делитель частоты,.формирователь сигналов фазовых зон и последовательно соединенные первый блок памяти, дешифратор, элемент ИЛИ, выход которого соединен со вторым входом фазового детектора, управляющий вход формирователя сигналов фазовых зон подключен к информационному входу,,управляющие входы дешифратора соединены с соответствующими выходами первого делителя частоты, введены коммутатор, анализатор фазовой расстройки, вторые делитель час- . тоты и блок памяти, при этом управляющий вхоп второго блока памяти через

3 83 второй делитель частоты соединен параллельно первому делителю частоты, с выходом задающего генератора, первая группа информационных входов коммутатора параллельно информационным входам второго блока памяти соединена с выходами формирователя сигналов фазовых зон, вторая группа информаци, онных входов коммутатора соединена с информационными выходами второго блока памяти, первый управляющий вход коммутатора соединен с первым выхо.дом анализатора фазовой расстройки, группа выходов коммутатора подсоединена ко входам первого блока памяти, вход анализатора фазовой расстройки подключен параллельно входу усредняющего блока к выходу фазового детек- тора, а второй выход анализатора фазовой расстройки соединен со вторым управляющим входом первого блока памяти, причем выход усредняющего блока подключен к второму управляющему входу коммутатора.

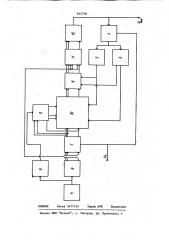

На чертеже представлена структурная электрическая схема предлагаемо.го устройства.

Устройство тактовой синхронизации содержит фазовый детектор 1, усредняющий блок 2, анализатор 3 фазовой расстройки, задающий генератор 4„ первый и второй делители частоты 5 и 6, соответственно, формирователь 7 сигналов фазовых зон, первый и второй блоки памяти 8 и 9, соответственно, коммутатор 10, дешифратор 11, элемент ИЛИ 12.

Устройство работает следующим образом.

При канале хорошего качества (слабый уровень помех ) в установившемся режиме сигналы Ц и U синфазны, фазоВик вый детектор 1 регистрирует отсутствие рассогласования, с выходов усредняющего блока 2 и анализатора 3 фаэовой расстройки поступают сигналы, по которым первый блок 8 памяти через коммутатор 10 подключен к формирователю 7 и находится в режиме запрета записи информации, т, е, в режиме хранения информации, при этом фаза колебаний )0,достается неизменной. При плавном расхождении по фазе колебаний 0 и0,фазовый детектор 1 вырабатывает соответствующий сигнал,, от которого срабатывает усредняющий блок 2, с выхода которого поступает сигнал, обеспечивающий подключение первого блока 8 памяти через комму2758 4 — татор 10 к формирователю 7, а также сигнал, разрешающий запись информа5

1О

55 ции. Код с выхода формирователя 7 че.рез коммутатор 10 записывается в первый блок 8 памяти, при этом создают-. ся условия для появления сигнала на том выходе дешифратора 11, при котором сигнал на выходе устройства синфазен с входным..В результате устройство переходит в режим удержания до нового плавного рассогласования.

При воздействии помех монотонность сигнала на выходе фазового детектора

1 маловероятна, поэтому срабатывает, как правило, усредняющий блок 2. Однако при этом с большой вероятностью возможна неправильная привязка сигнала Оо к фазовой зоне, обеспечиваемая формирователем 7. Учйтывая большой процент импульсных помех в проводных каналах связи,.наличие селективных замираний в радиоканалах, часты ситуации, при которых под воздействием помехи усредняющий блок 2 выдает сигнал расстройки, в результате чего записывать в блок 8 памяти номер фазовой зоны, в которую попадает фронт сигнала Uc, нельзя, так как с большой вероятностью фронт сдвинут под воздействием помех. Поэтому при срабатывании усредняющего блока 2 сигналом от данного блока по управляющим входам коммутатора 10 и первого блока

8 памяти первый из них подключает формирователь 7 к блоку 8 памяти через второй блок 9 памяти, и первый блок 8 памяти переходит в режим записи информации, которая с более высокой вероятностью отображает истинное положение фронта сигиала в одной из фазовых зон, так как это положение записано раньше, когда вероятность смещения фронтов сигнала Оо была меньшей. Применительно к канаду с малым уровнем помех и медленнымл изменением фазы входного сигнала это замедление практически не сказывается °

При воздействии помех более вероятной является выдача фазовым детектором нерегулярного по знаку и величине значения фазовой расстройки, поэтому в этих ситуациях более вероятным,является срабатывание усредняющего .блока 2, чем анализатора 3 фазовой расстройки, При доплеровском искажении частоты входного сигнала U быстрее сраба тывает анализатор 3, так как фазовая

Формула изобретения

5 8327 расстройка в этом случае монотонна по знаку и быстро увеличивается, Наличие в этом случае только усредняющего блока 2 с его инерционностью создавало бы условия для сбоя такто5 вой синхронизации, пропуска тактов> и следовательно„ условия для сбоя цикловой синхронизации оконечных устройств.

Менее инерционный анализатор 3 фаэовой расстройки обеспечивает более быструю подстройку тактовой частоты, которая достигается тем, что сигналом по соответствующему управляющему входу коммутатора 10 последний подключает первый блок 8 памяти непосредственно к формирователю 7, а сигналом, передаваемым по управляющему выходу анализатора 3, подключенно.му к управляющему входу первого блока 0

8 памяти, последний переходит в режим записи информации. В остальном работа .происходит порядком, описанным для случая канала связи со слабым уров нем помех.

Применение предлагаемого устройства тактовой синхронизации обеспечивает увеличение числа типов каналов связи, по которым оно может успешно работать. 30

Возможность использования устройства в каналах с шумами и с доплеровскими искажениями особенно ценна с точки зрения размещения устройств обработки дискретной информации на 35 подвижных объектах.

Устройство тактовой синхронизации, содержащее на входе фазовый детектор, выход которого соединен через усредняющий блок с первым управляющим входом первого блока памяти, последова- 45 рельно соединенные задающий генера58

r тор, первый делитель частоты, формирователь сигналов фаовых зон и последовательно соединенные первый блок памяти, дешифратор, элемент ЮИ, выход которого соединен со вторым входом фазового детектора, управляющий вход формирователя сигналов фазовых зон подключен к информационному входу, управляющие входы дешифратора соединены с соответствующими выходами первого делителя частоты, о т л и— ч а ю щ е е с я тем, что, с целью повьппения помехоустойчивости, введены коммутатор, анализатор фазовой расстройки, вторые делитель частоты и блок памяти, при этом управляющий вход второго блока памяти .через второй делитель частоты соединен параллельно первому делителю частоты с выходом задающего генератора, первая группа информационных входов коммутатора параллельно информационным входам второго блока памяти соеДинена с выходами формирователя сигналов фазовых зон, вторая группа информационных входов коммутатора соединена с информационными выходами второго блока памяти, первый управляющий вход коммутатора соединен с первым выходом анализатора фазовой расстройки, группа выходов коммутатора подсоединена ко входам первого блока памяти, вход анализатора фазовой расстройки подключен параллельно входу усредняющего блока к выходу фазового детектора, а .второй выход анализатора фазовой расстройки соединен со вторым управляющим входом первого .блока памяти, причем .выход усредняющего блока подключен к второму управляющему входу коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 594594., кл. Н 04 1. 7/02, 1978 (проиотип).