Определитель экстремумов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ lli 334547 (61) Дополнительное к авт. свид-ву (22) Заявлено 15.08. 79 (21) 2809572/18-21 с присоединением заявки,ре (23) Приоритет (Sl)M. Кл.

G 01 R. 19/Оя

3Ъоударотваииый комитет

СССР (S>) УДК 621.317..7(088.8) де делам изобретеиий и открытий

Опубликовано 30.05.81, Бюллетень .% 20

Дата опубликования описания 02.06.81 (72) Авторы изобретения

Бе К. Куприк и А. И. Двойниченко (71) Заявитель (54) ОПРЕДЕЛИТЕЛЬ ЭКСТРЕИУИОВ

Изобретение относится к электро"

1измерительной технике.

Известны определители экстремаль- ных значений напряжения, содержащие элемент памяти (например, конденсатор), подключенный через ключ к источнику входного сигнала в момент времени, определяемый датчиком момента экстремума (1).

Погрешность известных устройств значительна и зависит от способности ю длительного хранения, запомненного напряжения элементом памяти, точности определения момента экстремума и времени, в течение которого элемент па15 мяти через ключ подключается к источнику сигнала.

Наиболее близким техническим решением к предлагаемому изобретению является устройство, содержащее ключевую схему, подключенную к запоминающему конденсатору и источнику преобразуемого напряжения, в котором есть экстрематор, дифференцирующий элемент

2 и одновибратор, причем вход экстрематора подключен к источнику преобразуемого напряжения, а выход соединен со входом дифференцирующего элемента, вход которого подключен к одновибратору, соединенному с ключевой схемой (21.

Однако устройству присущи значительные погрешности.

Цель изобретения — повьопение точности (определения экстремального значения напряжения).

Указанная цель достигается . тем, что в определитель экстремумов, содержащий дифференциатор, к выходу которого подключен компаратор, ключ, к выходу которого подключен элемент памяти, и блок управления, подключенный к управляющему входу ключа, введены дополнительный дифференциатор, второй компаратор, сумматор, блок преобразования и модулятор, причем первый вход . сумматора соединен со входом дифференциатора и входом ключа, второй вход

3 83454 соединен с выходом модулятора, соединенного своим первым входом с выходом дифференциатора, выход сумматора через последовательно включенные дополнительный дифференциатор и второй компара5 тор подключен к первому входу блока управления, второй вход которого соединен с выходом компаратора и входом блока преобразования, выход которого подключен ко второму входу модулятора. 1в

Блок преобразования выполнен из последовательно включенных источника постоянного напряжения, двух интеграторов и фильтра, причем с выходом блока преобразования соединен выход 15 фильтра, а со входом блока преобразования соединены входы управления интеграторов.

Блок управления выполнен из двух инверторов и трех элементов И-НЕ, при- 2, чем с выходом блока управления соединен выход первого элемента И-НЕ, входы которого. соединены с выходами двух других элементов И-НЕ, входы одного из которых соединены со входами блока управления непосредственно, à sxoды другого элемента И-НЕ соединены со входами блока управления через инверторы.

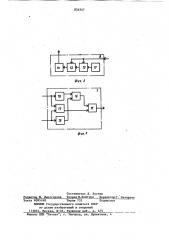

На фиг. 1 изображена структурная схема определителя; на фиг. 2 — структурная схема блока преобразования; на фиг. 3 — структурная схема блока управления.

Определитель экстремума состоит из дифференциатора 1, сумматора 2, ключа 3, элемента 4 памяти, дополнительного дифференциатора 5, второго компаратора 6, блока 7 управления, блока 8 преобразования, компаратора 9 40 и модулятора 10. Выходом определителя является выход элемента 4 памяти.

Блок 8 преобразования состоит из последовательно соединенных источника II постоянного напряжения, интегра-45 торов 12 и 13 и фильтра 14. Входы уп равления интеграторов 12 и 13 соединены параллельно и являются входом блока 8 преобразования, а его выходом является выход фильтра 14.

50, Блок 7 управления состоит из элементов 15-17 И-НЕ и инверторов 18 и

19, выходом блока 7 управления является выход элемента 15 И-HE,âõoäû которого-соединены с выходами элементов 16 и 17 И-НЕ.Входы элемента 17 И-НЕ являются входами блока 7 управления,а выходы элемента 16 И-НЕ соединены с эти7 4 ми входами через инверторы 18 и 19.

Компараторы 6 и 9 работают в режиме сравнения сигнала с нулевым уровнем.В их роли могут быть использованы усилители, работающие в режиме ограничения и имеющие большой коэффициент усиления. Модулятор 10 выполняет операцию умножения входных сигналов.

Устройство работает следующим образом.

Из входного сигнала устройства, продифференцированного дифференциатором 1, компаратор 9 формирует импульcbl напряжения, когда сигнал íà его входе имеет определенную полярность.

Передними фронтами этих импульсов устанавливаются в начальное состояние интеграторы 12 и 13. На вход интегратора 12 подается постоянное напряжение U . Фильтр 14 выделяет постоян11 ную составляющую напряжения Uly на выходе интегратора 13, прямо пропорциоI нальную усредненному значению величи ны периодов повторения сигналов на выходе основного дифференциатора 1.

Модулятор 10 формирует на выходе напряжение U®, прямо пропорциональное произведению от входного сигнала на усредненное значение, периода повторения сигналов на выходе основного дифференциатора 1. В результате на вы-. ходе сумматора 2 формируется сигнал, опережающий по фазе сигнал на входе устройства.

Выходной сигнал сумматора 2 дифференцируется дополнительным дифференциатором 5. На выходе компаратора 6 формируются импульсы напряжения, г когда сигнал на его входе имеет определенную полярность. Блок 7 управления формирует на своем выходе импульсы напряжения U, когда сигналы на. выходах компараторов 6 и 9 различны по своей величине. Импульс1ы U открывают ключ 3, при этом на элемент 4 памяти подается входной сигнал устройства. Импульс 0> начинает" ся до экстремального значения сигнала и оканчивается в момент достижения входным сигналом экстремального значения.

Таким образом, в элементе 4 памяти запоминается экстремальное значение.

Положительный эффект заключается в повышении точности, достигаемой за счет того, что элемент памяти ,включается незадолго до момента экст,ремума и отключается от входного сиг5 . 83454 нала в момент экстремума. При этом конечное значение напряжения, запом ненное элементом памяти, равно экст- ремуму.

В известных устройствах включение

5 элемента памяти производится в момент. экстремума, а отключение их от вход.ного сигнала — через некоторый кромежуток времени после него. При этом конечное значение напряжения, запомненное элементом памяти, отличается от экстремалвного. Изобретение одновременно позволяет расширить частотный диапазон измерения, так как длительность импуль- 15 са, в течение которого элемент памяти подключен к входному сигналу, адаптирована к исследуемому сигналу.

Формула изобретения

Источники информации, нринятые во внимание при экспертизе

1. Нетретбенко К.А. Компенсацион" ные схемы амплитудных вольтметров и указателей экстремума. M., "Энергия", 1967 с. 14-51.

2. Авторское свидетельство СССР

У 368550, кл. 6 01 и 19/22, 1970.

1. Определитель- экстремумов, содержащий дифференциатор, к выходу которого подключен компаратор, ключ, 25 к выходу которого подключен элемент памяти, и блок управления, подключенйый к управляющему входу ключа, о тл и ч а ю шийся тем, что, с целью повышения точности, в него введе- рф ны дополнительный дифференциатор, второй компаратор, сумматор, блок преобразования и модулятор, причем первый вход -сумматора соединен со sxoдом дифференциатора и входом ключа, второй вход соединен с выходом модулятора, соединенного своим первым входом с выходом дифференциатора, выход

7 Ь сумматора через последовательно включенные дополнительный дифференциатор и второй компаратор подключен к первому входу блока управления, второй вход которого соединен с выходом компаратора и входом блока преобразования, выход которого подключен ко второму входу модулятора.

2. Устройство по п. 1 о т л и ч аю щ е е с я тем, что блок преобразования выполнен из последовательно включенных источника постоянного напряжения, двух интеграторов и фильтра, причем с выходом блока преобразования соединен выход фильтра, а со входом блока преобразования соединены входы управления интеграторов.

3. Устройство по и. 1, о т л и ч аю щ е е с я тем, что блок управления выполнен из двух инверторов и трех элементов И-Н5, причем с выходом блока управления соединен выход первого элемента И-НЕ, входы которого соединены с выходами двух других элемен- . тов И-НЕ, входы одного из которых со" единены со входами блока управления, непосредственно, а входы другого элемента И-НЕ соединены со входами блока управления через инверторы.

834547

Составитель В. Костин

Ре акто И. Лысогорова Техред И.Коштура КорректорГ. Наза ова

Заказ 4095 68 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и .открытий ..

ll3035, Москва Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4