Измеритель сдвига фаз

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски и

Социалистических

Рес убпнк (и)834593 (61) Дополнительное к авт. санд-ву -741186 (22) Заявлено 1О ° 07. 79 (21) 2795337/18-21 (5! )М. Кл. с присоединением заявки М—

6 01 R 25/00

Ркудеретееииыб кеюитет

СССР ее делаю изебретеиий и етерытий (23) Приоритет— (53) УД К 62! . 317.

77(088.8) ОпУблнковано 30. 05. 81 ° Бюллетень,кб 20

Дата опубликования описания 30. 05. 81 (72) Авторы изобретения (54) ИЗМЕРИТЕЛЬ СДВИГА ФАЗ

Изобретение относится к радиоизмерительной технике и может быть использовано при измерении сдвига фаз между двумя гармоническими сигналами, один из которых искажен шумами, а также гармоническими составляющими.

По основному авт.св. 1Е 741186 известен измеритель сдвига фаз, содержащий стробоскопический и аналогоцифровой преобразователи, два перемножителя, два сумматора с регистратО ми, вычислительный блок, синхрониэирующий блок, делитель частоты, дешифратор, постоянный запоминающий элемент и формирователь fl).

Недостатком известного измерителя сдвига фаз является ограниченный динамический диапазон сигнала по измерительному входу. Причина этого saключается в том, что в диапазоне амплитуд сигнала Цтн&ЮюИ-порядка (1-50)

AU<, где Ь0сти — значение ступеньки — кванта АЦП, работоспособность устройства нарушается.

В известном измерителе сдвига фаз дешифратор, делитель частоты, формирователь и синхрониэирующий блок выполняют функцию формирования импульсов, под воздействием которых производятся отсчеты мгновенных значений входного сигнала. Поскольку формирование таких импульсов возможно различными путями, то целесообразно. впредь объединить все эти блоки в один под названием синхронизирующий блок" °

Цель изобретения — расширение динамического диапазона входных сигналов по измерительному входу.

Поставленная цель достигается тем, что в измеритель сдвига фаз, содержащий стробоскопический и аналогоцифровой преобразователи, два перемножителя, два сумматора с регистрами, вычислительный и синхронизирующий блоки, постоянный запоминающий элемент, вводятся последовательно соединенные аналоговый коммутатор, циф/

3 8345 роаналоговый преобразователь, регистр памяти, вычитающий блок и элемент И, причем аналоговый коммутатор подключен к аналого-цифровому преобразователю, выход которого соединен с ре5 гистром памяти и с вычитающим блоком,. а элемент И соединен с регистром памяти и синхронизирующим блоком.

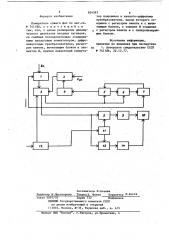

На чертеже приведена структурная схема измерителя сдвига фаз. 10

Устройство содержит последовательно включенные стробоскопический преобразователь 1, аналоговый коммутатор 2, аналого-цифровой преобразователь 3, последовательно включенные цифроаналоговый преобразователь 4, регистр 5 памяти, вычитающий блок 6 и элемент И 7, последовательно вклю- . ченные перемножитель 8, сумматор с регистром 9 и вычислительный блок 10. 20

Постоянный запоминающий элемент

ll соединен с синхронизирующим блоком

12, перемножителем 13 и сумматором с регистром 14.

Устройство работает следующим об25 разом.

На измерительные входы поступают напряжения с измеряемым фазовым сдвигом. Стробоскопический преобразователь

1 осуществляет квантование сигнала со

30 входа по времени и запоминанию мгновенного значения сигнала в момент стробирования (квантования), Напряжение с выхода стробоскопического преобразователя носит ступенчато-си35 нусоидальный вид. Напряжение каждой ступеньки дискретизируется, т.е. превращается в цифровой код аналого-цифровым преобразователем 3. Запуск стробпреобразователя 1 и АЦП 3 осущест40 вляется импульсами с выхода синхронизирующего блока 12. Таким образом, на выходе АЦП 3 существует последовательность кодов, отображающих мгно45 венное значение входного сигнала.

Устройство работает в два этапа.

На первом этапе производят выбор максимального за период входного сигнала значения кода АЦП 3. В первом этапе аналоговый коммутатор 2 подклю50 чает к АЦП 3 опорное напряжение.

Поиск максимального значения кода, соответствующего амплитуде входного сигнала, осуществляется узлами 5-7, 55

В регистре 5 памяти хранится значение отсчета в предыдущей точке Х.1 „ . Вычитающий блок 6 осуществляет операцию X „ -Х„ 4и анализ разности. Если

93 4. Х„-Х.; q> p т. е. Х„> Х 14, то на эле мент И 7 подается разрешение и Х.; записывается а регистр 5 памяти. Если (p„то в регистре сохраняется Х„., . Таким образом происходит выявление максимального кода за период.

На этом первый этап .заканчивается.

Во втором этапе Х <, как и все

Х4, преобразуется цифроаналоговым преобразователем (ЦАП) в напряжение, примерно равное U . Аналоговый коммутатор 2 подключает ЦАП 4 к АЦП 3. Зто приводит к тому, что значение кванта ступеньки АПП 3 изменяется таким образом, что амплитудное значение входного сигнала представляется теперь уже максимальным кодом во всем динамическом диапазоне.

Во втором этапе работа узлов 6 и

7 блокируется, т.е. в регистре 5 памяти хранится Х < äî конца времени измерения, Аналоговый коммутатор 2 подключается к источнику опорного напряжения только на время первого этапа, Фазометр обеспечивает измерение фазовых сдвигов в соответствии с алгоритмом где Х1 — отсчеты мгновенных значений входного сигнала;

ht — интервал квантования входного сигнала;

Й - количество отсчетов в одном из к периодов входного сигнала;

N частота входного сигнала. В постоянном запоминающем элемен-. те 11 хранятся коды, соответствующие значениям 51И 1(ЮМ и СО51(ЮМ . В сумматоре с регистром 9 накапливается значение числителя Х, а в сумматоре с регистром 14 — знаменателя у . Вычислительный блок 10 производит вычисление функции Огс 4д х/у и индикацию результата измерения.

Введение перечисленных элементов обеспечивает предлагаемому устройству возможность работы в широком динамическом диапазоне входных сигналов по измерительному входу. Так, например, для 7-разрядного АЦП динамический диапазон расширяется примерно в 2 раза.

Формула изобретения

Измеритель сдвига фаз по авт.св.

Р 741186, отличающийся тем, что, с целью расширения динамического диапазона входных сигналов, он снабжен последовательно соединенными аналоговым коммутатором, цифроаналоговым преобразователем, регистром памяти, вычитающим блоком и элементом И, причем аналоговый коммута834593 6 тор подключен к аналого-цифровому преобразователю, выход которого соединен с регистром памяти и с вычитающим блоком, а элемент И соединен с регистром памяти и с синхронизирующим блоком.

1 Источники информации, принятые во внимание при экспертизе

1в . l. Авторское свидетельство СССР

Ф 741186, 22.12.77.

Составитель Н.Агеева

Редактор М.Лысогорова Техред 3. Фанта Кор ектор M.KocTa

Заказ 4097/70 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-З, Раушская наб., д. 4/5

Филиал ППП "Патент, r.Óæãîðîä, ул.Проектная, 4