Устройство для порогового контроляуровня искажений вершины импульсногосигнала

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистичесиих

Республик 834612 (61) ДополнитеЛьное к авт. саид-ву(51)М. Кл. (22) Заявлено 27. 08. 79 (21) 2811063/18-21

G 01 R 29/02 с присоединением заявки ¹ (23)Приоритет,Геаударстааннвй квинтет

СССР аа делам нзабрвтаннй н ютхритнй

Опубликовано 30. 05. 81. Бюллетень,%20 (53) УДК621.317. ,325(088 ° 8) Дата опубликования описания10.0б.81 (72) Авторы изобретения

В,Т.Осьминин и В.С.Васильев

1 с Ф,, ) 1

1 (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПОРОГОВОГО КОНТРОЛЯ УРОВНЯ

ИСКАЖЕНИЙ ВЕРШИНЫ ИМПУЛЬСНОГО СИГНАЛА

Изобретение относится к электроизмерительной технике и может быть использовано в быстродействующих тестерах контроля параметров транзисторов.

Наиболее близким к предлагаемому изобретению по технической сущности является устройство для порогового контроля искажений вершины импульсного сигнала, содержащее блок памяти, блок суммирования, блок управления

10 памяти, блок сброса, компаратор и триггер $1).

Недостатком устройства является ограниченность функциональных возмож15 иостей. Устройство не обеспечивает возможности анализа искажений импуль сов любой полярности, не.позволяет производить анализ. искажений, имеющих вид одиночных выбросов.

20 Цель изобретения — расширение функциональных воэможностей.

Укаэанная цель достигается тем, что устройство для порогового контроля уровня искажений вершины импульсного сигнала, содержащее блок памяти, первый вход которого соединен с шиной исследуемого сигнала, первым входом блока суммирования, входом блока управления памятью и входом блока сброса, второй вход — с выхо- дом блока управления памятью, а выход со вторым входом блока суммирования и первым входом первого компаратора, выход которого подключен к первому входу триггера, установочный вход которого соединен с выходом блока сброса, снабжено вторым компаратором и инвертором, вход которого соединен с выходом блока памяти, а выход — с первым входом второго компаратора, второй вход которого подключен к выходу блока суммирования и второму. входу первого компаратора, а выход— ко второму входу триггера.

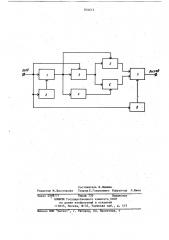

На чертеже представлена структурная электрическая схема устройства.

3 83461

Устройство состоит из блока 1 папяти, (операционного усилителя с коммутируемым входом, в цепи обратной связи которого включен запоминающий конденсатор), блока 2 управления памятью (одновибратора), блока 3 суммирования (операционного усилителя), инвертора 4, первого и второго компараторов 5 и 6, триггера 7 и блока

8 сброса. 10

Устройство работает следующим образом.

Исследуемый импульс поступает на входы блоков 1-3 и 8. Блок 2 управления памятью вырабатывает импульс, 15 задержанный относительно исследуемого на время, исключающее влияние переходных процессов, Этот импульс подается на второй вход блока 1 памяти и переводит его в режим запоминания zp . постоянного уровня исследуемого сиг« нала.и хранения этого уровня до окончания исследуемого сигнала.

Выходной сигнал блока 8 сброса переводит триггер 7 в одно иэ устой- 2s чивых состояний. Блок 3 суммирования осуществляет алгебраическое сложение исследуемого сигнала и сигнала, сформированного блоком 1 памяти, который имеет постоянный уровень и полярность 30 противоположную полярности исследуемого сигнала. В результате сложения выделяются усиленные искажения плоской вершины исследуемого импульса.

Компараторы 5 и 6 сравнивают сиг- 35 нал иСкажений с выходньм сигналом блока 1 памяти и инвертированньм сигналом на выходе блока 4, Действительное значение уровня искажений определяется аоотношением 40 — 1007, т

О0 где Оп — величина .абсолютного размаха искажений;

uO - величина постоянного уровня 45 исследуемого сигнала.

2 4

Если величина искажений превышает допустимое значение, задаваемое в процентном отношении коэффициентом усиления блока 3 суммирования, т. е. если К ) К, то срабатывает один из компараторов 5 или 6 и триггер 7 перебрасывается в другое устойчивое состояние.

Предлагаемое устройство позволяет обнаруживать искажения любой формы и длительность на вершинах импульсов любой полярности.

Формула изобретения

Устройство для порогового контроля уровня искажений вершины импульсного сигнала, содержащее блок памяти, пер- . вый вход которого соединен с шиной исследуемого сигнала, первым входом блока суммирования, входом блока .управления памятью и входом блока сброса, второй вход — с выходом блока управления памятью, а выход — со вторым входом блока суммирования и первым входом первого компаратора, выход которого подключен к первому входу триггера, установочный вход которого соединен с выходом блока сброса, о т— л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей,. оно снабжено вторым компаратором и инвертором, вход которого соединен с выходом блока памяти, а выход - с первым входом второго компаратора, второй вход которого подключен,к выходу блока суммирования и второму входу первого компаратора, а выход — ко второму входу триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке Â 2611621/01, кл. H 03K 5/00, 1978.

834612

Составитель В.Лившиц .

Редактор М.Лысогорова Техред Е.Гаврилешко Корректор Л,Иван

Заказ 409 71 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4