Функциональный преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

И ЗО6РЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ()834707 (61) Дополнительное к авт. свид-ву— (22) Заявлено 07.08.78 (21) 2653255/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G 06 F 15/353

Гоеударстеенный комитет

СССР

Опубликовано 30.05.81, Бюллетень № 20

Дата опубликования описания 05.06.81 (53) УДК 681.3 (088.8) по делам изобретений и открытий

В. Я. Хуторянский, Б. 3. Стеколь, П. И. С

Б. Ф. Дрозд, Б. В. Петрович, Г. Н. Рахимов, В. P. Холокйовск1тй," с

Б. П. Касич, В. Э. Штейнберг и P. Г. упов"(":- .--.,"с, с ( (72) Авторы изобретения (71) Заявитель (54) ФУНКЦИОНАЛЬНЫЛ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве специализированных вычислителей систем автоматического управления и контроля, в качестве линеаризаторов частотных сигналов, генераторов функциональных кривых и т.д.

Известно . устройство для воспроизведения функции а = а/х, в том числе у = Ф/х методом кусочно-линейной аппроксимации (1) .

Недостатком известного устройства яв- 10 ляется значительная неравномерность погрешности в различных участках диапазона.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее счетчик участков, дешифратор, блок памяти, делитель длины участка и управляемый делитель частоты, включающий счетчик, группу элементов И и элемент ИЛИ, причем вход счетчика соединен со входом устройства, первые входы элементов И группы соединены с разрядными выходами счетчика, вторые — с выходами блока памяти, а выходы — со входами элемента ИЛИ, выход которого соединен с выходом устройства, разрядные выходы счетчика участков через дешифратор подключены ко входам блока памяти (2).

Известное устройство уменьшает погрешность в начале интервала области определения, но увеличивает ее в конце.

Цель изобретения — повышение точности вычисления функции на концах области определения.

Поставленная цель достигается тем, что в устройство, содержащее счетчик участков, дешифратор, блок памяти, делитель длины участка и управляемый делитель частоты, включающий счетчик, группу элементов И и элемент ИЛИ, причем вход счетчика соединен со входом устройства, первые входы элементов И группы соединены с разрядными выходами счетчика, вторые — с выходами блока памяти, а выходы — со входами элемента ИЛИ, выход которого соединен с выходом устройства, разрядные выходы счет.чика участков через дешифратор подключены ко входам блока памяти, дополнительно введены три элемента И. элемент ИЛИ и триггер, вход которого ссединен с выходом первого элемента И, прямой выход подключен к первому входу второго элемента И, а

834707 инверсный — к первому входу третьего элемента И и управляющему входу счетчика участков, разрядные выходы которого сое-. динены со входами первого элемента И, второй вход второго элемента И подключен к выходу элемента ИЛИ управляемого делителя частоты, а выход через делитель длины участка соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, второй вход которого подключен к выходу счетчика управляемого делителя частоты, выход элемента ИЛИ соединен с информационным входом счетчика участков.

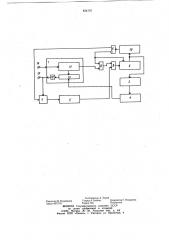

На чертеже приведена блок-схема устройства.

Устройство содержит управляемый делитель частоты 1, счетчик 2 участков, дешифратор 3, блок 4 памяти, делитель 5 длины участка, триггер 6, элементы И 7 8,схему 9 ИЛИ, элемент 10 И.

Управляемый делитель содержит счетчик 11. элемент 12 ИЛИ и группу элементов 13 И.

Устройство также имеет вход 14 и выход

15. В основу работы устройства положен принцип разбиения воспроизводимой зависимости с постоянным шагом hP до оси симметрии равнобочной гиперболы и с шагом йХ от оси симметрии, в этом случае объем запоминающего устройства уменьшается в два раза, так как одни и те же значения угловых коэффициентов используются дважды при воспроизведении обеих ветвей функции.

Устройство работает следующим образом.

В исходном состоянии триггер 6 устанавливается в единичное состояние, при котором отпирается элемент 7 И, а счетчик 2 участков фиксируется в режиме сложения.

При подаче на вход 14.устройства число-импульсной последовательности на выход управляемого делителя частоты 1 поступает выходная последовательность импульсов, поступающая непосредственно на выход 15 устройства и через элемент 7 И вЂ” на вход делителя 5 длины участков, определяющего шаг

АУ аппроксимации. При накоплении в счетчике 2 участков числа m, которое выбирается кратным степени 2, на входах элемента

10 .И устанавливаются единичные уровни, что вызывает появление сигнала на его выходе и переключение триггера 6 в нулевое положение, при котором запирается элемент 7 И, отпирается элемент 8 И и переводится в режим вычитания счетчик 2 участ5

1О ков. Устройство продолжает отрабатывать участок аппроксимации между m и (m-1) узлами, и начиная с (m -1) узла воспроизведение функции осуществляется с постоянным шагом dx. В момент окончания входной число-импульсной последовательности работа устройства заканчивается.

Сравнение предлагаемого устройства с известным показывает, что оно обеспечивает уменьшенную неравномерность погрешности при функциональном преобразовании частотно-импульсных сигналов, уменьшает аппаратурные затраты и улучшает характеристики устройства.

Формула изобретения

Функциональный преобразователь, содержащий счетчик участков, дешифратор, блок памяти, делитель длины участка и управляемый делитель частоты, содержащий счетчик, группу элементов И и элемент ИЛИ, О причем вход счетчика связан с входом устройства, первые входы элементов g груйпы соединены с разрядными выходами счетчика, вторые — с выходами блока памяти, а выходы — с входами элемента ИЛИ, выход которого соединен с выходом устрой25 ства, разрядные выходы счетчика участков через дешифратор подключены ко входам блока памяти, отличающийся тем, что, с целью повышения точности, в него введены три элемента И, элемент ИЛИ и триггер, вход которого соединен с выходом первого элемента И, прямой выход подключен к первому входу второго элемента И, а инверсный— к первому входу третьего элемента И и управляющему входу счетчика участков, разрядные выходы которого соединены со вхоз дами первого элемента И, второй вход второго элемента И подключен к выходу элемента ИЛИ управляемого делителя частоты, а выход через делитель длины участка соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом тре40 тьего элемента И, второй вход которого подключен к выходу счетчика управляемого делителя частоты, выход элемента ИЛИ соединен с информационным входом счетчика участков.

45 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 538367, кл. С 06 F 15/34, 1977.

2. Авторское свидетельство СССР № 376778, кл. G 06 F 7/26, 1971 (прототип).

834707

Составитель А. Зорин

Редактор Н. Кузнецова Техред А. Бойкас Корректор Г. Назарова

Заказ 4077/76 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по . делам изобретений и открытий

113035, Москва, K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул, Проектная, 4