Аналоговый интегратор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ сс 834Т1 4

Союз Советсимк

Социалистическмк

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 12.09.79 (2!) 2815882/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

G 06 G 7/186

Государстееиимй .комитет

СССР (53) УДК 681 335 (088.8) Опубликовано 30.05.81. Бюллетень № 20

Дата опубликования описания 05.06.81 по делам иэееретеиий и открытий (72) Авторы изобретеиия с

В. П. Морозов с (71) Заявитель

Ордена Ленина Институт проблем у1эралдеыня (54) АНАЛОГОВЫЙ ИНТЕГРАТОР

Изобретение относится к аналоговым вычислительным и измерительным устройствам, а более конкретно к интеграторам, широко используемым в таких устройствах для интегрирования аналоговых сигналов.

Известен аналоговый интегратор, состояший из операционного усилителя, входного резистора и конденсатора обратной связи (1).

Недостатками такого интегратора являются как увеличение ошибки интегрирования при уменьшении коэффициента усиления операционного усилителя, например, с ростом частоты входного сигнала, так и практическая невозможность оценить величину ошибки интегрирования входных сигналов сложной формы.

Последний недостаток устранен в интеграторе, который, кроме линейного решающего блока, в частности интегрирующего блока, содержит также усилитель сигнала ошибки, позволяющий выделить и оценить ошибку операции при любой форме входного сигнала. Интегратор является наиболее близким к предлагаемому (2).

Однако он имеет недостаточную точность и нтегр и рова н и я.

Цель изобретения — повышение точности интегрирования за счет вычитания сигнала ошибки из выходного сигнала интегратора и за счет сокращения числа операционных конденсаторов.

Указанная цель достигается тем, что в аналоговый интегратор, содержащий операционный усилитель, вход которого через первый масштабный резистор соединен с входом аналогового интегратора, первый интегрирующий конденсатор, включенный

10 между входом и выходом операционного усилителя, усилитель сигнала ошибки, инвертирующий вход которого через второй интегрирующий конденсатор соединен с его выходом, и масштабные резисторы, введены масштабный усилитель и резистивный дели тель, включенный между выходом усилителя сигнала ошибки и шиной нулевого потенциала, средний вывод резистивного делителя подключен к неинвертирующему входу масштабного усилителя, инвертирующий вход зэ которого через второй и третий масштабные резисторы соединен соответственно с. выходом масштабного усилителя, являющимся выходом аналогового интегратора и выходом операционного усилителя, вход кото834714

20

Формула изобретения ь Б/ (К(р) + 1), рого подключен к неинвертирующему входу усилителя сигнала ошибки, а инвертирующий вход усилителя сигнала ошибки через четвертый масштабный резистор соединен с шиной нулевого потенциала.

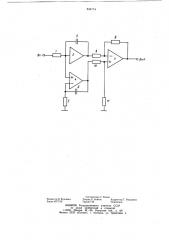

Ра чертеже представлена схема аналогового интегратора.

Аналоговый интегратор содержит масштабный резистор 1 и операционный усилитель 2 с интегрирующим конденсатором 3 в цепи обратной связи. Вход операционного усилителя 2 соединен с неинвертирующим входом усилителя 4 сигнала ошибки, инвертнрующий вход которого соединен с шиной нулевого потенциала через масштабный резистор 5 и с выходом усилителя через интегрирующий конденсатор 6 обратной связи.

Инвертирующий вход масштабного усилителя 7 с дифференциальными входами соединен с выходом операционного усилителя 2 через масштабный резистор 8 и с выходом устройства через масштабный резистор g обратной связи. Неинвертирующий вход масштабного усилителя присоединен к средней точке резистивного делителя из резисторов 10 и 11, включенного между выходом усилителя сигнала ошибки и шиной нулевого потенциала.

Предлагаемый интегратор работает следующим образом.

На выходе операционного усилителя 2 в процессе работы имеется сигнал, равный сумме точного значения интеграла от входного сигнала и сигнала ошибки, т.е. Ь +

+ 6 U. Указанная сумма, поступая на выход интегратора через масштабный резистор 8 и масштабный усилитель 7 с резистором 9 обратной связи, дает сигнал -MU> -Ма V, где М вЂ” коэффициент передачи масштабного усилителя.

Сигнал ошибки в суммирующей точке операционного усилителя равен где К(р) = 1/рТ вЂ” коэффициент передачи интегратора;

Т вЂ” его постоянная времени

Этот сигнал поступает на неинвертирующий вход усилителя 4, коэффициент передачи которого по этому входу равен, как и для любого дифференциального усилителя, обратной величине коэффициента передачи с выхода на инвертирующий вход. Но последний коэффициент равен рТ/(рТ + 1), где Тпроизведение сопротивления резистора 5 на емкость конденсатора 6, а сопротивления резисторов 1 и 5 так же, как и емкости конденсаторов 3 и 6, равны между собой.

С учетом всего изложенного напряжение на выходе усилителя сигнала ошибки составляет

Эо з5

4Р

55 (а@(«рГ+ !)).((р + 1)/р ) = д1/.

Делитель из резисторов 10 и 11 делит выходной сигнал усилителя 4 в отношении М/ (!"!+ 1), а коэффициент усиления масштабного усилителя по неинвертирующему входу, как легко подсчитать из отношения сопротивлений резисторов 8 и 9,равен М + 1. Поэтому с выхода усилителя 4 на выход устройства поступает сигнал, равный (Мь !1/

/(М + 1)) (М + 1), т.е. Ма U. Составляющие ошибки — Мь U и Мь U — на выходе устройства взаимно компенсируются, и остается точное значение интеграла -NU с масштабным коэффициентом -М (если необходимо, можно выбрать М = 1) . 3a счет такой компенсации, даже если вследствие малых погрешностей элементов устройства она будет неполной, точность интегрирования удается резко повысить.

Аналоговый интегратор, содержащий операционный усилитель, вход которого через первый масштабный резистор соединен с входом аналогового интегратора, первый интегрирующий конденсатор, включенный между входом и выходом операционного усилителя, усилитель сигнала ошибки, инвертирующий вход которого через второй интегрирующий конденсатор соединен с его выходом, и масштабные резисторы, отличающийся тем, что, с целью повышения точности интегрирования, в него введены масштабный усилитель и резистивный делитель, включенный между выходом усилителя сигнала ошибки и шиной нулевого потенциала, средний вывод резистивного делителя подключен к неинвертирующему входу масштабного усилителя, инвертирующий вход которого через второй и третий масштабные резисторы соединен соответственно с выходом масштабного усилителя, являющимся выходом аналогового интегратора и выходом операционного усилителя, вход которого подключен к неинвертирующему входу усилителя сигнала ошибки, а инвертирующий вход усилителя сигнала ошибки через четвертый масштабный резистор соединен с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

I. Коган Б. Я. Электронные моделирующие устройства и их применение для исследования системы автоматического регулирования. М., Физматгиз, 1963.

2. Морозов В. П. Методы измерения погрешности линейных аналоговых операций.«Известия Высших учебных заведений», сер. «Приборостроение», т. X!X, № 10, 1976 (прототип) .

834714

Вх.

Редактор Н. Бушаева

Заказ 4077/76

Составитель С. Белан

Техред А. Бойкас Корректор Г. Назарова

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4