Усилитель считывания

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<„,834764 (61) Дополнительное к авт. свид-ву (22) Заявлено 071278 (21) 2692869/18-24 с присоединением заявки HP (23) Приоритет

Опубликовано З00g81 Бюллетень HP

Дата опубликования описания 300581

Р1 М K 3

G 11 С 7/00

Государствеииый комитет

СССР по делам изо6ретеиий и открытий (5З) УДК 681.327.67 (088.8) В.И, Невядомский, С.И. Яровой, С.В. Курил нко, С.Н. Исаева и Т.Г. Гусева (72) Авторы изобретения!

I

) ! (71) Заявитель (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ

Изобретение относится к автоматике и вычислительной технике и предназначено для использования, в частности, в интегральных полупостоянных ЗУ.

Известен усилитель считывания, содержащий первый разрядный транзистор, затвор которого подключен к входу усилителя, и инвертор, состо- 1О ящий из зарядного и второго разрядного транзисторов, сток эарядного транзистора подключен к шине питания, затвор и исток соединен со стоком второго разрядного транзистора, исток которого соединен с шиной смещения. Кроме того, усилитель,содержит транзистор с обеднением, образующий истоковый повторитель с первым разрядным транзистором и два выходных транзистора, соединенных в пошпульный выходной каскад (11.

Недостатком данного усилителя является пониженное быстродействие, обусловленное тем, что транзистор с обеднением, подключенный к истоку первого разрядного транзистора, образует с ним истоковый повторитель и замедляет эа счет отрицательной

1обратной связи с выходом инвертора прием считываемой информации.

Если на затвор первого разрядного транзистора поступает логическая 1, то проводимость транзистора с обеднением уменьшается, что приводит к увеличению потенциала на истоке первого разрядного транзистора, который замедляет прием логической 1, а если поступает логический 0, то проводимость транзистора с обеднением возрастает, потенциал на истоке первого разрядного транзистора уменьшается, замедляя прием логического 0 .

Известен также усилитель считывания, содержащий два инвертора, в каждом иэ которых зарядный транзистор стоком соединен с шиной питания, исток зарядного транзистора первого инвертора соединен со стоком первого разрядного транзистора, затвор которого подключен к входу усилителя считывания. Исток зарядного транзистора второго инвертора соединен со стоком второго разрядного транзистора, затвор которого подключен к стоку первого разрядного транзистора, а исток соединен с истоком принимающего транзистора. Смещение на истоке первого разрядного транзистора обеспечивается транзистором, 834764 сток которого подключен к истоку первого разрядного транзистора, затвор соединен с шиной питания, а исток подключен к шине смещения (2).

Недостатком указанного усилителя считывания является отсутствие управляемого смещения" на истоке пер вого разрядного транзистора, что замедляет прием считываемой информации.

Наиболее близким к предлагаемому является усилитель считывания,содержащий три инвертора cQ встроенными нагрузками, причем затвор и исток зарядного транзистора первого инвертора соединен со стоком разрядного транзистора первого инвертора и с затвором разрядного транзистора второго инвертора,сток которого соединен с затвором и истоком зарядного транзистора второго инвертора,затвор и исток зарядного транзистора третьего 20 инвертора соединен со стоком разрядного транзистора третьего инвертора.

Кроме того, усилитель содержит выходные транзисторы, затворы которых соединены с выходами инверторов (3), 75

Недостаток известного усилителя в том, что положительный потенциал на истоке первого разрядного транзистора, равный напряжению смещения, замедляет прием логического 0, что приводит к уменьшению быстродействия и помехоустойчивости. Кроме того, технологический разброс порогового напряжения транзистора с обеднением уменьшает надежность данного усилителя считывания.

Цель изобретения — повышение быстродействия и помехоустойчивости усилителя считывания.

Поставленная цель достигается тем, что в усилитель считывания, 40 содержащий три инвертора, каждый иэ которых состоит из зарядного транзистора со встроенным каналом и иэ разрядного транзистора, сток которого соединен с затвором и исто- 45 ком зарядного транзистора со встроенным каналом, стоки зарядных транзисторов со встроенным каналом подключены к шине питания, истоки разрядных транзисторов объединены, затвор первого разрядного транзистора соединен с затвором третьего разрядного транзистора и подключен к входу усилителя, сток первого разрядного транзистора соединен с затвором второго разрядного транзистора,сток которого подключен к прямому выходу усилителя, сток третьего разрядного транзистора подключен к инверсному выходу усилителя, и коммутирующий транзистор, исток которого подключен d0 к шине смещения, а затвор — к шине управления, введены два согласующих транзистора со встроенными каналами сток первого из которых подключен к шине питания, затвор — к стоку 65 первого разрядного транзистора, а исток соединен с истоком первого разрядного транзистора и со стоком второго согласующего транзистора со. встроенным каналом, затвор и исток которого соединены со стоком коммутирующего транзистора.

В данном усилителе считывания доПолнительно введенные транзисторы за счет управления смещением истока первого разрядного транзистора создают благОприятные условия для приема каждого из логических уровней двоичной информации,в результате чего усилитель обладает более высокими быстродействием, помехоустойчивостью и надежностью, повышение которой обеспечивается также нейтрализацией технологических отклонений порогового напряжения транзисторов со встроенными каналами.

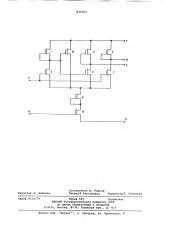

На чертеже изображена схема усилителя считывания.

Усилитель считывания содержит три инвертора, зарядными транзисторами 1-3 в которых являются МДПтранзисторы со встроенным каналом, стоки которых подключены к шине 4 питания. Исток и затвор зарядного транзистора 1 подключены к стоку первого разрядного транзистора 5 с индуцированным каналом и к затвору второго разрядного транзистора б с индуцированным каналом. Затвор транзистора 5 соединен с затвором третьего разрядного транзистора 7 с индуцированным каналом и подключен к входу

8, а исток его соединен с истоками разрядных транзисторов б и 7, стоки которых соответственно подключены к истокам и затворам зарядных транзисторов 2 и З.Сток разрядного транзистора б соединен с прямым выходом 9, а сток разрядного транзистора 7 — с инверсным выходом 10 .

Кроме этого, устройство включает два согласующих транзистора 11 и 12 со встроенными каналами, причем сток транзистора 11 подключен к шине 4 питания, а затвор — к стоку транзистора 5. Исток транзистора 11 соединен с истоком транзистора 5 и стоком транзистора 12, затвор и исток которого подключены к стоку коммутирующего транзистора 13 с индукцированным каналом, затвор которого соединен с шиной 14 управления, а исток — с шиной 15 смещения.

Устройство работает следующим образом.

Для включения усилителя считывания на шину 14 управления подается напряжение логической 1 (например сигнал из дешифратора адреса или сигнал Выбор ИС ), открывающее транзистор 13. Емкостная нагрузка первого инвертора намного меньше емкостной нагрузки второго и третьего инверторов, вследствие чего процессы

834764

Составитель Ю. Ушаков

ТехредЖ.Кастелевич КорректорB Синицкая

Редактор A. Лежнина

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35р РаУшская наб д» 4/5

Заказ 4110/79

Филиал ППП Патент, r. Ужгород, Ул, Проектная, 4