Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскмх

Соцналистичесних

Ресаублмк нц834766 (61) Дополнительное к авт. саид-ву (22) Заявлено 260479 (21) 2758028/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 3005.81. Бюллетень Èß

Дата опубликования описания 3005.81 (5 )м g> 3

G 11 С 11/00

Государственный комитет

СССР но делам изобретений и открытий (53) УДИ 681. 327. б (088.8) (72) Авторы изобретения

IOФ .В CyJIHMQB H В С roJIy6eB (71) 3 а яв итель (54) БУФЕРНОЕ ЗАПОМИНй0ЦЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике.

Известно буферное запоминающее устройство (БЗУ)., которое позволяет передавать информацию в одном направлении (11.

Недостаток данного устройства невозможность передачи информации в двух направлениях.

Наиболее близким по технической сущности к предлагаемому является

БЭУ, обеспечивающее передачу,(прием) информации в двух направлениях °

Оно содержит накопитель, входы которого подключены через первую группу элементов И к входным шикам и к шинам записи, а выходные шины и нины считывания подключены через вторую группу элементов И к выходам накопителя, формирователь адреса, подключенный через третью группу элементов И к адресным входам нако пителя, элемент ИЛИ.

Фсрмирователь адреса в БЗУ состоит из датчика адреса записи и датчика считывания, выходы которых подключены ко входам схем сравнения.

Выход схемы сравнения подключен к первому входу элемента И, второй вход которого соединен с шиной сигналов считывания и с входом датчика кода адреса считывания, а выход подключен к первому входу элемента ИЛИ, второй вход которого соединен с шиной сигналов записи, а выход — с входом датчика кода записи (2).

Недостатком БЗУ является то, что информация, поступившая из канала связи и записанная в накопитель по адресам, формируемым датчиком адреса считывания, вылоднтся на приемное

Устройство с некоторой задержкой при обращении к накопителю по адресам, формируемым датчиком адреса записи.

Величина этой задержки является переменной и зависит îT сдвига между состояниями датчиков адресов записи и считывания и может быть равна времени полного обхода накопителя, т.е. длительности цикла смены адресов.

Указанный недостаток снижает быстродействие и оперативные возможности БЗУ, особенно в случае приме« нения БЭУ в аппаратуре связи.

Цель изобретения - повышение быстродействия устройства, Поставленная цель достигается тем, что буферное запоминающее устройство, содержащее накопитель, входы которого подключены через эле834766

S5 еО менты И первой группы к входным шинам, а выходы — через элементы И второй группы к выходным шинам, формирователь адреса, выходы которого подключены через элементы И третьей группы к адресным входам накопителя, 1 ополнительно содержит управляемый енератор импульсов, входы которого подключены к выходам элементов И второй группы, элемент И, первый вход которого подключен к выходу управляемого генератора импульсов, элемент задержки, вход которого подключен к выходу элемента И и к входам элементов И второй группы, дополнительный формирователь адреса, вход которого подключен к выходу элемента задержки, элементы И четвертой группы, первые входы которых подключены к выходу элемента И и к входам элементов И второй группы, а выходы— к адресным входам накопителя, схему сравнения, первый вход которой подключен к выходу дополнительного формирователя адреса, а второй вход — к соответствующим выходам формирователя адреса, элемент НЕ,вход которого подключен к выходу схемы сравнения,а выход †. ко второму входу элемента И.

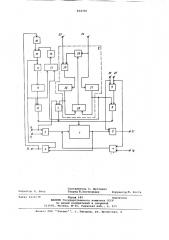

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит накопитель 1, формирователь адресов 2, элементы

И 3-4 первой группы, элементы И 5-6 второй группы, элементы И 7-8 третьей группы, элемент ИЛИ 9, управляемый генератор 10 импульсов, элемент

11 задержки, дополнительный формирователь 12 адресов, схему 13 сравнения, элемент НЕ 14, элемент И 15, элемент И 16 четвертой группы.

На шины 17-18 поступает информация, подлежащая записи в накопитель, соответственно от передающего устройства и из канала связи, а на шину 19 — управляющие сигналы записи информации в накопитель из передающего устройства. На шину 20 поступают управляющие сигналы считывания информации из накопителя в канал связи. Информация, считанная из накопителя в канал связи, поступает на шину 21, а информация, считанная из накопителя в приемное устройство, — на шину 22. На шины 23 и 24 поступают сигналы смены адреса, на шину 25 — упранляющие сигналы записи информации н накопитель из канала связи. Формирователь 2 адресов записи и считывания состоит из блока 26 записи адреса, блока 27 адреса считывания, блока 28 сравнения, элемента И 29 и элемента ИЛИ 30.

Ввод-вывод информации н (из) накопитель, поступающей из (в) канала связи, осуществляется по адресам,которые вырабатываются формирователем ,2 адресов, и через элементы И 7

f0

45 и 8, на вторые входы которых подаются управляющие сигналы соответственно от шины 19 и от элемента ИЛИ 9.

Блок 28 сравнения, элемент И 29, элемент ИЛИ 30, входящие в состав формирователя адресов, обеспечивают сравнение адресов в блоках 26 и 27 адреса и их установку н положение, при котором адрес записи блока 26 никогда не отстает от адреса считывания блока 27. Подгон адреса записи осуществляется сигналом смены адреса, формирующимся на первой адресной шине 24 и поступающим через элемент И 29 и элемент ИЛИ 30 на вход датчика 26, Считывание приня-. той из линии информации на выходные шины 22 обеспечивается входящими в состав устройства блоками 10-16.

Датчик 10 формирует управляющие сигналы считывания с частотой, определяемой кодом на шине 22; при отсутствии информации в накопителе управляющие сигналы поступают с высокой, ограничиваемой быстродействием накопителя частотой; при наличии информации в накопителе управляющие сигналы поступают с низкой, ограничиваемой быстродействием приемного устройстна частотой. Если адрес в формирователе 12 совпадает с адресом в формирователе 2, то на вход элемента И 15 с выхода блока

13 сравнения через элемент НЕ 14 поступает сигнал, разрешающий прохождение с генератора 10 управляющих сигналов на вход элемента И 15, на вход элемента И 6 и через элемент задержки 11 — на вход дополнительного формирователя 12 адреса. При совпадении кодов на входах формирователей 12 и 2 с выхода блока 13 сравнения через элемент НЕ 14 на вход элемента И 15 поступает сигнал, запрещающий прохождение сигналов с генератора 10.

Последовательность нвода и вывода информации из накопителя 1 определяется управляющими сигналами на шинах 19,20 и 25, которые формируются в зависимости от состояния линии связи

В режиме Линия связи свободна информация может поступать по каналу передачи и по каналу приема, при .этом на шину 20 поступает сигнал, обеспечинающий считывание передаваемой в канал связи информации по адресу, определяемому формирователем 2 (блок 27), и ее вывод в канал связи по шине 21. На шину 25 поступает сигнал, обеспечивающий запись принимаемой из канала связи информации по адресу, который был опрошен и освобожден по сигналу, поступающему с шины 20 в предыдущем такте. На шину 19 поступает сигнал, обеспечивающий запись информации

834766 в накопитель по адресу, определяемо-( му формирователем 2 (блок 26).

Сигналы смены адреса поступают на шины 23 и 24 поочередно, при этом частота поступления сигналов на шину 23 определяется частотой работы приемного и передающего аппаратов,,а частота поступления сигналов на шину 24 — скоростью передачи информации в линии связи.

Считывание принятой из линии связи информации и ее вывод на выходные шины 22 осуществляется сигналами генератора 10 по адресам, определяемым формирователем 12.

Благодаря тому, что генератор 10 управляется состоянием шины 22, достигается минимальная задержка вывода из накопителя информации на приемное устройство.

В режиме Линия связи занята передача информации в линию связи 20 и прием ее из линии связи отсутствуют. При этом управляющие сигналы на шины 20 и 25 и сигналы смены адреса на шину 24 не поступают. В данном режиме подаются управляющие д5 сигналы на шину 19, а сигналы смены адреса — на шину 23. При этом осуществляется запись в накопитель информации, поступающей на шину 17 от передающего устройства, и вывод принятой из канала связи информации на шину 22 в соответствии с сигналами датчика 10. При заполнении накопителя запись прекращается.

Считывание информации из накопителя также прекращается, как только код адреса на выходе формирователя 12 совпадает с кодом адреса на выходе формирователя 2 (6JIDK 27).

Предлагаемое БЗУ может быть исгользовано в стартстопных синхронных 40 системах передачи (приема) информации, когда информация передается в двух направлениях с промежуточным хранением в памяти. При этом устраняется задержка в выводе принятой 45 из линии связи информации на приемное устройство (тем самым сокращается общее время доведения сообщения от источника до приемника информации) . Это особенно важно при передаче некоторых видов быстростареющей информации и при ведении переговоров двух абонентов связи.

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель, входы которого подключены через элементы И первой группы к входным шинам, а выходы — через элементы И второй группы к выходным шинам, формирователь адреса, выходы которого подключены через элементы И третьей группы к адресным входам накопителя, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия устройства, оно содержит управляемый генератор импульсов, входы которого подключены к выходам элементов И второй группы, элемент И,первый вход котерого подключен к выходу управляемого генератора импульсов, элемент задержки, вход которого подключен к выходу элемента И и к входам элементов И второй группы, дополнительный формирователь адреса вход которого подключен к выходу элемента задержки, элементы И четвертой группы, первые входы которых подключены к выходу элемента И и к входам элементов И второй группы, а выходы — к адресным входам накопителя, схему сравнения, первый вход которой подключен к выходу дополнительного формирователя адреса, а второй вход — к соответствующим выходам формирователя адреса, элемент НЕ, вход которого подключен к выходу сравнения, а выход — ко второму входу элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 446052, кл. 6 06 Р 5/00, 1971 °

2. Авторское свидетельство СССР

Р 583476, кл. С 11 С 11/00, 1976 (прототип) ..

834766

Составитель С. Шустрнко

Техред Ж. Кастелевич Корректор М. Коста

Редактор Л. Филь

Закаэ 4110/79

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4