Элемент памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социапнстическмк

Республнк

< 1834767

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 310579 (21) 2773646/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 300581. Бюллетень Но 20

Дата опубликования описания 3005.81 (51)м. КЛ.З

G 11 С ll/40

Государственный комитет

СССР по делам изобретений и открытий (53) УД (681.327.66 (088.8) (72) Авторы изобретения

В.А. Милошевский и А.A. Яковлев (71) Заявитель (54) ЭЛЕМЕНТ ПАМЯТИ

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств.

Известен элемент памяти (ЭП), который содержит триггер, построенный на МДП-структурах, а также транзисторы для записи и считывания инфОрмации из такого ЭП и необходимые для построения запоминающих устройств из этих элементон (1).

Недостатком такого ЭП является большое количество внешних выводов.

Наиболее близкий к предлагаемому элемент памяти (ЭП) содержит память транэисторон, из которых первые три имеют проводимость первого типа, а остальные — проводимость, противоположную проводимости первого типа.

Четыре транзистора из них образуют триггер, а пятый является ключом (2).

Недостатком известного ЭП является большое количество ныводон (четыре), что усложняет коммутацию н запоминающем устройстве ЗУ, построенном на таких элементах и уменьшает степень интеграции ЗУ.

Цель изобретения — повЫшение наI дежности ЭП за счет уменьшения количества выводов элемента.

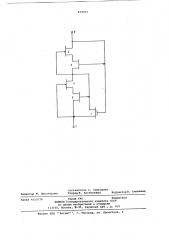

Поставленная цель достигается тем, что в элементе памяти, содержащем управляемый транзистор первого типа проводимости и ключевые транзисторы, первый и третий из которых — первого типа проводимости, а второй и четвертый — проводимости, противоположной проводимости первого типа, исток и сток первого ключевого транзистора подключены соответственно истоку второго ключевого и затворам управляемого и второго ключевого транзисторов, исток и сток четвертого ключевого транзистора подключены соответственно к истоку и затвору третьего ключевого транзистора, затворы первого и четвертого ключевых транзисторов и стоки управляемого, второго и третьего ключевых транзисторон объединены, исток управляемого транзистора подключен к стоку четвертого ключевого транзистора, а стоки первого и четвертого ключевых транзисторов соединены соотнетственно с первым и вторым выводами ЭП.

На чертеже приведена принципиальная схема ЭП.

Элемент памяти содержит управляемый МОП транзистор 1, первый, нто3() рой, третий и четвертый ключеные .l

834767 (2) то транзисторы 2 5 открываются а транзистор 1 закрыт, При этом большая часть напряжения падает на транзисторах 4 и 5. Если теперь Ug7 увеличить настолько, чтобы выполнялось

1О,условие

Наконец, если независимо от того, в каком состоянии ЭП находится, напрятранзисторы 2-5. Точки 6 и 7 являются соответственно первым и вторым выводами ЭП. Введем следующие обозначения: разность потенциалов между б7 точками 6 и 7 „ напряжение между стоком и истоком транзистора 1; порог открывания транзистоl11 ра 1;

U ° — напряжение перекрытия каная1 ла транзистора i (1=2, 3,. 4, 5) .

Пусть крутизна транзисторов 2 и

3 выше, чем крутизна транзисторов

4 и 5

+ " +UP 3 < 1 6 (Н2 nS М4

ЭП работает следующим образом.

Если U67 удовлетворяет условию (1) (режим хранения информации), то ЭП может находиться в любом из следующих двух устойчивых состояний.

В первом состоянии (пусть оно соответствует, например, 0 двоичной информации) транзисторы 2 и 3 закрыты, а 4 и 5 открыты, вследствие чего U близко к О. Во втором состоянии, соответствующем 1 двоичной информации, транзисторы 2 и 3 открыты, а 4 и 5 закрыты и U„ близко

U6$, В обоих рассеиваемая ЭП, мала и обусловлена лишь токами утечки.

Если - увеличить настолько, чтобы оно несколько превысило U 1 (режим чтения информации}, то ЭП, находящийся в состоянии 1, начинает пропускать ток, протекающий через открытые транзисторы 1-3.

Если такое же напряжение U67 подать на ЭП, находящийся в состоянии 0, то ток через ЭП течь не будет, так как транзисторы 2 и 3 закрыты.

Если и далее увеличивать напряжение Пбт на ЭП, находящемся в состоянии 1, то транзистор 1 будет открываться сильнее и падение напряжения на транзисторах 2 и 3 будет возрастать. В результате этого транзисторы 2 и 3 закрываются, потенциал стоков транзисторон 3 и 4 приближается к потенциалу точки 7 и транзисторы 4 и 5 открываются (режим записи 0 ) . Это состояние сохранитс при уменьшении Оя и переходе в режим хранения информации. Если же ЭП находится и состоянии 0, то осуществление режима записи 0 не приведет к изменению его состояния. жение Уб уменьшить настолько, чтобы выполнялось условие (режим записи

1 11I 1) то транзисторы 4 и 5 закроются и ЭП установится в состояние 1 .

Таким образом, предлагаемый ЭП является статическим, управляется во всех режимах однополярным напряжением и имеет всего два вывода.

Изменяя напряжение Ugy, можно перевести ЭП в любое из двух состояний, считывать информацию, хранимую в нем (не разрушая ее при этом), или перевести ЭП в режим хранения, и ко25 тором он практически не потребляет энергию. формула изобретения

Элемент памяти, содержащий управляемый транзистор первого типа

30 проводимости и ключевые транзисторы, первый и третий иэ которых - первого типа проводимости, а второй и четвертый — проводимости, противоположной проводимости первого типа, 35 о .т л и ч а ю щ и и сятем,,что, с целью повышения надежности элемента памяти, исток и сток первого ключевого транзистора подключены соответственно к истоку второго клю-.

4р ченого и затворам управляемого и второго ключевого транзисторов, исток и сток четвертого ключевого транзистора подключены соответственно к истоку и затвору третьего ключевого транзистора) затворы первого

45 и четвертого ключевых транзисторон и стоки управляемого, второго и третьего ключевых транзисторов объединены, исток управляемого транзистора подключен к стоку четвертого ключеного транзистора, а стоки первого и четвертого ключевых транзисторов соединены соответственно с первым и вторым выводами элемента памяти.

55 Источники информации, принятые во внимание при экспертизе

1. Патент CIQA 9 4006469, кл. 340-173, опублик. 1976.

2. Патент CIIIA Р 3521242, кл. 340-173, опублик. 1974.

834767

Составитель С. Самуцевич

Техред Ж. Кастелевнч КорректорВ. Синицкая

Редактор М. Лысогорова

Заказ 4110/79

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4