Запоминающее устройство с автоматичес-ким восстановлением работоспособности

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналнстнческ их

Реслублнк

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВКДИТИЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 170979 (21) 2826233/18-24 с присоединением заявки Йо (23) Приоритет

Опубликовано 300581. Бюллетень М 20

Дата опубликования описания 300581

«i>834770

Ф

"4 (5!)м. кл.з

G 11 С 29/00

Государственный комитет

СССР ио делам изобретеиий и открытий (53) УДК 681.327 (088.8) (72) Автор изобретения

A В Чернориз (71) Заявитель (54) ЗАПОМИНИОЩЕЕ УСТРОЙСТВО С АВТОМАТИЧЕСКИМ

ВОССТАНОВЛЕНИЕМ РАБОТОСПОСОБНОСТИ

Изобретение относится к запоминающим устройствам (ЗУ) и предназначено для использования в системах памяти, в том числе выполненных на интегральных схемах с большой степенью интеграции.

Известно ЗУ с автоматическим восстановлением работоспособности, в котором устранение неисправности осуществляется путем подключения резервного оборудования (1).

Недостаток устройства — большие аппаратурные затраты.

Наиболее близким к предлагаемому является ЗУ с автоматическим восстановлением работоспособности, содержащее блок выборки адресов, основные одноразрядные блоки памяти, входные шины и шины управления— по числу разрядов хранимой информации, входной и выходные коммутаторы, причем соответствующие входные шины соединены со входами основных входов памяти и информационными входами входного коммутатора, а выходы основных блоков памяти — с информационными входами соответствующих выходных коммутаторов. При отказе в этом ЗУ одного из основных блоков памяти автоматически подключается резервный (2).

Недостаток этого устройства — его значительная аппаратурная избыточность в связи с тем, что при отказе даже одной ячейки памяти в основном блоке заменяется весь блок памяти с неисправностью на резервный такой же информационной емкости.

Цель изобретения — упрощение устройства путем уменьшения аппаратурной избыточности

Поставленная цель достигается

15 тем, что в запоминающее устройство с автоматическим восстановлением работоспособности, содержащее адресный блок, группы основных накопителей, резервный накопитель, входной

2О и выхоцные коммутаторы, причем выход входного коммутатора подключен к одкому из входов резервного накопителя,выход которого соединен с одним из информационных входов выходкых коммутаторов, другие информационные входы которых подключены к выходам основных накопителей, информационные входы которых подключены к .одним из входов входного коммутатора

3() Ии являются информационными входами

834770

Формула изобретения устройства, введены элементы И (по числу разрядов накопителя) и блок местного управления, один из входов которого подключен к.одному из выходов адресного блока, другие выходы. которого соединены с адресными входами одноименных накопителей групп основных накопителей, выход блока местного управления подключен к другому входу резервного накопителя и перI вым входам элементов И, .выходы которых соединены с управляющими входами коммутаторов, вторые входы элементов И и другой вход блока местного управления являются управляющими входами устройства.

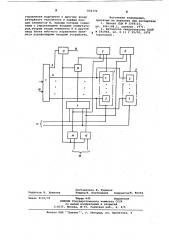

На чертеже дана структурная схема предлагаемого устройства (для двухразрядного ЗУ) .

Устройство содержит группы 1 и

2 одноразрядных основных накопителей 3, входной коммутатор 4, выход- 20 ные коммутаторы 5 и 6, адресный блок

7, имеющий выходы 8 и 9 и входы 10.

Устройство содержит также блок 11 местного управления, один вход которого подключен к выходу 9 блока 7, рс; другой является одним из управляющих входов 12 устройства, а выход соединен с одним из входов резервного накопителя 13 и первыми входами элементов И 14 и 15,вторые входы которых являются другими управляющими входами 16 устройства, имеющего информационные входы 17, Выходы элементов И 14 и 15 соединены с управляющими входами коммутаторов 4-6.Выходы блока 7 соединены с адресными входами одноименных накопителей 3 групп

1и 2.

Устройство работает следующим образом.

При отсутствии неисправностей в основных накопителях 3 блоком 7 вырабатывается сигнал выборки с уровнем 1 на одном из выходов 8, разрешая обращение к подключенным к нему 4 одноименным накопителям 3 групп 1 и

2. На остальных выходах 8 — уровень 0 . На все входы 16 подан сигнал с уровнем 0 . При этом на выходах элементов И 14 и 15 будет также уровень 0, который запрещает подачу входной информации на информационный вход накопителя 13 и разрешает выдачу информации с основных накопителей 3 через выходные коммутаторы 5 и 6. Обращение производится к выбранным накопителям 3.

При отказе одного из накопителей

3, например, в группе 2 в блок 11 управляющим сигналом по входу 12 заносится информация о номере отказав- бО щего накопителя 3, поступающая с выходов 9 блока 7, а на управляющий вход 16, соответствующий отказавшей .группе 2 накопителей 3, подается . уровень 1 .

Блок 11 вырабатывает сигнал выборки резерва с уровнем 1, разрешая обращение к резервному накопителю 13 и открывая элемент И 15, сигнал с выхода которого подключает соответствующий вход 17 через входной коммутатор 4 ко входу резервного накопителя 13, а его выход — через выходной коммутатор 6 к выходу устройства, одновременно блокируя выдачу информации от неисправной группы 2 накопителей 3.

Таким образом, резервный накопитель 13 памяти фактически занимает место отказавшего накопителя 3 в группе 2 °

Аналогично производится выборка резервного накопителя 13 при последующих обращениях (записи или считывании информации) к ЗУ по адресам, соответствующим отказавшему накопителю 3. Если обращение к ЗУ производится по другим адресам, то сигнал выдачи резерва не вырабатывается и резервный накопитель 13 не включается.

Предлагаемое устройство позволяет по сравнению с известными автоматически восстанавливать работоспособность при значительно меньшей аппаратурной избыточности, так как при отказе заменяется не вся группа основных накопителей, а лишь ее отказавший накопитель.

Предлагаемое Зу может быть построено на интегральных схемах с большой степенью интеграции, причем в качестве одноразрядных накопителей мо,гут быть использованы отдельные интегральные схемы памяти.

Запоминающее устройство с автоматическим восстановлением работоспособности, содержащее адресный блок, группы основных накопителей, резервный накопитель,;входной и выходные коммутаторы, причем выход входного коммутатора подключен к одному из входов резервного накопителя, выход которого соединен с одним из информационных входов выходных коммутаторов, другие информационные входы которых подключены к выходам основных накопителей, информационные входы которых подключены к одним из входов входного коммутатора и являются информационными входами устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит элементы И (по числу разрядов накопителя) и блок местного управления, один иэ входов которого подключен к одному иэ выходов адресного блока, другие выходы которого, соединены с адресными входами одноименных накопителей групп основных ,накопитеЛей, выход блока местного

834770

Составитель В. Рудаков

Техред Ж. Кастелевич КорректорМ. Коста

Редактор Н. Бушаева

Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4110/79

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 управления подключен к другому входу резервного накопителя и первым входам элементов И, выходы которых соединены с управляющими входами коммутаторов,вторые входы элементов И и другой вход блока местного управления являются управляющими входами устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент США Р 3568153 кл. 340-146.1, опублик. 1971 °

2. Авторское свидетельство СССР

9 591966, . G 11 C 29/00 1976 (прототип) .