Запоминающее устройство с само-контролем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<, >834771

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 141179 (2() 2842058/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 00581 Бюллетень ¹ 20

Дата опубликования описания 300581 5 М К„з

G l1 С 29/00

Государственный комитет

СССР по делам изобретений и открытий (53) «УДК 681. 327 (088 ° 8) (72) Авторы изобретения

И.В. Огнев, Ю.A. Розанов и О.В. Исаев (71) Заявитель

Московский ордена Ленина энергетический институт (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам и может быть использовано в системах, требующих быстрого восстановления работоспособ5 ности запоминающих устройств.

Известны запоминающие устройства с самоконтролем.

Одно из известных устройств содержит динамические полупроводниковые блоки памяти, дешифратор, элементы 2 И, блок управления, блок регенерации, состоящий из таймера, генератора регенерации, счетчика и селектора, и блок диагностики (1)., Недостатками этого устройства являются высокие аппаратурные затраты на блок диагностики и низкая надежность.

Наиболее близким к предлагаемому является запоминающее устройство, 20 содержащее полупроводниковые блоки памяти, дешифратор, первые и вторые адресные шины, блок микропрограммного управления и схемы локализации отказов (блок диагностики) (21, Недостаток такого устройства заключается в низкой надежности в случае реализации устройства на динамических запоминающих элементах вследствие невозможности определять отказы ЗО блоков, обеспечивающих регенерацию информации .

Цель изобретения — повышение надежности запоминающего устройства, выполненного с применением полупроводниковых запоминающих элементов динамического типа.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее группу накопителей, дешифратор, блок контроля и блок управления, причем выходы накопителей подключены ко входам блока контроля, входы дешифратора подключены к одним из адресных выходов блока управления и являются одними из адресных входов устройства, другие адресные выходы блока управления являются другими адресными входам;..устройства, введены формирователь синхроимпульсов, счетчик, мультиплексор, селектор, блок местного управления, элементы И и элемент И-НЕ, причем первый вход селектора подключен к первому входу элемента И-НЕ и первому управляющему выходу блока управления, второй входк выходу формирователя синхроимпуль-, сов, а третий вход — ко второму уп равляющему выходу блока управления, 834771 регенерацией информации в зависимости от режима работы устройства и этапа диагностирования.

Устройство работает в рабочем режиме и в режиме диагностирования.

2О

По истечении периода регенерации, отсчитываемого таймером, на его выходе появляется логическая единица которая стробируется на селекто-. ре 6 логической единицей с первого управляющего выхода блока управления 5, и поступает на вход блока местного управления 9.

Этот блок вырабатывает последовательность импульсов на входе счетчика 10 и сигнал Регенерация (логическая единица), стробирующий мультиплексор 11 и элемент И-HE 7.

Так как оба входа этого элемента находятся в состоянии логической единицы, то логический 0 на его выходе переключает выходы всех элементов И 2 в состояние 0, что обеспечивает одновременное обращение по всем столбцам накопителей 1 во время регенерации. Адреса регенерации формируются на счетчике 10 и при наличии сигнала Регенерация через входы мультиплексора 11 поступают на адресные входы накопителей 1. После полного перебора адресов на счетчике 10 ныход формирователя синхроимпульсов 8 перебрасывается в нулевое состояние и регенерация заканчивается.

В режиме диагностирования выполняется циклическая перезапись и считывание по всем адресам столбца навыход селектора подключен ко входу блока местного управления, первый выход которого соединен со входом счетчика, а второй выход - co входом стробирования мультиплексора и вторым входом элемента И-НЕ, выход котoporo подключен к первым входам элементов И, вторые входы которых соединены с выходами дешифратора, а выходы — с первыми адресными входами накопителей, выходы мультиплексора подключены ко вторым адресным входам накопителей, одни из выходов мультиплексора соединен с выходами счетчика, а другие входы с другими адресными выходами блока управления.

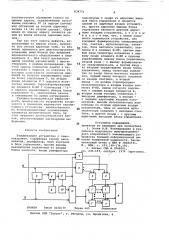

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит группу накоi!Hгелэй 1, выполненных на полупроводниковых запоминающих элементах динамического типа, элементы И 2, дешифратор 3, блок контроля 4, блок управления 5, селектор 6, элемент

ii -НЕ i, формирователь синхроимпульссл 8, блок местного управления 9, предназначенный для управления pere:. . ацией инФормации, счетчик 10, г.упьтиплексор 11 и адресные входы и 13.

Выходы накопителей 1 подключены к» -:кодам блока контроля 4. Входы демнфратора 3 подключены к одним из адресных выхоцов блока управления 5 и являются одними из адресных входов 12 устройства. Другие адресные выходы блока управления 5 соединены с другими адресными входами

13 устройства. Первый вход селектора 6 подключен к перному входу элемента И-НЕ 7 и первому управляющему выходу блока управления 5. Второй вход селектора 6 соединен с выходом формирователя синхроимпульсов

8, а третий вход — со вторым управляющим выходом блока. Управления 5.

Выход селектора 6 подключен ко входу блока местного управления 9, первый выход которого соединен со входом счетчика 10, а второй ныходсо входом стробирования мультиплексора 11 и вторым входом элемента

И-HE 7, выход которого подключен к первым входам элементов И 2, вторые входы которых соединены с выходами дешифратора 3, а выходы — с первыми адресными входами накопителей 1. Одни из входов мультиплексора 11 соединены с выходами счетчика 10, а другие входы — с другими адресными ныходами блока управления

5.

Устройство работает следующим. образом.

Блок управления 5, выполняющий микропрограммное управление, и селектор 6 осуществляют управление

60 б5

Состояние первого управляющего выхода блока управления 5 соответствует логической единице в рабочем режиме и логическому 0 н режиме диагностирования.

Селектор 6 подключает вход блока местного управления 9 к формирователю синхроимпульсов 8 в рабочем ре-. жиме или к блоку управления 5 в режиме диагностирования.

В рабочем режиме адрес столбца накопителей 1 поступает с первых адресных входов 12 устройства на дешифратор 3, на одном из выходов которого появляется логический О., а на других выходах — логическая единица, поступающие на первые входы элементов И 2. На вторые входы элементов И 2 с выхода блока местного управления 9 через элемент И-HE 7 подается логическая единица, что обеспечивает обращение только к одному столбцу накопителей

1, элементы памяти которых.возбуждаются логическим нулем. Адрес элемента памяти поступает со вторых адресных входов 13 устройства через входы мультиплексора 11 на адресные входы накопителей 1.

834771

Т а б л и ц а 1

1 1 0

1 0 0

NT 1

1 1 0 0 1 1

MT 2

0 1 1 0 0 1

МТ 3

Т а б л и ц а 2

Элементы памяти

О т

МТ3 МТ1 МТ2 МТЗ МТ1 МТ2

NT2

МТ1

МТ3 МТ1 МТ2 MTÇ NTl МТ2 МТЗ

МТ2

МТ1 МТ2 МТЗ МТ1 МТ2 МТЗ MTl

MT 3 копителей 1 и по всем столбцам набора тестовых слоев, пример которых

Адрес и набор тестовых слоев задаются блоком управления 5. Ко- личество тестовых слоев должно быть не менее трех для определения отказов по вторым адресным входам 13 устройства, так как в этом случае по адресам, кратным двум, записываются разные тестовые слова.

Особенностью предлагаемого усройства является последовательное проведение диагностирования в два этапа.

Целью первого этапа работы устройства является диагностирование

Аналогичным образом тестируются остальные столбцы накопителей 1.

Локализация неисправностей осуществляется после тестирования всего запоминающего устройства, Так как тест поиска дефекта обеспечивает естественную регенерацию информации, то запуск внешней регенерации на первом этапе необходимо блокировать, что осуществляется логическим 0 на управляющих выходах блока управления 5, подключенных к третьему и первому входам селектора б соответственно. Так как запуск внешней регенерации блокируется, то второй выход блока местного управления 9 находится в состоянии логического 0, который инвертируется элементом И-НЕ 7 и поступает на вторые входы элементов И 2, обеспечивая во время прохода теста поиска дефекта обращение только к одному столбцу накопителей

1. Адреса тестовых слоев формируются для разрядности слова, равной восьми, приведен в табл 1.

15 всего устройства, эа исключением блоков, осуществляющих регенерацию: формирователя синхроимпульсов 8, блока местного управления 9, счетчика 10, мультиплексора 11 и селектора б. В каждом последующем такте осуществляется запись тестовой последовательности, циклически сдвинутой на один адрес, для достижения первоначального положения.

25 Алгоритм работы устройства (тест поиска дефекта) для одного столбца и числа элементов памяти в каждом из накопителей 1, равного восьми, показан в табл. 2. на адРесных выходах блока управления

5. Считанные из накопителей 1 слова

45 поступают на входы блока контроля 4, где происходит локализация отказов.

Целью второго этапа работы устройства является..диагностирование селектора б,формирователя синхроимпульсов

8,блока местного управления 9,счетчика 10 и мультиплексора 11. Отказы счетчика 10 и мультиплексора 11. идентичны отказам адресных схем запоминающего устройства. Отказы типа Постоянный 0 на выходах формирователя синхроимпульсов 8, селектора б. или на первом выходе блока местного управления 9, приводящие к отсутствию последовательности импульсов на входе счетчика 10, или отказ блока шестого управления 9,приводящий к отсутствию сигнала Регенерация (в этом случае не стробируется мультиплексор 11 и блокируется передача адреса регенерации со счет 5 чика 10 на выход мультиплексора 11),!

834771

Формула изобретения

Заказ 4110/79 Тираж 645 Подписное

Филиал ППП "Патент", г; Ужгород, ул. Проектная, 4 соответствуют обращению только по одному адресу, определяемому состоянием счетчика 10 (в первом случае) или сигналами на вторых адресных входах 13 (но втором случае). Обращение по одному адресу является одним из видов отказов адресных нходон.

Так как тест поиска дефекта, используемый на первом этапе, выявляет все отказы адресных схем, то его можно применить для диагностирования указанных выше блоков без введения дополнительного оборудования в блок контроля 4 . Для этого достаточно любой столбец накопителей 1 протестировать в режиме. регенерации. При этом адреса элементов памяти н на-. . копителях 1 берутся со счетчика 10, который запускается логической единицей со второго управляющего выхода блока управления 5. На вторые входы элементов И 2 подается логическая единица (проиннертированный на элементе И-HE 7 логический 0 с первого управляющего выхода блока управления 5},. обеспечивая запись и считывание во время регенерации.

Технико-зкономическая эффективность предлагае .;>го устройства заключаются в повышении надежности запоминающего устройства, реализованного на полупроводниковых запоминающих элементах динамического типа, за счет введения диагностирования блоков, обеспечивающих регенерацию информации.

Запоминающее устройство с самоконтролем, содержащее группу накопителей, дешифратор, блок контроля и блок упранления, причем выходы накопителей подключены ко входам блока контроля, входы дешифратора подключены к одним из адресных выходов блока управления и являются одними из адресных входов устройства, другие адресные выходы блока управления янляются другими адрес5 ными входами устройства, о т л и ч аю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит формирователь синхроимпульсон, счетчик, мультиплексор, селектор, блок местного управления, элементы И и элемент И-НЕ, причем первый вход селектора подключен к первому входу элемента И-НЕ и первому управляющему выходу блока управления, 15 второй вход — к выходу формирователя синхроимпульсов, а третий вход— ко второму управляющему входу блока управления, выход селектора подключен ко входу блока местного управления, первый выход которого соединен

20 со входом счетчика, а второй выход — со входом стробиронания мультиплексора и вторым входом элемента И-НЕ, выход которого подключен к первым входам элементов И, вторые входы котоРых соединены с выходами дешифратора, а выходы— с первыми адресными входами накопителей, выходы мультиплексора подключены ко вторым адресным входам

ЗО .накопителей, один из выходов мультиплексора соединен с выходами счетчика, а другие входы — с другими адресными выходами блока управления.

Источники информации, принятые во внимание при экспертизе

1. Огнев И.В. Исследование и разработка модульного попупронодникового оперативного запоминающего устройства большой информационной ем4О кости повышенной надежности. Заключительный отчет о НИР 9 78080531.

M. МЭИ, с. 1.09,149-174,191.

2. Патент США М 3940601, кл. 235-153, опублик. 1976 (прототип)