Цифровой умножитель частоты сле-дования импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Реслублик ()834823 (61) Дополнительное к авт. свид-ву — (22) Заявлено 17.08.79 (21) 2809629/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. К., Н 03 В 19/00

Гееуддрственнмй кемитет

Опубликовано 30.05.81. Бюллетень №20

Дата опубликования описания 05.06.81 (53) УДК 621.374..44 (088.8) до делам нзееретеннй

N еткрмтий (72) Авторы изобретения

О. С. Голод, Ш. И. Исаев, И.-Б. И. Кампо и Т. В. Рубина (54) ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано в качестве масштабирующего устройства, систем измерения, вычисления и автоматической обработки данных, а также в качестве цифрового синтезатора частоты.

Известно устройство дискретного умножения частоты, содержащее цепь последовательно соединенных удвоителей частоты и преобразователь частота-напряжение, вход которого объединен со входом первого из удвоителей частоты и подключен к клемме источника входного сигнала, а выход — к управляющим входам удвоителей частоты (1) .

Недостатком устройства является невозможность получения дробных коэффициентов умножения больших единицы.

Наиболее близким по технической сущности к изобретению является устройство, содержащее счетчиковый делитель частоты, установочный блок, элементы И, блок фазовой автоподстройки, первый вход которого соединен с выходом элемента ИЛИ, а второй — с выходом блока фазовой автоподстройки, вход которого соединен с вы2 ходом установочного блока, разрядные выходы которого соединены с первыми входами элементов И, вторые входы которых соединены с разрядными выходами счетчикового делителя частоты, а выходы — с входами элемента ИЛИ (2).

Недостатком известного устройства является отсутствие возможности получения дробного коэффициента умножения больше единицы.

Цель изобретения — обеспечение возможности получения коэффициента умножения, выраженного неправильной дробью.

Указанная цель достигается тем, что в цифровой умножитель частоты, содержащий делитель частоты, вход которого подключен к входной шине, а разрядные выходы — к первым входам соответствующих элементов И, вторые входы которых соединены с соответствующими разрядными выходами установочного блока, а выходы — со входами элемента ИЛИ, выход которого соединен со входом блока фазовой автоподстройки частоты, ко второму входу которого подключен выход цифроаналогового преобразователя, вход которого соединен с выходом установочного блока, введены до834823

Формула изобретения

3 полнительный элемент И, элемент HE и дополнительный разряд установочного блока, выход которого подключен к первому входу дополнительного элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого подключен к входу делителя частоты, а выход — с дополнительным входом элемента ИЛИ.

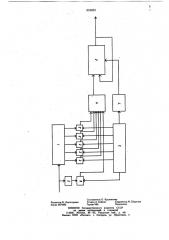

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит делитель I частоты, выполненный в виде счетчика, элементы 2 — 1, 2 — пИ, блок 3 установочный, элемент 4 ИЛИ, элемент 5 НЕ, блок 6 фазовой автоподстройки частоты, цифроаналоговый преобразователь 7, дополнительный элемент 8 И.

Устройство работает следующим образом.

Поступающие на вход устройства импульсы, будучи снятыми с одноименных плеч триггеров делителя 1, являются несовпадающими во времени по какому-то из одноименных фронтов импульсов и разнесены на период входной частоты, что позволяет осуществлять селективное пропускание импульсов на выход через элементы 2 в зависимости от положения блока 3 через элемент 4. Импульсы со входа устройства через элемент 5, обеспечивающий сдвиг на Т/2 по отношению к импульсам, пропускаемым с плеч триггеров, также могут быть селективно пропущены на выход через элемент 8 в зависимости от положения дополнительно введенного разряда блока 3, для чего в элементе 4 также введен дополнительный вход. На выходе элемента 4 импульсы представляют собой комбинацию входной частоты и ее субгармонических составляющих с выходов делителя 1. При осуществлении отбора только с разрядов делителя 1 коэффициент умножения меньше единицы, при отборе импульсов только с элемента 5 коэффициент умножения равен единице. При совместном отборе коэффициент умножения больше единицы и может быть равен двум.

Дискретность установки коэффициента определяется числом разрядов делителя 1, так, например, при выполнении счетчика в двоичном коде с 10-ю разрядами дискретность установки составит 1/1024 или, в общем случае, 1/2.

Следует отметить, что на выходе элемента 4 частота сформирована по числу импульсов за период цикла работы делителя 1, при этом она содержит пропуски и вставки субгармоник частоты. Для получения равно4 мерной частоты на выходе устройства импульсы с выхода элемента 4 поступают на вход блока 6, котбрый выполняется в виде инерционной системы автоматического регулирования, причем для обеспечения захвата и режима синхронизма в нем с блока 3 через цифроаналоговый преобразователь 7 к блоку 6 подводится напряжение, при котором частота на выходе устройства уже приближенно равна заданной частоте, определяемой коэффициентом умножения. Ввиду астатизма блока 6 по частоте погрешность при этом практически не вносится.

Преимущество предлагаемого устройства заключается в получении спектрально чистого сигнала на выходе, в возможности получения частоты, умноженной на дробный коэффициент больше единицы, что позволяет использовать устройство в системах измерения, вычисления автоматического управления и обработки данных.

Цифровой умножитель частоты следования импульсов, содержащий делитель частоты, вход которого подключен к входной шине, а разрядные выходы — к первым входам соответствующих элементов И, вторые входы которых соединены с соответствующими разрядными выходами установочного блока, а выходы — со входами элезо мента ИЛИ, выход которого соединен со входом блока фазовой автоподстройки частоты, ко второму входу которого подключен выход цифроаналогового преобразователя, вход которого соединен с выходом установочного блока, отличающийся тем, что, с целью обеспечения возможности получения коэффициента умножения, выраженного неправильной дробью, в него введены дополнительный элемент И, элемент НЕ и дополнительный разряд установочного блока, 40 выход которого подключен к первому входу дополнительного элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого подключен к входу делителя частоты, а выход — с дополнительным входом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 31!391, кл. Н 03 К 3/72, 27.03.70.

2. Патент Великобритании № 1264903, кл. Н 03 В 3/08, 23.02.72.

834823

Составитель О. Кружилина

Редактор М. Лысогорова Техред А. Бойкас Корректор М. Шароши

Заказ 4076/82 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/Ь

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4