Устройство установки схем цифровойавтоматики b исходное состояние

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И ЗОБРЕТЕ,Н Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублии (и834865 (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.07.79 (21) 2788269/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.э

Н 03 К 5/00

Гасударственный комитет

СССР

Опубликовано 30.05.81. Бюллетень № 20

Дата опубликования описания 06.06.81 (53) УДК 621.374 (088.8) ао делам изобретений и открытий.(72) Автор изобретения

К. К. Майковский (7l ) Заявитель (54) УСТРОЙСТВО УСТАНОВКИ СХЕМ ЦИФРОВОЙ АВТОМАТИКИ

В ИСХОДНОЕ СОСТОЯНИЕ

Изобретение относится к импульсной технике, в частности к цифровой автоматике.

Известно устройство установки в исходное состояние схем цифровой автоматики, содержащее элемент И вЂ” НЕ транзисторной логики, к одному из входов которого под- а ключена времязадающая диодноконденсаторная последовательная цепь и полюс источника управляющего напряжения. Вход логического расширения элемента И вЂ” НЕ ! подключен к точке соединения диода и кон.денсатора времязадающей цепи (1).

Наиболее близким по технической сущности к предлагаемому является устройство установки схем цифровой автоматики в исходное состояние, содержащее времязадаю- 1а щую RC-цепочку из последовательно соединенных конденсатора и ограничительного резистора, подключенную к одному из источников питающих напряжений, а также формирующий усилительный элемент, вход которого подключен к точке соединения конденсато10 ра с ограничительным резистором, параллельно конденсатору подключен ключевой элемент, входы которого соединены с остальными основными источниками питающих напряжений (2).

Однако данное устройство имеет недостаточную функциональную надежность, т. е. при пропадании одного из питающих напряжений формируется ложный сброс.

Цель изобретения — повышение функциональной надежности.

Поставленная цель достигается тем, что в устройство установки схем цифровой автоматики в исходное состояние, содержащее многовходовой ключевой элемент, времязадающую RC-цепь из последовательно соединенных конденсатора и ограничительного резистора, который одним концом подключен к одному из источников питающих напряжений, а вторым концом —. к входу парогового элемента, введены два логических элемента И вЂ” НЕ, диод и элемент памяти, входы которого подключены к источникам напряжения, а выходы — к входам ключевого элемента, выход которого соединен с первыми входами логических элементов

И вЂ” НЕ, вторые входы которых подключены к выходу порогового элемента, причем выход одного из логических элементов И вЂ” НЕ

834865

Формула изобретения подключен через диод ко входу порогового элемента, а выход второго логического элемента И вЂ” НŠ— к установочному входу элемента памяти.

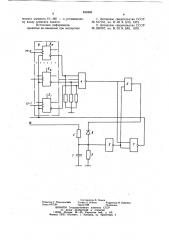

На чертеже изображена схема предлагаемого устройства.

Устройство содержит времязадающую

RC-цепочку из последовательно соединенных конденсатора 1 и ограничительного резистора 2, шунтирующий резистор 3, многовходовой ключевой элемент 4, пороговый элемент 5 и два двухвходовых логических элемента И вЂ” НЕ 6 и 7, диод 8, элемент 9 памяти и источник 10 питающих напряжений.

Ограничительный резистор 2 одним концом подключен к одному из источников 10 питающих напряжений, а вторым — к входу порогового элемента 5. Элемент 9 памяти подключен к источникам 11 — 1 — 11-и напряжений, а его выходы — к входам ключевеге элемента 4, выход которого подключен к первым входам логических элементов

И вЂ” HE 6 и 7. Вторые входы логических элементов И вЂ” НЕ подключены к выходу порогового элемента 5. Выход логического элемента И вЂ” HE 6 подключен через диод

8 ко входу порогового элемента 5, а выход логического элемента И вЂ” НЕ 7 — к установочному входу элемента 9 памяти. Входы многовходового ключевого элемента 4 зашунтированы. Элемент 9 памяти преимущественно выполнен на триггерах.

Устройство работает следующим образом.

При установке схем цифровой автоматики в исходное состояние в момент включения источников 11 †1 вЂ-и напряжения на выходах элемента 9 памяти, а следовательно, и на входах ключевого элемента 4 присутствует потенциал «О» (триггеры .элемента 9 памяти в этот момент находятся в неопределенном состоянии). На выходе ключевого элемента 4 появляется потенциал «1», который также присутствует и на выходе порогового элемента 5, так как конденсатор

1 не заряжен. Это обуславливает формирование на выходе логического элемента И—

НЕ 7 потенциала «0», подаваемого на установочные входы элемента 9 памяти и схем цифровой автоматики (счетчиков).

При этом на выходе элемента И вЂ” НЕ 6, присутствует потенциал «О», препятствующий заряду конденсатора 1. После установки триггеров элемента 9 памяти в исходное состояние, на входы ключевого элемента 4 подается потенциал «1», а на его выходе формируется потенциал «О», что снимает блокировку заряда конденсатора 1, на выходе логического элемента И вЂ” НЕ 6 формируется потенциал «1», а на выходе логического элемента И вЂ” НЕ 7 появляется потенциал «1» — разрешение на счет элементов цифровой автоматики. При этом конденса5

Зо

4 тор 1 заряжается, на .входе порогового элемента 5 появляется потенциал «1», а на выходе — потенциал «О», который удерживает логические элементы И вЂ” HE 6 и 7 в данном состоянии. Чередование на входе ключевого элемента 4 потенциалов «!» и «О» не влияет на работу устройства.

Пропадание напряжения одного из источников 11 — 1 — l l -п напряжения также не приводит к ложному сбросу. При отсутствии одного из этих напряжений в момент включения устройства на входе ключевого элемента 4 присутствует потенциал

«О», а на его выходе — потенциал «1». При этом конденсатор 1 не заряжен, что обуславливает наличие потенциала «1» на выходе порогового элемента 5 и потенциалов «О» на выходах логических элементов И вЂ” НЕ

6 и 7. В этом случае происходит установка схем цифровой автоматики в исходное состояние. При появлении отсутствующего напряжения на выходе элемента 9 памяти появ ляется потенциал «1», что обеспечивает изменение потенциалов на противоположные на ключевом элементе 4 и логических элементах И вЂ” НЕ 6 и 7. Появление потенциала «1» на выходе логического элемента

И вЂ” НЕ 6 позволяет осуществить заряд конденсатора 1 (в момент его заряда продолжается установка схем цифровой автоматики в исходное состояние). При достижении порогового значения потенциала на выходе элемента 5 появляется потенциал «0», обеспечивающий удержание потенциала «1» на выходах логических элементов И вЂ” НЕ 6 и 7 — разрешение на счет схем цифровой автоматики.

Таким образом, формирование ложного сброса при пропадании одного из питающих напряжений не происходит, что повышает функциональную надежность устройства.

Устройство установки схем цифровой автоматики в исходное состояние, содержащее многовходовой ключевой элемент, времязадающую RC-цепь из последовательно соединенных конденсатора и ограничительного резистора, который одним концом подключен к одному из источников питающих напряжений, а вторым концом — к входу порогового элемента, отличающееся тем, что, с целью повышения функциональной надежности, в него введены два логических элемента И вЂ” НЕ, диод и элемент памяти, входы которого подключены к источникам напряжения, а выходы — к входам ключевого элемента, выход которого соединен с первыми входами логических элементов И вЂ” НЕ, вторые входы которых подключены к выходу порогового элемента, причем выход одного из логических элементов И вЂ” НЕ подключен через диод ко входу порогового элемента, а выход второго логи834865

Составитель В. Чижов

Редактор Т. Мерменштайн Техред А. Бойкас Корректор. Н. Бабинец

Заказ 4057/84 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 I 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП сПатент», г. Ужгород, ул. Проектная, -4 ческого элемента И вЂ” НŠ— к .установочному входу элемента памяти.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР № 517151, кл. Н 03 К 5/13, 1973.

2. Авторское свидетельство СССР № 336787, кл. Н 03 К 5 01, 1970.