Последовательно-параллельный аналого-цифровой преобразователь c коррекциейпогрешности

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистические республик

< 834900 (бт } Дополнительное к авт. свид-ву %702513 (22} Заявлено 01.07.77(21) 2501187/18-21 (51)М. Кл.

Н 03 К 13/175 с присоединением заявки,% .

Гее)щеретеенеМ кеннтет

СССР (23} Приоритет

Опубликовано 30.05.81 Бюллетень М 20

Дата опубликования описания 03.06.81 пе делен нтебретеннй н етернтнй (53) УДК 681. .325(088.8) М. А. Пцльв н П. П. Алексеев (72) Авторы изобретения (7т) Заявитель (54) ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНЫЙ

АНАЛОГО-БИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (: KOPPEKIlHEA ПОГРЕШНОСТИ

° .

° ° ,Ф - е

Oi.

Изобретение относится к приборостроению и предназначено для использования в качестве быстродействующего аналогоцифрового преобразователя в приборах и системах для измерения различных биса

5 ропротекаюп их пропессов, а также в системах автоматического управления и контроля.

По основному авт. св. % 70253.3 известно устройство, содержащее и последовательно соединенных декад преобразования, каждая тт. -3. из которых состоит из. последовательно соединенных аналогоцифрового, цифроаналогового преобразователей, масштабного усилителя, компаl5 ратора погрешности и блока цифровой коррекции, соединенного также с выходом аналого-пифрового преобразователя, и управляемого блока сдвига, а младшая декада состоит из аналого-цифрового пре- то образователя, причем выход управляемого блока сдвига каждой предыдущей декады соединен с входом аналого-цифрового преобразователя последуютцей декады(1).

Недостатком такого устройства является возможность неверного срабатывания компараторов погрешности, которая может быть устранена с помоцтью высокочувствительных компараторов. Однако создание компараторов, обладающих одновременно высокой чувствительностью и быст родействием, является сложной задачей.

Таким образом, в цепом недостатком известного устройства является невысокая точность и сложность.

Бель изобретения - повышение точности и упрощение устройства.

Поставленная цель достигается тем, что в последовательно-параллельный аналого-цифровой преобразователь с коррекцией погрешности, содержацтий и последовательно соединенных декад преобразования, каждая тт -1. из которых состоит из последователЬно соединенных аналогоцифрового, цифроаналогового преобразователей, масштабного усилителя и компаратора погрешности, выход которого соединен с управляющим входом блока цифровой коррекции, выход которого соединен с ш ной,выходного кода, а сигнальный вход соединен с выходом аналого-цифрового преобразователя, вход которого соединен также с.выходом масштабного усилителя выход которого соединен с сигнальным входом управляемого блока сдвига, упра ляющий вход которого соединен с выходом компаратора погрешности, а выход подключен к входу аналого-цифрового преобразователя. следующей декады„ вход аналого-цифрового преобразователя ....с старшей декады соединен с шиной входного сигнала, а младшая декада содержит аналого-цифровой преобразователь, .выход которого соединен с шиной выходного кода, введен дополнительный блок цифровой коррекции, входы которого соединены с выходами компараторов погрешности, а его выход подключен:к управляющему входу блока цифровой коррекции старшей декады.

i

О(1) 0

834900 4 и- Устройство определенным образом обрабатывает сигналы компараторов погрешности, вводя поправку в показания старшей декады преобразователя.

Обозначая выходной сигнал дополнительного блока 7 цифровой коррекции .чав- реэ U, выходные напряжения компараторов 4-1 и 4-2 через U u Ug и учитывая, что они принимают значение либо

10 логической "l" (открытое состояние), либо логического "0" (закрытое состояние), заполним таблицу функционирования дополнительного блока 7 цифровой коррекции.

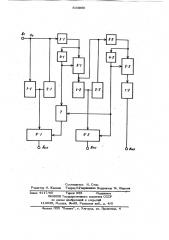

На чертеже представлена структурная электрическая схема преобразователя.

Устройство содержит и последовательно соединенных декад преобразования, каждая p -l. из которых, кроме младшей, содбржит последовательно соединенные аналого-цифровой преобразо Зо ватель 3., цифроаналоговый преобразователь 2, масштабный усилитель 3, выход которого соединен с входами компара тора погрешности 4 и управляемого блока 5 ссддввииггаа, выход которого соединен с входом. аналого-цифрового преобразователя следующей декады, выход компара тора 4- соединен с управляющими входами управляемого блока 5 сдвига и блока 6 цифровой коррекции, выход кото-. рого соединен с шиной выходногокода; а сигнальный вход которого соединен с выходом аналого-цифрового преобразователя 1, вход которого соединен также с шинОЙ ВхОднОгО сигнала и ВхОдОм масш 4 табного усилителя 3, младшая е декада содержит аналого-цифровой преобразователь 1, вход которого соединен с выходом управляемого блока 5 сдвига предыдущей декады, а выход подключен к пане выходного кода,.старшая декада содержит дополнительный блок 7 цифровой коррекции, входы которого соединены с выходами компараторов 4, а выход годключен к управляющему входу блока 6 цифровой коррекции.

Принцип работы дополнительного блока 7 цифровой коррекции заключается в следующем.

Аналогически U< выражается соотноше1 (2 3 2 Ъ 2. 3 (x)

Выражен ие в скобках иэ соотношения (4.) представляет собой значение U< (1) в таблице и принимает значение логической "1 в спучае, если напряжение на выходе масштабного усилителя 3-4 находится в пределах 10 В " (11 В и ложном срабатывании l-й декады. При этом через компаратор 4-1 не вводится коррек-. ция в показание 1-й декады, срабатывают компаратор 4-2, дополнительный блок ") и тем самым вводится коррекция в показание 1-й декады. Кроме того, при

Ug Q a 4 блок 7 реагирует только на сигнал компаратора 4 более старшей декады.

Из приведенного соотношения видно, что дополнительный блок 7 цифровой коррекции реализует простую алгебру логики, поэтому техническая схема может быть выполнена только на одном корпусе логической интегральной схемы, обеспечиваю- . щей быстродействие порядка нескольких наносекунд.

Оелесообразно предположить существенные изменения в этом преобразователе некоторого одиапазона, уровня срабатывания (У Рс ) компараторов 4 подобно тому, как уровни срабатывания компараторов декадных аналого-цифровых преобразователей лежат в определенном интер вале напряжений. Технически это связано

3 83490 со значительным упрощением сложной схемы чувствительных компаратор в 4 и повышением быстродействия всего устройства.

Выберем диапазон срабатывания компараторов 4, удовлетворяющий неравенс» ву

Последовательно-.параллельный аналого-цифровой преобразователь с коррекцией погрешности по авт. св. % 702513, о т л и ч а ю m и и с я тем, что, с келью повышения точности и упрощения устройства, в него введен дополнительный блок цифровой коррекции, входы которого соединены с выходами погрешности компараторов,а его выход подключен к управляюшему входу пифрового блока коррекпии старшей декады.

Источники информации, принятые во внимание при эксце»}тизе

1. Авторское свидетельство СССР

М»,7025lЗ, za, Н 03 К l3/3.75, 20.03.78 (прототип) .

lOa < u, c l В (2)

Проиллюстрируем работу предлагаемого

16 последовательно-nàðàëëeëüíîãî аналогоцифрового преобразователя с коррекцией погрешности на численном примере.

Пусть на шину входного сигнала преобразователя поступает преобразуемое напряжение g а2,0 l ÇB и компаратор уровня 2 в декадном аналого-цифровом преобразователе l-1 срабатвает только при уровне 2,3 В. В результате на выходе преобразователя 1-l мы будем а6 иметь показание 1, напряжение на вы.ходе масштабного усилителя 3-1 Я .

4.0(2,013-3.) и lO,l3 В.

Предположим что из а неточности порога срабатывания компаратора 4-1 35 последний срабатывает при уровне 10,4В.

В таком случае выходное напряжение 0

} управляемого блока 5 сдвига повторяет выходное напряжение масштабного усилителя З-l, при входном напряжении 10, 39

l3 В в .аналого-цифровом преобразователе l-2 срабатывает компаратор уровня «9» и показание на шине выходного кода блока 6-2 цифровой коррекции рав 9-, 3$

При этом напряжение на выходе масштабного усилителя 3-2 U atO(l0,3.3-9)=

М.l,3 В и, так как ll,3 В ) 11 В, то срабатывает компаратор 4-2, выходное напряжение доно}}нительного блока 7 циф 49 ровой коррекции повторяет сигнал компа- . ратора 4-2 и посредством блока 6-1 l коррекции в показание аналого-пифрового . преобразователя 1.-1 вводится коррекция

l+l®2, а при помощи блока 6-2 коррек- 45 пии в показание аналого-цифрового преобразователя l-2 вносится поправка

9+М(1) О. Одновременно при помощи управляемого блока 5-2 сдвига на вход аналого-цвфрового преобразователи l-3 50

0 С поступает напряжение У -1 1,3 — 0

} а 3,,ЗВ.

B зависимости от уровней срабатывания компараторов в аналого-цлфровомпреобразователе 1-3 показание на его выходе будет равно l или О, а показание устройства при входном напряжении U}}

2,01.3 B в целом 20l или 200, полученная погрешность показания равна погреши сти дискретности преобразования преобразователя.

В предложенном аналого-цифровом преобразователе система коррекции погрешности допускает небольшую неточность уровней срабатывания компараторов, что достигается введением в схему устройства дополнительного блока цифровой коррекции, включенного в неточные цепи аналого-цифрового преобразователя. Техническая реализация решения проста, так как дополнительный блок цифровой коррекции погреп}ности может быть выполнен только на одном корпусе логической интегральной схемы, .; Ъбеспечиваюшей быстро»ействие порядка нескольких наносекунд, тогда как в известном устройстве требуются компараторы, которые должны обеспечить высокую точность, чувствительность и быстродействие, что является сложной проблемой.

Формула изобретения

834900

Составитель И. С том

Редактор Н. Кешеля Техред ЕХаврюяюеяюко Корректор М. Шароши

Заказ 41. 3.7/85 Гираж 988 Подписное

ВНИИПИ Государственною о комитета СССР по делам изобретений и открытий

З.l3035, Москва, Ж35, Раушская наб., д. 4/5 филиал ППП Патент, r. Ужгород, ул. Проектная, 4