Делитель частоты

Иллюстрации

Показать всеРеферат

ОП ИКАНИЕ изовррт ния " ® 49З"

Союз Советских

Социалистических

Респубиик а

К АВТОРСКОМУ СВИ ИТИЛЬСТВУ (6l) Дополнительное к авт. сеид-ву— (22) Заявлено 13. 11. 79 (21) 2838399/18- 21 с присовдииением заявим М— (23) Приоритет

Опубликовано 300581. бюллетень М 20

Дата опубликования описания 300581 (51)М. Кл.з

Н 03 К 23/00

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621. 374. 32 (088.8) Г т

В.С.Голубев, B.À.Òðîøàíîâ и Н.Ф.Юрков

Я,,,, 1 (72) Авторы изобретения (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ

Изобретение относится к импульсной технике и может быть использовано в автоматике, вычислительной технике, технике связи и других областях, связанных с обработкой и преобразованием цифровой информации.

Известен делитель частоты, который содержит последовательный счетчик.со счетным триггером, триггером управления и схемой И-HE в каждом разряде. Отдельные разряды соедйнены последовательно один с другим таким образом, что счетные триггеры образуют счетчик входных импульсов, а логические схемы и управляющие триггеры - устройство управления.

Схема обеспечивает возможность изменения коэффициента счета путем воздействия на входы управления кода управления коэффициентом счета j1) .

Недостатком известного устройства является его узкая специализация.

Известен также делитель частрты, содержащий счетчик и элемент И, первый вход и выход которого соединены соответственно с управляющим входом делителя частоты и управляющим входом счетчика, счетный вход которого соединен с информационным входом делителя частоты (2).

Недостатком этого делителя частоты являются ограниченные функциональные возможности.

Цель изобретения — расширение функциональных возможностей.

Поставленная цель достигается тем, что в делитель частоты, содержащий счетчик и элемент И, первый вход и выход которого соединены соответственно с управляющим входом делителя частоты и управляющим вхсдом счетчика, счетный вход которого соединен с информационным входом делителя частоты, введен блок памяти с произвольной выборкой, информационные входы которого соединены с выходами счетчика, входы записи данных блока памяти с произвольной выборкой соединены с установочными входами делителя частоты, а первый выход блока памяти с произвольной выборкой соединен с вторым входом элемента И.

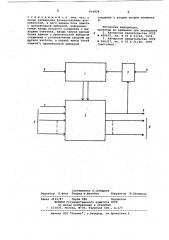

На чертеже показана структурная схема делителя частоты.

Делитель частоты содержит счетчик

1, блок 2 памяти с произвольной выборкой и элемент И 3, первый вход и выход которого соединены соответ834934

5 t0

Формула изобретения

65 ственно с управляющим входом 4 делителя частоты и управляющим входсм счетчика 1, счетный вход которого соединен с информационным входом 5 делителя частоты, информационные входы 6 блока 2 памяти с произвольной выборкой соединены с выходами счетчика, входы записи данных блока 2 памяти с произвольной выборкой сое.динены с установочными входами б. делителя частоты, а первый выход блока 2 памяти с произвольной выборкой соединен с вторым входом элемента И.

Делитель частоты реализует сле-. дующие основные функции: счетчика импульсов с любым целочисленным коэффициентом счета, линии задержки с любым целочисленным значением величины задержки информации .и датчика последовательности с заданным распределением импульсов в периоде.

Перед началом работы производится программирование устройства для реализации заданной функции.

Программирование устройства для реализации счетчика с заданным коэффициентом счета осуществляется следующим образом.

На вход счетчика 1 подается тактовая частота, на вход 7 управления записью-считыванием подается уровень напряжения, соответствующий режиму записи, и в момент накопления счетчиком 1 числа импульсов, равного заданному:коэффициенту счета, на информационный вход б первого разряда блока 2 памяти подается логическая единица. На этом программирование заканчивается.

В работе блок 2 памяти по входу

7 управления записью-считыванием устанавливается в режим считывания и каждый раз при накоплении счетчиком 1 числа, равного коэффициенту счета, на выходе блока 2 памяти появляется сигнал, приводящий счетчик

1 в начальное состояние при наличии разрешающего уровня напряжения на входе 4 устройства. Частота появления сигналов на выходе блока 2 памяти составляет Г = f/k, гдеf- частота повторения импульсов на входе 5; коэффициент с .ета.

Программирование схемы для реализации линии задержки производится аналогично, при этом коэффициент счета выбирается равным заданной величине задержки информации. По окончании программирования на вход б второго разряда блока 2 памяти подается информационная последовательность, первый знак которой будет иметь место на выходе блока 2 памяти через время, определяемое выражением т где Т вЂ” период частоты следования импульсов на входе 5 делителя, коэффициент счета.

На вход 7 управления записьюсчитыванием в работе подается последовательность, тождественная последовательности на входе 5 делителя.

Задержке могут подвергаться (n-1) последовательностей, где и †. число разрядов блока 2 памяти.

Программирование схемы для реализации датчика последовательности с заданным распределением импульсов в периоде производится аналогично программированию счетчика, при этом коэффициент счета выбирается равным периоду повторения последовательности. Кроме того, в процессе программирования во второй разряд блока 2 памяти по входу б записывается один период последовательности заданного вида.

В работе производится считывание последовательности, записанной во второй разряд блока 2 памяти, и на выходе 8 устройства имеет место непрерывная последовательность заданного периода с заданным распределением импульсов- Устройство позволяет реализовать датчик (и-1)последовательностей, где n — число разрядов блока 2 памяти, а также датчик кода разрядности (n-1) и т.д

Помимо укаэанных функций, устройство может применяться для контроля узлов обработки цифровой информации. Например, с его помощью можно контролировать наличие недопустимо-. го числа подряд следующих единиц в последовательности. Для этого при программировании коэффициент счета выбирается равным недопустимому,числу подряд следующих единиц. В работе на вход 5 делителя подается тактовая частота, а на вход 4 — контролируемая последовательность. При появлении каждого нуля в контролируемой последовательности происходит сброс делителя в наЧальное состояние.

Импульс на выходе 9 имеет место лишь в том случае, когда в контролируемой.последовательности. число подряд следующих единиц достигнет величины, недопустимой для данного кода.

Устройство может применяться также для контроля целостности электричес-. ких цепей связи (определяются неисправности типа обрыв и другие, приводящие к эффекту длительного отсут-. ствия сигналов сброса делителя), цепей тактовых частот и т.п.

Делитель частоты, содержащий счетчик и элемент И, первый вход и выход . которого соединены соответственно с управляющим входом делителя частоты и управляющим входом счетчика, счетный вход которого соединен с информационным входом делителя частоты, 834934

Составитель О.Скворцов

Редактор Л.Филь Техред T.Ìàòî÷êà Корректор В.Синицкая

Заказ 4119/87 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, Ж-.35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4 отличающийся тем, что, с целью расширения функциональйых. возможностей, в него введен блок памяти с произвольной выборкой, информационные входы которого соединены с выходами счетчика, входы записи данных блока памяти с произвольной выборкой соединены с установочными входами делителя частоты, а первый выход блока памяти с произвольной выборкой . соединен с вторым входом элемента и.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 499675, кл. Н 03 К 23/24, 1974.

2. Авторское свидетельство СССР

9 556666335577, кл. Н 03 К 21/36, 1975 (прототип).: