Делитель частоты следованияимпульсов c переменным коэффициентомделения

Иллюстрации

Показать всеРеферат

Союз Сееетскня

Соцналнстнческня

Реснубинк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ИТИЛЬСТВУ

< 834936 (61) Дополнительное к авт, сеид-ву— (22) Заявлено 28. 05. 79 (21)2771682/18-21 с присоединением заявки HP— (23) Приоритет—

Опубликовано 300581. Ькзллетеиь М 20

54)М Х> ç

Н 03 К 23/02 .

Государственный комитет

СССР ио делам изобретений и открытий (53) УДК621.373.6 (088.8) Дата опубликования описания (72) Авторы изобретения

В.М.СоЛодуха и И.П.Усачев (71) заявители

Недостатком известного устройства является недостаточно высокое быстродействие, связанное с задержкой момента переключения делителя на другой коэффициент деления.

Цель изобретения — повышение быстродействия.

Указанная цель достигается тем, что в делитель частоты следования импульсов с переменным коэффициентом деления, содержащий счетчик импульсов, блок опознавания, первый вход которого. соединен со счетным входом счетчика импульсов, а выход— с первым входом блока управления, второй вход которого соединен с выходом блока формирования команд, а выход — с управляющим входом счетчика импульсов, и выходной формирователь импульсов, первый вход которого соединен с выходом счетчика импульсов, а второй вход — с выходом блока формирования команд, введены элемент сравнения, запоминающий блок и элемент ИЛИ, первый вход которого соединен с выходом счетчика импульсов,,второй вход — с выходом элемента сравнения, а выход — с вто рым входом блока опознавания, выход которого соединен с первым входом

Изобретение относится к радиотехнике, в частности к цифровым синтезаторам частот и цифровым фильтрам.

Известен делитель частоты следования импульсов с переменным коэффициентом деления, в котором для изменения коэффициента деления входнои частоты импульсов используется счетчиковый делитель с управляемой обратной связью (11.

Недостаток известного устройства невысокое быстродействие.

Наиболее бли..кий к предлагаемому делитель частоты следования импульсов содержит счетчик импульсов, со- 15 стоящий из последовательно соединенных счетных декад, блок опознавания, первый вход которого соединен со входом счетчика, остальные входы — с соответствующими выходами счетных 20 декад, а выход подключен к разрешающему входу блока управления счетчиком, второй вход которого соединен с выходом блока формирования команд, кроме того делитель частоты содержит 25 еще блок формирования выходного сигнала, одни выходы которого соединены с выходами счетных декад, а другие — с выходами блока формйронания команд (2). 30 (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

834936 запоминающего блока, второй вход которого подключен к выходу блока формирования команд и первому входу элемента сравнения, второй вход которого соединен с выходом запоминающего блока.

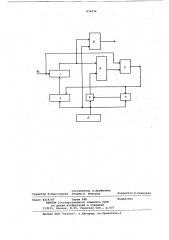

На чертеже приведена структурная схема устройства.

Устройство содержит счетчик 1 импульсов, элемент 2 сравнения, блок 3 опознавания, блок 4 управления, блок 5 формирования команд, !О элемент 6 ИЛИ, запоминающий блок 7, выходной формирователь 8 импульсов.

Устройство работает следующим образом.

Поступающие входные импульсы заполняют счетчик 1 до состояния насыщения,что фиксируется блоком 3, на выходе которого формируется импульс. С появлением импульса на выходе блока 3 разрешаФ ется установка коэффициента деления k+»

L\Р в счетчике 1 путем записи определенного кода числа от блока 5 через блок 4 и одновременно разрешается запись коэффициента деления k » в запоминаю-, щем блоке 7 от блока 5.

Поскольку на обоих входах элемента 2 одинаковая информация, то на его выходе сохраняется сигнал логического "0", которыи не влияет на формирование сигнала логическая "1" на выходе элемента 6 в конце каждого 30 цикла деления. В этом случае сигнал логическая "1" на выходе элемента 6 формируется при появлении сигнала логическая "1" с выхода счетчика 1, т.е. в конце каждого цикла деления. 35

Если же в какой то момент времени внутри цикла деления информация с выхода. блока 5 изменится, что означает переход на другой коэффициент деления kgb, то на входы элемента 2 4р поступит разная информация: с выхода запоминающего блока.7 — о коэффициенте деления k », а с выхода блока 5 — о коэффициенте деления

М д. В результате на выходе элемен ита 2 установится уровень логической единицы, который через элемент 6 пройдет на вход блока 3, что подготовит его к формированию выходного импульса в момен - прихода очередного входного импульса счетчика 1. Импульс сброса с выхода блока 3 разрешит запись в запоминающем блоке 7 информации о k c блока 5 и нрохождения импульса установки счетчика 1

9 с блока 4. 55

Поскольку на обоих входах элемента 2 информация о коэффициенте деления у теперь одинаковая, то на его выходе сформируется уровень логического нуля, который поступает на элемент 6 и не препятствует обычной цикловой работе делителя с коэффициентом деления до тех пор, пока с блока 5 изменится команда на следующий коэффициент деления 1уи т.д.

Использование предлагаемого делителя частоты следования импульсов с переменным коэффициентом деления позволяет получить максимальное быстродействие при переходе с одного коэффициента деления на другой, что очень важно, например, в цифровых синтезаторах частот, где позволяет получить минимальное время перехода с одной частоты на другую.

Формула изобретения

Делитель частоты следования импульсов с переменным коэффициентом деления, содержащий счетчик импульсов, блок опознавания, первый вход которого соединен со счетным входом счетчика импульсов, а выход — с первым входом блока управления, второй вход которого соединен с выходом блока формирования команд, а выход— с управляющим входом счетчика импульсов, и выходной формирователь импульсов, первый вход которого соединен с выходом счетчика импульсов, а второй вход — с выходом блока формирования команд, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в него введены элемент сравнения, запоминающий блок и элемент ИЛИ, первый вход которого соединен с выходом счетчика импульсов," второй вход — с выходом элемента сравнения, а выход со вторым входом блока опознавания, выход которого соединен с первым входом запоминающего блока, второй вход которого подключен к выходу блока формирования команд и первому входу элемента сравнения, второй вход которого соединен с выходом запоминающего блока.

Источники информации, принятые во внимание при экспертизе

1. Лейнов М.Л., Качалуба В.С. и

Рыжков A.Â. Цифровые делители частоты на логических элементах. М., "Энергия", 1975, с.35.

2. Лвторское свидетельство СССР

Р 577685, кл. Н 03 К 23/02, 28.01.76.

834936

Составитель О.Кружилина Редактор М.Лысогорова Техред Н. Майорош

Корректор В.Синицкая

Подписное

Филиал ППН "Патент", r.Óæãoðîä, ул.Проектная,4

Заказ 4119/87 Тираж 988

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.» д.4/5