Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических республик

ОIl ИСAНИЕ „„836681

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. саид-ву )4 63903.9 (22) Заявлено 05.07.79 (21) 2790950/l8-24 (51) М. KJI.

3 с присоединением заявки рй

611 С 1.7/00

3Ьоудлрстеенны6 квинтет

СССР до делам наобретений н отхрытнй (23) Приоритет

Опубликовано 07.06.81. Бюллетень М 2 l

Дата опубликования описания Щ.06.8 (53) УДК681. .327.6 (088.8) (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вы:числительной техники.

Известное постоянное запоминающее устройство (ПЗУ) содержит блоки памяти, выходы которых подключены ко входам выходного регистра, а адресные вхо ды - к выходам регистра адреса, два адресно-числовых регистра, управляющий вход первого из которых соединен с выходом первого разряда регистра адреса, а управляющий вход второго — с выходом второго разряда регистра адреса, выходы первого адресно-числового регис фа соединены с адресными входами первых разрядов блоков памяти, а выходы второго— с адресными входами вторых разрядов блоков памяти, выходы выходного реги-стра подключены к соответствующим входам элемента ИЛИ, первого адресно чисттового регистра, и входам второго ад» ресно-числового регистра, кроме первого f3. .

Недостатком известного устройства является низкая скорость выполнения в нем операции суммирования.

Белью изобретения является повышение быстродействия ПЗУ.

Эта цель достигается тем, что предлагаемое ПЗУ содержит третий и четвертый адресно-числовые регистры, первую и вторую числовые шины. Управляющие вхо ды третьего и четвертого адресно-числовых регистров соответственно соединены с третьим и четвертым выходами регистра адреса, основные входы первого и третьего, кроме первого входа, адресно-числовых регистров соединены с первой числовой шиной, а основные входы второго и четвертого, кроме первого входа, адресно-числовых регистров соединены со второй числовой шиной, дополнительные входы, кроме первого. третьего адресно-числового регистра подсое-. динены к выходам первого, адресно-чйс;лового регистра, дополнительные входы, кроме первого и второго, четвертого адресно-числового регистра — к соответствующим выходам выходного регистра. а выходы третьего и четвертого адресно8366 числовых регистров соединены соответственно с третьими и четвертыми адрес- ными входами блоков памяти.

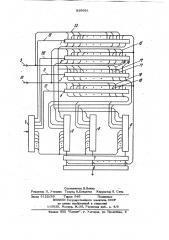

Струкp nan схеМа предложенного усВ; ройства представлена на чертеже.

Устройство содержит первый адресночисловой регистр АЧР l, второй АЧР 2, третий АЧР 3, четвертый АЧР 4, регистр адреса 5, блоки памяти 6, выходной регистр 7, элемент ИЛИ 8, первую 10 числовую цшну 9, вторую числовую ши- ну l0, управляющий вход ll третьего

АЧР, управляющий вход l2 четвертого

АЧР, основные входы первого и третьего АЧР соответственно 13, Х4, основ- 15 ные входы второго четвертого АЧР соответственно l5, l6, дополнительные входы третьего АЧР и четвертого АЧР соответственно l7, 18, управляющие входы первого и второго АЧР соответ- 20 ственно 19,20.

Устройство работает в трех режимах: считывания числа, выполнения логической операции и выполнения операции суммирования.

При считывании числа из ПЗУ адрес числа подается на регистр адреса 5 и с помощью управляющих входов l l, l2, l9, 20 выходы АЧР l,2, 3,4 принимают значения соответствующих разрядов регистра адреса 5 ("0" или "l }, остальная часть адреса поступает непосредственно с регистра адреса 5 на адресные входы блоков памяти 6, и производится считывание числа в выходной регистр 7.

При выполнении логической операции на регистр адреса 5 подается код логической операции, представляющий собой адрес соответствую40 щей таблицы. При этом два первых разpalta адреса не используются; на первом

АЧР 4. и втором АЧР 2 устанавливаются числа, над которыми необходимо вы45 полнить логическую операшпо; выходы третьего АЧР 3 и четвертого АЧР 4 с помощью управляющих входов ll и l2 принимают значения соответствующих разрядов регистра адреса 5, и производится считывание результата на выходной

50 регистр 7.

При выполнении операции суммирования через числовые шины 9 и l0 устройства на адресно-числовые регистры 1,2, 3,4 подаются ащлежащие суммировании

55 числа: j(Х,ф g Х1 Х;,,,,.. - X

81 4 где „и У„- цифры. двоичных колов чисел Х и У, причем на третий АЧР 3 и четвертый АЧР 4 со сдвигом на один разряд в сторону старшего разряда.

На регистре адреса 5 устанавливается адрес табпицы частичной суммы: $ 5„S ..51. 5 где, 9. - цифра 1 -го разряда частичной суммы, при этом четыре первых разряда не используются. Таблица частичной суммы состоит из И одинаковых таблиц, предварительно записанных во все блоки памяти 6 в соответствии с формулой

s„=((x„, ц, х„.„,ч„.„) = х„. Оч„- e „.+ч„„

Производится считывание, частичной суммы S на выходной регистр 7. В разрядных сечениях устройства выполняется логическое преобразование

На регистре адреса 5 устанавливается адрес таблицы частичного переноса

P= Р Р --. Р;." и, z ne P„. -grampa

1 -го разряда частичного переноса .

Таблица частичного переноса состоит из

И одинаковых таблиц предварительно записанных во все блоки памяти 6 в соответствии с формулой

Р1= (1,11,< 4-q У1 1) = Г;И„„Y„4

Частичная сумма 5 передается на первый

АЧР 3. без изменения.

Производится считывание слова пере-. носов P на выходной регистр 7.

Если на выходе элемента ИЛИ 8 устанавливается сигнал .3. (слово переносов не равно нулю ), то слово переносов с регистра 7 передается на второй

АЧР 2 со сдвигом на один разряд и на четвертой АЧР 4 со сдвигом на два разряда в сторону старшего разряда, а частичная сумма передается с первого

АЧР l на третий АЧР 3 со сдвш ом на один разряд в сторону стершего раз« ряда.

Если на выходе элемента ИЛИ 8 устанавливается сигнал 0 (слово пе реносов равно нулю), то находящаяся на первом АЧР l частичная сумма является результатом суммирования.

Время суммирования чисел прибли-, зительно в два раза меньше, чем в црототипа, так как в предлагаемом устройстве при вычислении частичной суммы

5 83668 l

6 сразу учитываются все переносы, распро- регистров соответственно соединены с страняющиеся не более -нем на один третьим и четвертым выходами регистра !

P "4 адреса, основные входы первого и треДля таблиц частичных сумм и частич«тьего, кроме первого входа, адресно-. ных переносов требуется объем памяти 5 числовых регистров соединены с первой не более 32 ячеек памяти. Но ей о можно числовой шиной, а основные входы втозначительно сократить, так как таблицы рого и четвертого, кроме первого входа, частичных сумм и переносов частично адресно-числовых регистров соединены совпадают с таблицами логических опера- со второй числовой шиной, дополиительций. t0 ные входы, кроме первого, третьего ад-, ПЗУ может быть включено в состав ресно-числового регистра подсоединены информационно логический или управляю- к выходам первого адресно-чкспового щей системы в качестве специализиро- регистра, дополнительные входы, кроме ванного блока, предназначенного для первого и второго, четвертого адреснохранения информации, выполнения логи- 15 числового регистра — к соответствующим ческих операций и операщИ суммирования. выходам выходного регистра, а выхо е. ф о р м у л а и з о б р е т е н и я ды третьего и четвертого адресно-чис;

Постоянное запоминающее устройство ловых регистров соединены соответственно авт. свид. № 639019, о т л и ч а ю- но с третьими и четвертыми адресными щ е е с я тем, что, с цепью повышения zp входами блоков памяти. быстродействия устройства, оно содер= Нс точники информ &ции, жит третий и четвертый адресно-число- принятые во внимание при экспертизе вые регистры, первую и вторую число- 1. Авторское свидетельство СССР вые шины, при этом управляющие входы ¹ 539019„кл. Gl l С l7/00, l976 третьего и четвертого адресно-числовых 25 (прототип) .

83668l

Составитель В.ВакарРедактор Л. Утехина Техреду Н.Ковалева Корректор H. Степ

Заказ 3122/39 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 ф nnn a W"; . У.род. у. Прая, 4