Цифровой частотный детектор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. сеид-ву (22) Заявлено 291278 (21) 2704686/18-09 (Я)М. Kll. с присоединением заявки HP (23) Приоритет

Н 04 L 27/14

Государственный комитет

СССР во делам изобретений н открытий

Опубликовано 07.0681. Бюллетень N 21

Дата опубликования описания 1006$1

М) УЛК 621. 376. . 9 (088. 8) 1

° -, ) Ф - ) I

2 (72) Автор изобретения

В. A. Могунов

1! ! 4J и I (I ! (71) Заявитель (54) ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР

М

Изобретение относится к технике связи и может использоваться для детектирования сигналов частотной телеграфии ЧТ,. у которых разность периодов частот нажатия и отжатия сравнима с периодом опорной частоты.

Известен цифровой частотный детектор, содержащий. определитель расстройки, выполненный в виде последовательно соединенных ключа, делителя частоты, счетный вход которого является входом опорного сигнала, и

Д-триггер, при этом выход делителя частоты подключен к информационному входу Д-триггера, а также фильтр ниж- 15 них частот (1).

Однако в известном цифровом частот- . ном детекторе при сравнимости разности периодов частот нажатия и отжатия .с периодом опорной частоты не обеспечивается достаточная точность детектирования, т.е. преобладания детектированного ЧТ-си"нала велики. Этот недостаток вызван временными погрешностями работы делителя частоты из-за несинфазности сигналов опорной и рабочей частот.

Цель изобретения — повышение точности детектирования.

Для этого в цифровой частотный детектор, содержащий определитель расстройки, выполненный в виде последовательно соединенных ключа, делителя частоты, счетный вход которого является входом опорного сигнала, и

Д-триггер, при этом выход делителя частоты подключен к информационному входу Д-триггера, а также фильтр ниж-.. них частот, введены п дополнительных определителей расстройки, распределитель импульсов, формирователь импульсов опроса и мажоритарный элемент, при этом входы распределителя импульсов и формирователя импульса опроса объединены и являются сигнальным входом детектора, выходы распределителя импульсов подключены к первым входам ключей соответствующего определителя расстройки, вторые входы всех ключей., объединены и подключены к выходу формирователя импульса опроса, выход ключа соединен с тактовым входом

Д-триггера в каждом определителе расстройки, а мажоритарный элемент включен .между выходами определителей расстройи и входом фильтра нижних частот.

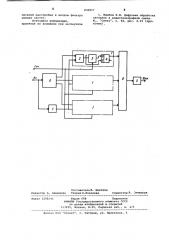

На чертеже представлена. структурная электрическая схема предлагаемого цифрового частотного детектора. ю

836817

Формула изобретения

Цифровой частотный детектор содержит определитель расстройки 1, ключ

2, делитель частоты 3, Д-триггер 4, фильтр нижних частот 5, распределитель импульсов б, формирователь импульса опроса 7 и мажоритарный элемент 8.

Цифровой частотный детектор работает следующим образом. На вход устройства приходит ЧТ-сигнал, ограниченный по моментам перехода через нуль. На выходах распределителя импульсов б формируются импульсы„ длительность которых равна периоду входного сигнала, а частота следования равна величине f>< /и, где n — коэффициент пересчета, равный числу определителей расстройки 1. Формирователь импульса опроса 7 формирует короткий импульс, совпадающий с передним фронтом входного ЧТ-сигнала.

При совпадении на входе ключа 2 импульсов распределителя импульсов б и формирователя импульса опроса 7 на выход ключа 2 проходит импульс опроса и сбрасывает в исходное состояние делитель частоты 3. На вход делителя частоты 3 поступают импульсы опорной частоты. Коэффициент деления делителя частоты 3 выбирается таким образом, чтобы оп <с

К 2.п где f „ — спорная частота, К вЂ” коэффициент деления делителя частоты 3, — средняя частота входного ЧТ-сигнала. B этом случае полупериод выходного сигнала делителя частоты 3 равен периоду выходного сигнала распределителя импульсов 6, при условии поступления. на его вход частоты fc> .

Если на вход устройства поступает частота меньше f p, то к моменту прихода очередного импульса опроса делиЯО тель частоты 3 не изменит своего состояния (т.е. íà его выходе будет сигнал "О") и одновременно со сбросом делителя в Д-триггер 4 будет записано это состояние. 45

Если на вход, устройств приходит частота больше f

Д-триггеров 4 всех определителей расстройки 1 поступают на входы мажоритарного элемента 8, который служит для выделения модулирующего сигнала. Для принятия решения.о наличии на входе устройства одной из двух (отжатия или нажатия) частот необходимо. проанализировать значение выхо- 6О дов всех определителей расстройки 1.

В мажоритарном элементе 8 суммируют=я зна. ения "О" и "1", поступающие на его вход, и значение сигнала на выходе мажоритарного элемент 8 определя- 65 ется соотношением входных сигналов.

Если большинство входных сигналов ."1", то на выходе элемента 8 появится "1" и наоборот. Определители расстройки 1 выдают сигналы на входы мажоритарного элемента 8 не одновременно. Функции памяти в предлагаемом устройстве выполняют Д-триггеры 4.

Сигнал на выходе Д-триггера 4 хранится до появления на тактовом входе.

Д-триггера 4 следующего импульса опроса, когда значение сигнала на выходе Д-триггера 4 либо подтверждается, либо меняется на противоположное. уменьшение временных преобладаний, а значит и повышение точности детектирования, достигается за счет увеличения в п раз времени измерения расстройки и применения и определителей расстройки 1, работающих со сдвигом в один период друг относительно друга. В предлагаемом детекторе результат сравнения может быть получен в каждый период входного сигнала, в то время как в известном устройстве для получения результата одного сравнения необходимо несколько периодов входной частоты.

Технико-экономическая эффективность предлагаемого цифрового частотного детектора по сравнению с известным состоит в повышении качества восстановления модулирующего сигнала, т.е. повышении точности детектирования, когда разность периодов частот нажатия и отжатия сравнима с периодом опорной частоты.

Цифровой частотный детектор, содержащий определитель расстройки, выполненньтй в виде последовательно соединенных ключа, делителя частоты, счетный вход которого является входом опорного сигнала, и Д-триггер, при этом выход делигеля частоты подключен к информационному входу Д-триггера, а также фильтр нижних частот, отличающийся тем, что, с целью повышения точности детектирования, в него введены и дополнительных определителей расстройки, распределитель импульсов, формирователь импульса опроса и мажоритарный элемент, при этом входы распределителя импульсов и формирователя импульса опроса объединены и являются сигнальным входом детектора, выходы распределителя импульсов подключены к первым входам ключей соответствующего определителя расстройки, вторые входы всех ключей объединены и подключены к выходу формирователя импульса опроса, выход ключа соединен с тактовым входом Д-триггера в каждом определителе расстройки, а мажоритарный "-лсмент включен между выходами ярс-л! °вЂ”

836817

Составитель В. Цветков

Редактор A. Ахмедова Техред Н. Ковалева Корректор В. иницкая

Тираж 698 Подписное

ВНИИПИ Государственного коМитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3208/46

Филиал ПШ1 "Патент", г. Ужгород, ул. Проектная, 4 лителей расстройки и входом фильтра нижних частот.

Источники информации, принятые во внимание при экспертизе

1. Машбиц Л.М. Цифровая обработка сигналов в радиотелеграфной связи.

М., "Связь", с. 48, рис. 2.21 (прототип).