Стабилизированный однотактныйконвертор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУСоюз Советскими

Социалистических

Республик (iij838683 (61) Дополнительное к авт, саид-ву (22) Заявлено 26.10.79(21) 2835204/24-07 с присоединением заявки H (23) Приоритет

Опубликовано 150681. Бюллетень No 22

Дат4 опубликования описания 15 . 06 . 81 (51)М. Кл

G 05 F 1/56

Н 02 М 3/335

Государственным комитет

ССС P но делам изобретений и открытий (53) УДК 621. 316. .722.1 (088.8) (72) Авторы изобретения

Н.А. Толмириди, M.À. Ягупов и Н.Е. Комраков (71) Заявитель (54) СТАБИЛИЗИРОВАННЫ1Ч ОДНОТАКТНЕЙ КОНВЕРТОР

20

Изобретение относится к электротехнике и может быть использовано в качестве вторичного источника питания.

Известен стабилизированный одно.тактный конвертор, содержащий усилитель мощности с трансформатором, выходная обмотка которого через выпрямитель и фильтр подключена к выходным клеммам, блоКи запуска и управления (1).

Однако данный конвертор обладает недостаточно высоким КПД,обусловленным большими потерями в силовом тран- 15 зисторе усилителя мощности.

Наиболее близким к изобретению является конвертор, содержащии усилитель мощности, входом питания подключенныи к входным клеммам, вторичная обмотка трансформатора которого через выпрямитель и фильтр соединена с выходными клеммами,формирователь управляющих импульсов, вход которого подключен к выходным клеммам, управляющии трансформатор,первая обмотка которого подсоединена к управляющему входу усилителя мощности, и первыи дополнительный транзистор, коллектор которого подключен 30 к первому выводу второй обмотки управляющего трансформатора f2).

К его недостаткам следует отнести недостаточно высоки КПД и малую надежность, что ot)óñëoâëåío необходимостью расчета цепей насыщения и запирания силового транзистора усилителя мощности с учетом большого технологического и температурного разбросов его характеристик.

Цель изобретения — повышение надежности и КНД устройства.

Поставленная цель достигается тем, что в стабилизированном однотактном конверторе выход формирователя импульсов через введенный инвертор соединен с одним входом введенного

I узла совпадения, другои вход которого подключен к выходу выпрямителя, выход введенного узла совпадения через первый введенный импульсныи усилитель с двухтактным выходным каскадом соединен с базой первого дополнительного транзистора, эмиттер которогo через первый введенный токозада-. ющий резистор подключен к первой входнои клемме, выход формирователя импульсов через второи введенный импульсный усилитель с двухтактным выходным каскадом соединен с базой

838683 второго дополнительного транзистора, коллектор которого подключен к первому выводу третьен обмотки управляющего трансформатора, а эмиттер че рез второй введенный токозадающии резистор — к первой входнои клемме, вторые выводы второй и третьей обмоток управляющего трансформатора подключены к второй входнои клемме, первые выводы питания первого и второго введенных импульсных усилителеи соединены с первой входной клеммои, а вторые выводы питания через вспомогательныи стабилизатор — с второй входной клеммой.

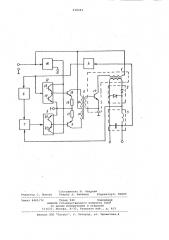

На чертеже представлена схема предлагаемого стабилизированного однотактного конвертора.

Однстактный стабилизированный конвертор содержит усилитель 1 мощности с выходным трансформатором, вторичная обмотка которого через выпрямитель 2 и фильтр 3 соединена с выходными клеммами, формирователь 4 импульсов, управляющий трансформатор 5, вход формирователя 4 импульсов соединен с выходными клеммами„ а выход через инвертор 6 — с первым входом схемы 7 совпадения, второй вход которой подключен к выходу выпрямителя 2, выход схемы 7 совпадения соединен со входом первого импульсного усилителя 8, выход которого соединен с базой первого дополнительного транзистора 9, коллектор которого соединен с второй обмоткой 10 трансформатора 5, а эмиттер через первый токозадающий резистор 11 — к первой входнои клемме, выход формирователя соединен также со входом второго импульсного усилителя 12, выход которого соединен с базой второго дополнительного транзистора 13, коллектор которого подключен к третьей обмотке 14 трансформатора 5, а эмиттер через второй токозадающии резистор 15 к первой входной клемме. По цепи питания первый и второй импульсные усилители подключены к выходу вспомогательного стабилизатора 16. Вторые выводы второй 10 и третьей 14 обмоток управляющего трансформатора 5 подсоединены к второй входной клемме, а первая обмотка подключена к управляющему переходу силового транзис-. тора 17 усилителя 1 мощности. Выходные каскады импулbcных усилителей 8 и 12 выполнены по двухтактной схеме соответственно на транзисторах 18, 19 и 20, 21.

Работает устройство следующим образом.

Усилитель 1 мощности с помощью формирователя 4 осуществляет преобразование постоянного входного напряжения в импульсное, которое затем выпрямляется выпрямителем 2 и через

Г фильтр 3 поступает на входные клеммы, причем длительность выходных ,импульсов формирователя 4 такова, что при действии всех дестабилизирующих факторов выходное напряжение конвертора остается постоянным.

При появлении на выходе формирователя 4 импульсов управляющего сигнала выходной транзистор 19 импульс0oI о усилителя 12 запирается, а транзистор 18 насыщается. Выходное напряжение стабилизатора 16 через транзистор 18 усилителя 12 прикладывается к базе транзистора 13 относительно общего входного вывода, создавая падение напряжения на втором токозадающем резисторе 15. Транзистор

13 открывается и через третью обмотку 14 управляющего трансформатора 5 течет ток, что приводит к формированию на обмотке 14 управляющего импульса. Снимасмый с перво обмотки трансформатора 5 управляющии импульс прикладывается непосредственно к переходу база-эмиттер транзистора

17 усилителя 1 мощности, открывая его на время длительности импульса.

Ток в первичной обмотке 14 транс— форматора 5 определяется только значением выходного напряжения стабилизатора 16 и величиной токозадающего резистора 15 и не зависит от параметров транзистора 17.

Таким образом, в предлагаемом конверторе обеспечивается постоянство величины тока базы транзистора

17, усилителя 1 мощности независимо от разброса значений напряжения базаэмиттер в транзисторе 17. Это позволяет исключить устанавливаемый в цепи базы транзистора усилителя мощности для компенсации разброса напряжения база-эмиттер резистор и связанные с ним потери мощности на управление, что повышает ЕПД всего устройства.

Одновременно импульсы с выхода формирователя 4 импульсов через инвертор 6 поступают на вход схемы 7 совпадения, в которой осуществляется сложение импульсов с выхода инвертора 6 с импульсами, поступающими с выхода выпрямителя 2. Так как сложение импульсов с выхода выпрямителя 2 осуществляется с инвертированными импульсами формирователя 4, то передний фронт импульсов с выхода схемы 7 совпадения. формируется одновременно с задним фронтом импульса с выхода формирователя 4. Импульс с выхода схемы 7 совпадения поступает на вход первого импульсного усилителя 8. При этом транзистор

20 запирается, а транзистор 21 открывается. Напряжение с выхода стабилизатора 16 напряжения через открытыи транзистор 21 поступает на базу первого дополнительного транзистора 9. Транзистор 9 отпирается, создавая на первом токозадающем ре838683 зисторе 11 падение напряжения, что приводит к протеканию тока через дополнительную обмотку 10 и формированию обратного тока базы через транзистор 17, чем достигается его форсированное запирание и уменьшение динамических потерь мощности. Формирование импульса на выходе схемы 7 совпадения заканчивается одновременно с окончанием импульса напряжения на выходе выпрямителя 2.

После того как процесс рассасывания закончится, транзистор 17 закрывается и напряжение на выходе выпрямителя 2 становится равно нулю.При этом заканчивается формирование импульса на выходе схемы 7 совпаде- 15 ния. Таким образом, формирование .импульса на выходе схемы 7 совпадения начинается одновременно с окончанием управляющего импульса, поступающего с формирователя 4, а за- 2О вершается одновременно с окончанием процессов рассасывания в транзисто-. ре 17. Следовательно, в предлагаемом устройстве длительность рассасывающего импульса автоматически поддерживается равной времени рассасывания.

После запирания транзистора 17 усилителя 1 мощности транзисторы

18 и 21 импульсных усилителей 8 и 12 заперты, а транзисторы 19 и 20 насыщены, что повышает экономичность устройства.

Таким образом, в предлагаемом конверторе при воздействии всех дестабилизирующих факторов, а именно: изменении входного напряжения, температуры окружающей среды,технологического разброса напряжения база-эмиттер транзистора 17, обеспечивается с необходимой точностью 4О постоянство базового тока транзистора 17, что повышает экономичность устройства.

Независимо от разброса значений времени рассасывания транзистора

17 и изменении режима его работы вследствие изменения условий эксплуатации длительность рассасывающего импульса автоматически поддерживает.— ся равной времени рассасывания тран- . зистора 17. Это исключает необходимость подбора элементов схемы, что значительно упрощает процесс настройки и повышает надежность и технологичность изделия.

Формула изобретения

Стабилизированный однотактный конвертор, содержащий усилитель мощности, входом питания подключенный к входным клеммам, вторичная обмотка трансформатора которого через выпрямитель и фильтр соединена с выходными клеммами, формирователь управляющих импульсов, вход которого подключен к выходным клеммам, управляющий трансформатор, первая обмотка которого подсоединена к управляющему входу усилителя мощности, и первый дополнительныи транзистор, коллектор которого подключен к первому выводу второи обмотки управляющего трансформатора, отличающийся тем, что, с иелью повышения надежности и КПД, выход формирователя импульсов через введенныи инвертор соединен с одним входом введенного узла совпадения, другой вход которого подключен к выходу выпрямителя, выход узла совпадения через первый введенный импульсный усилитель с двухтактным выходным каскадом соединен с базой первого дополнительного транзистора, эмиттер которого через первыи введенный токозадающий резистор подключен к первой входной клемме, выход формирователя импульсов через второй введенный импульсныи усилитель с двухтактным выходным каскадом соединен с базои второго дополнительного транзистора, коллектор которого подключен к первому выводу третьей обмотки управляющего трансформатора, а эмиттер через второй введенный токозадающии резистор — к первой входной клемме, вторые выводы второй и третьей обмоток управляющего трансформатора подключены к второй входной клемме, первые выводы питания первого и второго введенных импульсных усилителей соединены с первой входной клеммой, а вторые выводы питания через вспомогательныи стабилизатор — c второй входной клеммой.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 609110, кл. G 05 F 1/56, 1978.

2. Авторское свидетельство СССР

Р 599321, кл. H 02 М 3/335, 1978.

838683

Составитель Ю. Опадчий

Техред A. Бабинец КорректорО. Билак

Редактор С. Лыжова

Тирад 940 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4445/72

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4