Устройство защиты источников питания

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски)с

Социалистически>!

Республик

f»>838685 (6!) Дополнительное к авт. свид-ву— (22) Заявлено 29.03.79 (21) 2757237124-07 с присоединением заявки №вЂ” (23) Приоритст— (5 1 М . 1х,!. (з 05 1 1,58

Гасударственный комитет па делан юобретеннй и птхрытнй

Опубликовано !5.0б.81. В»о.)г)с! ciil. ¹ 2"

Дата опубликования описан)!>! 2)5).0().81 (53j,х Д1х i2l.31(i. .722.! (088.8! (72) Автор изобретения

Н. A. Соцков (7I) Заявитель (54! х>СТРОИСТВО ЗАШИТЫ ИС1())11111ÊÎÂ 111! 1 А!1 ИЯ

Изобретсli c о.сносится к радиоэлектроникс li можст быть использовано во вторичных ис)о п)иках ш)тания (ВИП) рядиоэлектpoIIIIolt i!fffiI>ратуры и в системах автоматики.

Извсст !с> устройство защиты ВИП по оку Ilя г!>узки ii выходному на пряжени)о, содер>кащсс дифференциальный усилите. il с токостяб))лизирук)щим транзистором, логи:)с(кую схсъ)у ИЛИ, датчик тока ((J.

Няис)(>лес олизким техническим решенисм к нзооретснию является устройство защиты ис гочпиков с)ита))ия, содержащее ус))литель датчика тока, дифференциальный ус!f,lèòcël с источником опорного напряжения, выполненный на трех транзисторах, вход первоп> из которых подключен через резистор к входному выводу, усилитель обратной связи на транзисторе с развязывающим диоjo)f и входным резистивным делителем, первый вывод которого подключен к общей шине, средняя точка подключена к базе укя)a«iioio транзистора, а выход усилителя оорятной связи подключен ко входу второго транзистора дифференциального усилителя (2) .

Недостатками данного устройства являются низкая надежность, поскольку время

lI МpО ВСII!> Ср С)О >! тl>! Вf!! I!! я >,"с TpОЙ СTВС! Зя ПСI)ты по токх н>>гр зки II пс> нижнемм ),ровнк)

KOIITPO,IIf!)>, CМОГО iI3IlPHЖ IIII>I II(ЛЬЗЯ PCI Хлировять раздельно, зяпгрудненя и очень низка To÷ность >,стя!гонки порога срябяты5 вания по нижнему урс>вню, имеет место взаимная зависимо Tb порогов срабатывания iio току перегрузки и нижнему уровню контролируемого напряжения.

Цель изобретения — повышение надежности и, как следствие. расширение облас1р ти применения и возможности микром)(ниятюризацпи.

Цель достигается тем, что в устройстве защиты источников питания. выход усилителя датчика тока подключен через введенный д>)од ко второму выводу входного резистивного делителя, запунтированного введенным конденсатором, причем вход третьего транзистора шиффер 1! f!H2ëbIIoão усилителя подключен через второй резистор к входному выводу, выход второго транзистора под20 ключен к выходному выводу, а выход первого транзистора подключен ко входу второго транзистора д! фференциального усилителя, кроме того, эмиттер транзистора усилителя обратной связи подключен к общей

838685

Формула «добр -; -«<: ч

so

55 точке эмиттеров первого и третьего транзис торов дифференциального усилителя.

Кроме этого, между общей шиной питания и эмиттерами первого и третьего транзисторов дифференциального усилителя включен источник опорного напряжения.

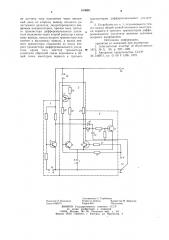

На чертеже приведена принципиальная электрическая схема устройства зашиты источников питания.

Устройство содержит усилитель 1 датчика тока, выполненный ны транзисторе 2, дифференциальный усилитель 3, выполненный на транзисторах 4 — 6 с источником 7 опорного напряжения, и усилитель 8 обратной связи, выполненный на транзисторе 9 и диодах 10 и 11. Устройство зашиты имеет выводы 12 для подключения датчика тока, входные выводы 13. выходные выводы 14 и источник 15 питания, резисторы 16 — 20, резистивный делитель 21, конденсатор 22, резистор 23.

Устройство работает следующим образом.

В исходном состоянии при номинальном токе нагрузки, что соответствует номинальному падению напряжения на датчике тока и при номинальном значении контролируемого напряжения на выводах 13 транзистор

2 открыт, так как падение напряжения на базовом резисторе этого транзистора выше падения напряжения на датчике тока, и разность этих напряжений, достаточная для открывания транзистора 2, положительная.

При этом переход коллектор-эмиттер транзистора 2 шунтирует один вход (анод диода 10) усилителя 8 обратной связи, в результате чего транзистор 9 заперт. Транзистор 4 дифференциального усилителя 3 открыт, так как контролируемое напряжение на выводах ! 3 превышает минимальный допустимый уровень, который выше величины опорного напряжения 7, и разность напряжения на переходах база-эмиттер транзистора 4 положительная, а к переходам база-эмиттер транзистора 9 приложено опорное напряжение 7 в запирающей этот транзистор полярности.

Транзистор 6 дифференциального усилителя заперт, так как напряжение на егс входе не превышает максимального допустимого значения, определяемого опорным напряжением 7. Транзистор 5 также заперт, так как заперты транзисторы 6 и 9. При этом на выходе 14 устройства защиты отсутствует сигнал, что соответствует нормальным уровням 3-х контролируемых параметров: току нагрузки, максимальному и минимальному уровням контролируемого напряжения.

При увеличении тока нагрузки напряжение на датчике тока в полярности, запирающеи транзистор 2, увеличивается, при достижении током нагрузки заданного максимального уровня транзистор 2 запирается. При этом с выхода усилителя 1 датчика тока (коллектор транзистора 2) на второй вход усилителя обратной связи (анод диода 0) поступает сигнал, трансзитор 9 открывается открывая транзистор 5, а последний

4 открывает транзистор 6. Hd выходе 1- с ройства защиты появляется сигнал il<.ис: эа".. ности. При этом транзисторы 6 и 5 ост;:;

Для возвращения устройст;а за«<и исходное состояние необходимо

При снижении контролируемого на ..ряж"!!i:;i на выводах 13 ниже допуст:!мо: о уров <я транзистор 4 запирается, на c! <> ко«»<«ктор< появляется напряжение, которое носl «ас< на первый вход усилителя 8 обратной св .зи (анод диода 11). Транзистор 9 открывается. Далее устройство защиты работа<.:: -ак же как и при токовой iiepe

Положительный эффект от исш:.<ь. >-.: ния предлагаемого устройства зак.<юча«тс l в повышении надежности, обеспечивас",го :. а счет того, что уровни всех трех ко< тро, пlp, мых параметров (тока перегт зки и.<и; прот". кого замыкания, верхнего и нижнelо .<гчней напряжения) можно ус;апавливат=: «з— дельно друг от друга с высокой -".!!<;:E,"., тОчнОсти. IpEE 3TQM устянонкя 1)<)a!lк батывания по одному параметр. I;«. :к- зывает влияния на ранее

Кроме того, максимальный и мини.,!».1<, ный уровни контролируемo!-

1. Устройство защиты и:, гчкнкон ния, содержащее усилитель la i чика < ька дифференциальный усилитель с исто»а»к<.; опорного напряжения, выполненный::;i р х транзисторах, вход первого из которь»-: <их<ключен через резистор к входном!, вь«,";:д<. усилитель обратной связи:а гра:.з< «то,i«;. развязывающим диодсм и в,:.Однь< 1 роз::. и::. ным делителем, первый вьнк:д котo:: ::.;: .i .: ключен к общей шине,: рс цl EIEI .; о; к; ключена к базе указан-гого 1ра,ганс-: ор:-., ..< Нь ход усилителя обратной «вяз.< подключ< . ):. входу второго транзисгора дифф«р:,, <:.;:-:.. ь ..: го усилителя, отла <аюи1еее» т;..хк лью повышения надежности. Ны. :.,i .: :<т

838685

Составитель С. Горбачева

Редактор Л. Конецкая Техред А. Бойкас Корректор М. Шароши

Заказ 4446/73 Тираж 940 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и откбытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 ля датчика тока подключен через введенный диод ко второму выводу входного резистивного делителя, зашунтированного введенным конденсатором, причем вход третьего транзистора дифференциального усилителя подключен через второй резистор к входному выводу, выход второго транзистора подключен к выходному выводу, а выход первого транзистора подключен ко входу второго транзистора дифференциального усилителя, кроме того, эмиттер транзистора усилителя обратной связи подключен к общей точке эмиттеров первого и третьего транзисторов дифференциального усилителя.

2. Устройство по и. 1, отличающееся тем, что между общей шиной питания и эмиттерами первого и третьего транзисторов дифференциального усилителя включен источник опорного напряжения.

Источники информации, принятые вг внимание при экспертизе

1. International JourhaI of Electronics»

1972, № 5, 33, р. 597 — 599.

2. Авторское с в и детел ьство С С С Р № 546871, кл. G 05 F 1/58, 1975.