Управляемый распределитель импульсов

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е ()840860

ИЗОБРЕТЕНИЯ

COIO3 COIOTCNNX

Социалистических

Республмм

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. саид-ву(22) Заявлено 03.09 79 (21) 2815360118-24 (5! )М. Кл.

6 06 Г 1/04 с присоединением заявки И—

6Ьеудеретеенный кемнтет

СССР (23) Приоритет(53) УДК 681.3 (088.8) Опубликовано 23.06.81. Бюллетень Эй 2

Дата опубликования описания 28;06.81 ае лелем нэебретеннй н втерытнй (72) Автор. изобретения е

А. Г. Костюковский (ф ,.Ф

Белорусский филиал Государственного нау*6тв. .исследовательского института им.

Г.М.Кржижановского (7I ) Заявитель (S4),УПРАВЛЯЕМЫЙ РАСПРЕДЕЛИТЕЛЬ

ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике.

Известен датчик тактов, содержащий

И -разрядный регистр, каждый разряд которого состоит из двух триггеров, причем единичные входы первых триггеров каждого разряда соединены с нулевыми выходами вторых триггеров того же разряда, а единичные выходы со входами тактовой частоты устройства (11..

Недостатком такого датчика является о периодический пропуск входных тактов.

Причем число пропущенных тактов тем больше, чем меньшее число каналов в работе.

15 Наиболее близким к предлагаемому по технической сущности является распределитель импульсов в котором датчик тактов содержит дополнительный триггер и элемент НЕ, что позволяет управлять числом каналов распределения импульсов при отсутствии неиспользуемых тактов.

Однако при управлении таким распределителем импульсов возникает существенный недостаток, заключакацийся в том, что первый тактовый импульс, в зависимости от коэффициента пересчета, появляется на разных выходах устройства, что не позволяет применить известный распределитель импульсов в схемах с переменной структурой управления от микропроцессоров или ЭВМ, поскольку нарушается временная последовательность выполнения необходимых операций.

Бель изобретения - расширение области применения устройства, за счет привязки первого тактового импульса к первому выходу устройства при любом коэффициенте пересчета.

Указанная цель достигается тем, что каждый разряд регистра содержит элемент

И-НЕ и триггер, выход которого соединен с первым входом элемента И-НЕ предыдущего разряда, выход триггера каждого рвз ряда соединен со вторым входом элемента И-НЕ последующего разряда единичные выходы, ит - разрядного регистра coedsиены с соответствуюшими входами мупь3 8408 типлексора, выход которого соединен с единичным входом триггера установки в

0" w -разрядного регистра, единичный ,выжод которого соединен со счетным входом триггера относительности, а нулевой выход соединен с нулевыми установочными входами и| -разрядного регистра, при этом единичный и нулевой выходы триггера относительности соединены с управляющими входами коммутатора, информаци- 10 оннь1е входы которого соединены с выхо .дами формирователя двух серий импульсов, при этом один вывод коммутатора соединен с третьими входами элементов

И-НЕ всех нечетных разрядов регистра, 15 а другой выход — с третьими входами элементов И-НЕ всех четных разрядов ре гистрв, тактовый вход мупьтинпексора соединен с входом формирователя двух серий импульсов и через элемент HE сое-. 20 динен с нулевым входом триггера установки в 0" а -разрядного регистра а нулевой вход триггера относительности соединен с младшими разрядами управляющего входа мультиплексора. 25

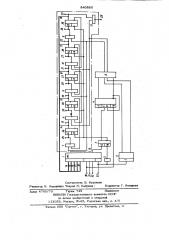

Нв чертеже приведена схема распределителя импульсов.

Упцввпяемый распределитель импуль. .cqa содержит мультиплексор 1, выход которого соединен с единичным входом триг- Зо гера установки в "0" регистра 2,. твктоabN вход му пь тип пексорв " через элемент

ЙЕ 3 соединен с; входом триггеps установки в "0 регистра 2, единичж ный выход триггера установки в 0" регистра 2 соединен со счет;:ым входом триггера 4- относительности, в нупевой вход его соединен с упрввпяюшим входом младшего разряда мупьтиппексорв 1,входы формирователя 5 двух серий импульсов 40 соединены с тактовым входом мупьтиппек. ора 1, в выходы соединены с упрввпяюшими вхОдвми КОммутвтОрв ба при этОМ один выход коммутатора 6 соединен со входами элементов И HE 7-9, всех нечет й5 ных разрядов регистра 10, в другой выход - со входами схем И-HE 11-13 всех, четных разрядов, кроме того, единичные выходы регистра 10 соединены соответст= венно со входами И-HE старших разрядов, ы в нулевые выходы - соответственно со входами схем И-НЕ младших разрядов, единичные выходы 14-18 регистра 10 соединены с соответствующими входами

55 мультиплексора 1.

В исходном состоянии на выходе триггера установки в 0" регистра 2 вырабатывается "0", который устанавливает ре80 гистр 10 а 0". При этом на выходах

19 23 устанавливается О, а на выходах 24-29 — 1, На выходные шины 3032 приходит управляющая команда в параллельном коде с весами соответственно 1»2-4. На шины 30 и 32 приходит 1 на шину 31 — О, что соответствует коэффициенту пересчета пять и соответственно пяти каналам распределения импульсов.

С приходом тактовых импульсов (ТИ). на шину 33 триггер установки в 0 регистра 2 вырабатывает 1.", которая разрешает работу регистра 10, выполненного нв триггерах 34-38. Одновременноформироввтепь 5 двух серий импульсов вырабатывает две серии импульсов, сдвинутых друг относительно друга нв 180 ТИ1 и ТИ2, ТИ1 и ТИ2 поступают на входы коммутатора 6 импульсов управления, нв другие входы поступают потенциальные сигналы с выхода триггера 4 относительности, который включен по схеме со счетным входом и перебрасывается по сигналам единичного выхода триггера установ ки в "0" регистра 2.

1 .1

Допустим, что в исходном состоянии ."a единичном выходе триггера относительности присутствует логическая 1, а на нулевом выходе - логический "0 ., Тогда в общую шину, объединяющую элементы И-НЕ 7-9 поступает серия по ТИ1. В другую шину, объединяющую элементы ИНЕ 11-13 поступает серия по ТИ2. При этом нв выходе 18 элемента И-НЕ 7 появпяе.|ся первый отрицательный импульс, в па выходе 19 триггера 34 появляется положительный импульс, который подготавливает элемент И-HE 8 к работе. Одновременно мультиплексор 1 анализирует единичный выход триггера 34 по звконууп. рввляюших сигналов нв шинах 30-32. С приходом импульса по ТИ2 на выходе 25 схемы И-HE 11 появляется второй отрицательный импульс, сдвинутый нв 180 по отношению к Отрицательному импульсу нв выходе 24, в нв выходе.20 триггера

35 появляется иоложитепьный импульс, ко» торый подготавливает элемент И-НЕ 8 к работе. Одновременно мультиплексор 1 анализирует единичный выход триггера 35 по закону управляющих сигналов на шинах

30-32. Кроме того, нулевой выход триггера 35 запрещает работу элемента И-HE

7. Аналогично работают остальные разряды регистра, причем но другому импупь« су ТИ1 появляется третий отрицательаый импульс нв выходе 26, h по другому импульсу ТИ2 появляется четвертый от° 5 а 40860 рицатепьный импульс на выходе 27. С . — Ф о р м у и а приходом третьего импульса по ТИ1 появ-" пяется пятый отрицательный импульс нв Управляемы выходе 28., с е

6 изобре тения

ТИ1 A Q Y ТИ2ЛИ

ТИ1 Л Я Ч ТИ2ЛЯ гае Я - единичный выход триггера 4 от» носитепьности, à Q - нулевой.

Применение управляемого распределитепя импульсов целесообразно в блоках с переменной структурой управления от микропроцессоров или ЭВМ.

Эффективность изобретения получается зв счет привязки первого тактового импульса к первому выходу устройства при

5 любом коэффициенте пересчета. Вцепом повышенная гибкость предлагаемого устройства позволяет сократить затраты на построение блоков с переменной структурой. по сравнению с известным, не менее

1,1 " раз. 50

5 качестве мультиплексора выбрана стйндартная микросхема 185КП1.

Единичный выход триггера 36 дешифрируется мупьтиппексором 1 и по заднему фронту ТИ перебрасывает схему установ- . ки в 0 регистра 2. Нулевой выход схемы установки в О, регистра 2 устанавливает регистр 10 в исходное состояние,, а единичный выход триггера установки в

0" регистра 2 перебрасывают триггер относительности 4. При этом на единич ном выходе триггера 4 относительности появляется логический 0", а на нулевом выходе - логическая 1 . Коммутатор 6 импульсов управления перебрасывает фазы импульсов в общих шинах регистра 10.

Цикл окончен, схема готова к повторному циклу. ,Дпя изменения числа каналов распределения необходимо изменить управпяющую команду на шинах 30- 32. При этом следует учитывать правило, что чиспо раэ У рядов регистра м аопжно быть ж= 2", где к - число разрядов управляющей команды. Коммутатор 6 импупьсов управления работает в общем спучае по закону

1О

15 яо

25 зо

3S

40 и распределитель импульсов, од ржвщий т — разрядный регистр, отпичающийся тем,что,с цепью расширения области применения устройства as счет привязки первого тактового импульса к первому выходу устройства при пюбом коэффициенте пересчета, каждый разряд регистра содержит элемент

И-НЕ и триггер, выход которого соеаинен с первым входом.эпементв И-НЕ предыдущего разряда, выход триггера каждого разряда соединен со вторым вхоаом элемента

И-НЕ поспедуюшего разряда, единичные выходы м -разрядного регистра соединены с соответствующими входами мультиплексора,выход которого соединен с единичным входом триггера усгановки в 0" м-разрядного регистра, еаиничный выход которого соеаинен со счетным входом

:триггера относительности, -а нулевой выход соединен с нулевыми установочными входами и -рвзряанрго регистра, при этом единичный .и нулевой выходы триггера относительности соединены с управляющими входами коммутатора, информационные входы которого соединены с выходами формироватепя двух серий импупьсов, при этом один выход коммутатора соединен с третьими входами элементов g-НЕ всех нечетных разрядов регистра, а другой выхоа — с третьими входами. элементов ИНЕ всех четных разрядов регистра, тактовый вход мультиплексора соединен с входом формнроввтепя двух серий импупьсов и через элемент НЕ соединен с нуле- . вым входом триггера установки в 0 разрядного регистра, а нулевой вход триггера относительности соединен с младшим разряаом управляющего входа мультиплексора.

Источники информации, принятые во вниманне при экспертизе

1. Авторское свидетельство СССР

N456269,,кп. G 06 F 1/04, 1 1. 01. 73.

2. Авторское свидетельство СССР

Мг 615470, кп. G 06 F 1/04, 23. 08. 76.

840860

Составитель В. Курочкин

Редактор Н. Лазаренко Техред Н. Келушак Корректор Г. Назарова

Заказ 4765/70 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4