Устройство для обмена информацией

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

СоюЗ Советских

Социалистических

Реснублин

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (5gP Кп 3

G 06 F 3/04 (22) Заявлено 24.0979 (21) 2819996/18-24 с присоединением заявки Йо

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 2 306,8 1.бюллетень М 2 3 (531 Pg 681.325 (088. 8) Дата опубликования описания 23D681

I «Г«« °

A.A. Бобров, П.А. Бобков, Б.Н. Веденяпин, Ю.В. Данилушкин, Е.Е. Питерцев и Ю.М. ТоргонЕн«ко

« ;..

) «1

/, 1 . 1

1," :; Й!,: (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ

Изобретение относится к вычислительной технике и может быть использовано для сопряжения оконечных устройств с процессором циФровой вычислительной машины.

Известны устройства для обмена информацией, содержащие коммутатор шин записи, коммутатор шин адреса записи, формирователи направления обмена, информационный регистр и регистр адреса, узел приоритета, два триггера, регистры требований, номера усгройства и выдачи (1).

Недостаток этих устройств — большие аппаратурные затраты.

Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения, содержащее два выходных коммутатора дан» ных, входной коммутатор данных, входные коммутаторы команд и адреса, выходные коммутаторы состояния и адреса, входной и выходной преобразо ватели, блок сравнения адресов, дешифратор команд, буферный регистр, регистры управляющего слова и слова состояния, дешифратор адреса регистров, причем первый выход дешифратора управляющих сигналов соединен с управляющим входом первого выходного коммутатора данных, второй и третий выходы — соответственно с управляющими входами выходных коммутаторов данных и адреса и коммутатора слова состояния, выходы которых подключены ко входу выходного преобразователя, а вторые входы - к первому выходу блока управления, входы входных коммутаторов адреса и дан-, ных и коммутатора команд подключены к соответствующим выходам;входного; преобразователя, а выходы — соответственно к первым входам блока сравнения адресов, первого выходного

15 коьв утатора данных и дешифратора команд (2) .

Недостаток этого устройства состоит в больших аппаратурных затратах, 20 Цель изобретения — сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство, содержащее первый входной коьинутатор, первый и второй выходные коммутаторы, группы выходов которых являются соответ,ственно первой и второй группами информационных выходов устройства, н дешифратор управляющих сигналов, 30 выходом соединенный с управляющим

840871 входом второго выходного коммутатора, введены второй входной коммутатор, блок формирования контрольного разряда, блок контроля, тактовый распределитель., шифратор управляющих сигналов, три группы линейных элементов согласования и..два линейных элемента согласования, причем группы входов первого и второго входных коммутаторов являются соответственно первой и второй группой информационных входов устройства, а группы выходов соединены соответственно через первую и вторую группу линейных элементов согласования с группами входов первого и второго выходных коммутаторов, первая и вторая группы входов блока формирования контрольного разряда соединены соответственно с группой входов второго выходного коммутатора и группой вы.-. ходов второго входного коммутатора, вход - с управляющим входом второго выходного коюеутатора и выходом дешифратора управляющих сигналов, . группа информационных входов которого через третью группу линейных элементов согласования подключена к группе выходов шифратора. управляющих сигналов, группа входов которого соединена с группой выходов тактового распределителя, вход которого является входом пуска устройства, выход блока формирования контрольного разряда соедийен через первый линейный элемент согласования с первым входом блока контроля, вторым входом подключенного к первому выходу тактового распределителя, третьим входом — к соответствующему выходу из группы выходов тактового распределителя, а первый и второй группами входов — соответственно к группе выходов первого входного коммутатора и группе входов первого выходного коммутатора, управляющие входы которых соединены с соответствующими выходами иэ группы выходов тактового распределителя, вторим выходом подключенного через второй линейный элемент согласования к управляющему входу дешифратора управляющих сигналов, выход -блока контроля является выходом контрольного разряда устройства..

Блок формирования -контрольного разряда содержит коммутатор, две группы входов и вход которого являются соответственно первой и вто.рой группами входов и входом блока, н узел свертки., вход и выход которого соединены соответственно с выходом коммутатора и выходом блока.

Блок контроля содержит коммутатор, две группы входов и вход которого являются соответственно первой и второй группами входов и третьим ,входом блока, триггер, первым вхо дом соединенный через, узел свертки

I ся сигналом с тактового распределителя 21, каждое состояние которого кодируется шифратором 9, передается через линейные элементы 3 и декодируется.дешифратором 10, стробирующим выходной коммутатор 14 н блок 16. с выходом коммутатора, а вторым ° со вторым входом блока и элемент

ЭКВИВАЛЕНТНОСТЬ первым и вторым входами подключенный соответственно к выходу триггера и первому входу блока, а выходом — к выходу блока.

Линейный элемент согласования содержит транзистор, оптронный элемент и резистор, причем вход оптронного элемента соединен через резистор с шиной положительного источника питания, управляющий выход— через транзистор с шиной отрицательного потенциала источника питания, а линейный выход - с выходом линейного элемента согласования, база

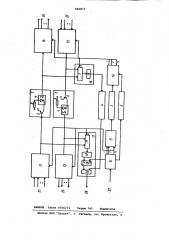

15 транзистора является входом линейного элемента согласования, На чертеже представлена блоксхема устройства.

Устройство содержит линейные элементы l, 2 и 3 согласования групп„ линейные элементы 4 и 5 согласования, включающие транзистор 6, оптронный элемент 7 и резистор 8, шифратор 9 управляющих сигналов, дешифратор 10 управляющих сигналов, входные коммутаторы ll и 12, выходные коммутаторы 13 и 14 блок 15 контроля и блок 16 формирования контрольного разряда, состоящие из коммутатора 17,.узла 18 свертки, триггера 19 и элемента 20 ЭКВИВАЛЕНТНОСТЬ, тактовый. распределитель

21, шины 22 и 23 первых групп информационных входов и выходов устройства, шины 24 и 25 вторых групп информационных входов и выходов устройства, шина 26 выхода контрольного разряда устройства и шика 27 входа пуска устройства.

Устройство работает следующим

40 образом.

Обмен осуществляется под управлением процессора, задающего на первом этапе адрес приемника или источника и направление обмена.

На втором этапе передаются данные.

На первам этапе процессор выставляет на шины 22 адрес источника или приемника и запускает по шине

27 тактовый распределитель 21, сиг © налами которого стробируется входной коммутатор 11 для выдачи через линейный элемент 1. и выходной коммутатор 14 в оконечное устройство.

При этом слово на шинах 22 передается несколькими посылками, для каж дой из которых формируются контроль.ный разряд в блоках 15 и 16, причем на шине 26 появляется сигнал, подтверждающий правильность передачи посылки. Каждая посылка сопровождает840871

Формула изобретения

1. Устройство для обмена информацией, содержащее первый входной коммутатор, первый и второй выходные коммутаторы, группы выходов которых являются соответственно первой и второй группами информационных выходов устройства, и дешифратор управляющих сигналов, выходом соединенный с управляющим входом второго выходного коммутатора, о т л и ч аю щ е е с я тем, что, с целью сок- 25 ращения аппаратурных затрат устройства, в него введены второй входной коммутатор, блок формирования контрольного разряда, блок контроля, тактовый распределитель, шифратор управляющих сигналов, три группы линейных элементов согласования и два линейных элемента согласования, причем группы входов первого и второго входных коммутаторов являются

35 соответственно первой и второй груп пой информационных входов устройства, h группы выходов соединены соответ-ственно через первую и вторую группу линейных элементов согласования с группами входов первого и второ- 40 го выходных коммутаторов, первая и вторая группы входов блока формирования контрольного разряда соеди- нены соответственно с группой входов второго выходного коммутатора и 45 группой выходов второго входного коммутатора, вход — с управляющим входом второго выходного коммутатора и выходом дешифратора управляющих сигналов, группа информационных. входов 50 которого через третью группу линейных ,элементов согласования подключена к группе выходов шифратора управл ющих сигналов,, группа входов которого соединена с группой выходов тактового распределителя, вход которого является входом пуска устройства, выход блока формйрования контрольного разряда соединен через первый линейный элемент согласования с первым входом блока контроля, вторым 60

На втором этапе передается слово данных с шин 22 на шины 24, если вызывался приемник, или с шин

25 на шины 23, если вызывался источник. Передачи несколькими посылками осуществляются аналогично передаче адреса.

Таким образом предлагаемое изобретение по сравнению с известным устройством позволяет осуществлять обмен информации при меньших аппаратурных затратах. входом подключенного .к первому выходу тактового распределителя, третьим входом — к соответствующему выходу из группы выходов тактового распределителя, а первой и второй группами входов — соответственно к группе выходов первого входного коммутатора и группе входов первого выходного коммутатора, управляющие входы которых соединены с соответ- . ствующими выходами из группы выходов тактового распределителя, вторым выходом подключенного через второй линейный элемент согласования к управляющему входу дешифратора управляющих сигналов, выход блока контроля является выходом контрольного разряда устройства.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок формирования контрольного разряда содержит коммутатор,две группы входов и вход которого являются соответственно первой и второй группами входов и входом блока, и узел свертки, вход и выход которого соединены соответственно с выходом коммутатора и выходом блока.

3. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок контроля содержит коммутатор, две группы входов и вход которого являются соответственно первой и второй группами входов и третьим входом блока, триггер, первым входом соединенный через узел свертки с выходом. коммутатора, а вторым — со вторым входом блока и элемент ЭКВИВАЛЕНТНОСТЬ, первым и вторым входами подключенный соответственнб к выходу триггера и первому входу блока, а выходом — к выходу блока.

4. Устройство по и. 1, о т л ич а ю щ е е с я тем, что линейный элемент согласования содержит транзи- стор,оптронный элемент и резистор, причем вход оптронного элемента соецинен через резистор с шиной положительного потенциала источника питания, управляющий выход - через транзистор с шиной отрицательного потенциала источника питания, а линейный выходс выходом линейного элемента согла-. сования, база транзистора является выходом линейного элемента согласования.

Источники . информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по- заявке Р 2634340/18-24, кл. G 06 F 3/04, 1978.

2. Авторское свидетельство СССР

608151 кл. G 06 F 3/04, 1976 (прототип).