Устройство для преобразования последовательныхмногорегистровых кодов b параллельные сконтролем

Иллюстрации

Показать всеРеферат

<>840877

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТВЛЬСТВУ (61) Дополнительное к авт. сеид-ву (51)М. КЛЗ (22) Заявлено 1409,79 (21) 2815908/18-24 с присоединением заявки Й

06 F 11/08

G F 5/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 23ll631. Бюллетень М 23

Дата опубликования описания 2306.81 (53) УДК (088.8) Л.В. Друзь, А.И. Савин и В.В. Солнцев ( (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛЬНЫХ

МНОГОРЕГИСFPOBbIX КОДОВ В ПАРАЛЛЕЛЬНЫЕ С КОНТРОЛЕМ

Изобретение относится к технике передачи данных и может быть"использовано в устройствах для преобразования данных.

Известно устройство для преобразования параллельных двоичных кодор, содержащее дешифратор, счетчик, ренистр, блок управления, логические элементы И. Каждая входная комбинация преобразуется в соответствующую ей только одну выходную комбинацию (1).

Однако такие устройства не обеспечивают преобразование многорегистровых кодов, так как они не анализируют и не формируют регистровые признаки, изменяющие значения преобразуемых кодов.

Наиболее близким,по технической сущности к изобретению является устройство для преобразования кодов, содержащее дешифратор, шифраторы, блоки управления и анализа. Известное устройство позволяет преобразовывать многорегистровые коды, причем каждому входному колу в зависимости от последовательности входных символов соответствует одно или несколько преобразований, включающих в себя формирование кола символа или кодов регистрового признака и символа (2).

Недостаток устройства заключается в низкой достоверйости преобразования информации, которая обусловлена тем, что в нем не обеспечивается контроль эа процессом преобразования кодов, не обнаруживаются пропу денные или дополнительно-ложные преобразования. Это снижает надежность и достоверность преобразования данных.

Цель изобретения — повышение достоверности .преобразования информации. . Поставленная цель достигается тем, что устройство, содержащее дешифратор, синхронизатор,и шифраторг причем вход дешифратора является входом устройства., выход дешифратора соеди20 нен с первым входом шифратора, выход которого является выходом устройства, введены блок контроля по модулю, реверсивный счетчик, элемент ИЛИ, блок формирования ошибки, коммутатор, регистр и блок сравнения, пфичем первый, второй, третий и четвертый выходы синхронизатора соединены соответственно с первым входом реверсив. юго счетчика, с первым, вторым и

ЗО третьим входами коммутатора, первый

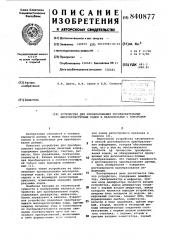

840877 выход которого соединен со вторым схемы 14 сравнения, регистра 15 усвходом шифратора и первым входом танки, счетчика 16 и дешифратора 17. блока Формирования ошибки, вход ус- Входные шины устройства соединены тройства соединен с первыми входами с первыми входами дешифратора 1, с регистра и блока сравнения, первый первыми входами блока 4 сравнения и второй выходы которого соединены 5 и через регистр 3 со вторыми входами соответственно с четвертым и пятым блока 4 сравнения. Информационные ,входами коммутатора, второй выход выходы дешифратора 1 соединены с которого соединен с третьим входом первыми входами шиФратора 2, а выход шифратора, первым входом элемента признака информации дешифратора

ИЛИ и вторым входом регистра, выход подключен через элемент ИЛИ 12 к которого соединен со вторым входом

10 третьему, суммирующему входу счетблока сравнения, выход шифратора сое- чика 11. Первый выход (совпадения) динен с входом блока контроля по мо- блока 4 сравнения соединен с первым дулю, выход которого соединен со вто- входом элемента И 7 коммутатора 6, рым входом реверсивного счетчика, вы- а второй выход (несовпадения) — с ход которого соединен со вторым вхо- 1 первыми входами элементов И 8 и 9, дом блока формирования ошибки, первый вторые входы элементов И 7, 8 и 9 выход блока формирования ошибки ян- подключены соответственно к синхрониляется вторым выходом устройства, а зирующим выходам синхронизатора 5. второй выход этого блока соединен со Выход элемента И 7 соединен со нтовторым входом дешифратора и шестым 20 рым, упранляющим,входом шифратора входом коммутатора,Tðåòèé выход кото- 2 и с управляющим входом схемы 14 рого является третьим выходом устрой- сравнения в блок 13 формирования ства,второй выход дешифратора соеди- ошибки. Выход элемента И 8 соединен нен со вторым входом элемента ИЛИ, ны- с третьим, управляющим, входом шифход которого соединен с третьим вхо- д5 ратора 2, со вторым, управляющим, дом реверсивного счетчика. входом регистра 3 и через элемент

При этом блок формирования ошибки ИЛИ 12 связан с третьим, счетным, содержит схему сравнения, регистр входом счетчика 11. Выход элемента уставки, счетчик и дешифратор, причем И 9 подключен к внешней цепи запропервый и второй входы схемы сравне- З0 са информации. Выходы шифратора 2 ния являются соответственно перным являются выходами устройства и поди вторым входами блока, выход ре- ключены через блок контроля по могистра уставки соединен с третьим дулю 10 ко второму, вычитающему, входом схемы сравнения, выход кото- входу счетчика 11, выходы которого рой соединен с входом счетчика, вы- соединены с первыми входами схемы 14 ходы счетчика соединены с входами сравнения в блоке 13 формирования дешифратора, первый и второй выходы ошибки, а первый, установочный, вход которого являются первым и вторым счетчика 11 подключен к синхронизируювыходами блока. щему выходу синхронизатора 5. В блоКроме того, коммутатор содержит ке 13 формирования ошибки регистр первый, второй и третий элементы И, 40 15 уставок соединен со вторыми вхавыходы которых являются соответ- дами схемы 14 сравнения, выход коственно первь м, вторым и третьим торого связан со счетным входом счетвыходами коммутатора, первый, второй чика 16, подключенного к дешифратору и третий входы коммутатора соединены 17. Один из выходов дешифратора 17 соответственно с первыми входами 4 является цепью сигнала ошибки, а первого, второго и третьего элемен- другой выход подключен к третьему, тов И, второй вход первого элемента блокирующему, входу элемента И 9

И соединен с четвертым входом ком- коммутатора 6 и к управляющему входу мутатора, вторые входы второго и дешифратора 1. третьего элементов И соединены с 50 пятым входом коммутатора, шестой вход Синхронизатор 5 представляет сокоторого соединен с третьим входом бой генератор импульсов, который фортретьего элемента И. мирует серии импульсов, сдвинутых во

На чертеже изображено устройство времени относительно друг друга. Редля преобразования последовательных гистр 15 уставок предстанляет собой многорегистровых кодов в параллель- коммутационное устройство, обеспеные с контролем. чивающее выдачу кодовых сигналов

Устройство содержит дешифратор 1 постоянного уровня на входы схемы входных кодовых комбинаций, шифратор 14 сравнения, например подключение

2 буквенных и цифровых комбинаций, вторых входов схемы 14 сравнения к регистр 3, блок 4 сравнения,синхрони- dO нулевой шине питания . затор 5, коммутатор 6, состоящий из При преобразовании, например, трех элементов И 7, 8 и 9, блок 10 алфавитно-цифрового кода ГОСТ 13052контроля по модулю, реверсивный 74 в трехрегистровый международный счетчик 11, элемент ИЛИ 12, блок 13 телеграфный код MTK-2 устройство раформирования ошибки, состоящий из ботает следующим образом.

840877

В исходном положении синхронизатор 5 выдает на установочные входы счетчика 11 код числа, зафиксированного в регистре уставок 15 (например код числа 0 ), и устанавливает счетчик в соответствующее положение, а затем выдает импульс на вход элемента И 9. Так как сигналы на входах блока 4 сравнения отсутствуют, последний сигналом несовпадения открывает элемент И 9, который посылает импульс (О запроса информации во внешнюю цепь.

По этому сигналу на входные кодовые шины устройства поступают кодовые комбинации ГОСТ 13052-74, которые соответствуют русским, цифровым, латинским или служебным символам и характеризуются постоянными значениями шестого и седьмого разрядов кода.

Значения этих разрядов используются в качестве регистровых признаков входных символов. Дешифратор 1 ана- 20 лизирует первые пять разрядов кодовой комбинации, определяющих символ, вырабатывает сигналы управления шифратором 2 и выдает сигнал наличия информации через элемент ИЛИ 12 на суммирующий вход счетчика 11, при этом содержимое счетчика увеличивается на единицу. Одновременно значения шестого и седьмого разрядов входного кода поступают на первые входы блока. 4 сравнения и на входы регистра 3, однако в регистр 3 не заносятся ввиду отсутствия сигнала разрешения на управляющем входе этого регистра. Так как на обоих входах блока 4 сравнения сигналы не совпадают, последний сигналом несовпадения подготавливает элемент И 8 к открыванию. Синхронизатор 5 следующим импульсом открывает элемент

И 8, который выдает сигнал pe- 40 гистр на управляющие входы шифратора 2 и регистра 3, а также через элемент ИЛИ 12 на суммирующий вход счетчика 11. При этом содержимое счетчика 11 Увеличивается ergq 45 на единицу, значения шестого и седьмого разрядов входного кода заносятся в регистр 3, откуда поступают на вторые входы блока 4 сравнения, а шифратор 2 при наличии сигналов с выхода дешифратора 1 и управляющего сигнала . Регистр с выхода элемента И.8 формирует комбинацию регистра в MTK2 (русский, латинский или цифра), которая поступает на вход устройства и на вход блока 10 контроля по модулю. Блок 10 контроля по модулю прове-. ряет комбИнацию по четности и при правильной четности выдает сигнал, поступающий на вычитающий вход счетчика 11, содержимое которого умень- 40 шается на единицу. После формирования и выдачи кода регистра на обоих входах блока 4 сравнения совпадают значения шестого и седьмого разрядов входной комбинации, и последний формирует сигнал совпадения, которйй подготавливает элемент И 7 к открыванию. Следующим импульсом синхронизатор 5 открывает элемент И 7, который выдает сигнал Символ на управляющие входы шифратора .2 и схемы

14 сравнения. Шифратор 2 при наличии сигналов с выхода дешифратора 1 и управляющего сигнала Символ с выхода элемента И 7 формирует комбинацию символа в коде МТК-2, соответствующего входному символу в коде

ГОСТ 13052-74, которая также поступает на вход устройства и через блок 10 контроля по модулю (при правильной четности) уменьшает содержимое счетчика еще на единицу. Таким образом, для данного символа в коде ГОСТ устройство формирует две кодовые комбинации — регистр и символ — в коде MTK-2, при этом к концу преобразования содержимое счетчика

11 соответствует начальной уставке.

В блоке 13 формирования ошибки по сигналу на управляющем входе схемы

14 сравнения последняя сравнивает состояние счетчика 11 с содержимым регистра 15 уставки. В случае совпадения их состояний схема 14 сравнения не выдает сигналов на вход, в случае несовпадения — выдает импульс на вход счетчика 16. При этом на выходе дешифратора 17 формируется сигнал Повтор, который блокирует элемент И 9 и тем самым цепь запроса информации, и подается на управляющий вход дешифратора 1 для повторного преобразования входной комбинации, и процесс повторяется. В случае заданной кратности повторения ошибки, определяемой счетчиком 16, дешифратор 17 выдает сигнал ошибки во внешнюю цепь.

По окончании преобразования данной входной комбинации, т.е. после выдачи кода символа в MTK-2, на входных шинах устройства входная комбинация сбрасывается, блок сравнения переходит в состояние Несовпадение, и устройство выдает во внешнюю цепь следующий сигнал запроса информации.

Последующая входная комбинация в коде

ГОСТ может иметь регистровый признак либо совпадающий с регистровым признаком предыдущего символа и зафиксированного в регистр 3,либо не совпадающий с ним. В Случае, если признаки регистров не совпадают, устройство работает аналогично, при этом содержимое счетчика 11 сначала увеличивается на два, а затем уменьшается на два, так как входному символу соответствуют два преобразования: формирование регистра и символа в MTK-2. В случае, если признаки регистров совпадают блок 4 сравнения сразу переходит в режим Совпадение и коммутатор 6 с выхода элемента И 7 выдает один управляющий сиг840877 нал Символ . По этому сигналу для входной комбинации формируется только код символа в МТК-2. При этом содержимое счетчика 11 сначала увеличивается на единицу, а затем уменьшается на еДИНицу. 5

Таким образом, при правильной работе устройства содержимое счетчика

ll всегда равно числу начальной уставки. При неисправностях каких-либо элементов устройства, неправильной четности преобразованных кодов, в случаях, если число преобразований не соответствует входной комбинации, содержимое счетчика 11 отличается от начальной уставки в большую или меньшую сторону, и блок 13 формирования ошибки выдает сигнал ошибки во внешнюю цепь, В предлагаемом устройстве обеспечивается автоматическое обнаружение отказов элементов устройства, что 20 повышает достоверность преобразования в нем информации.

Формула изобретения

1. Устройство для преобразования последовательных многорегистровых кодов в параллельные с контролем, содержащее дешифратор, синхронизатор и шифратор, причем вход дешифратора является входом устройства, выход дешифратора соединен с первым входом шифратора, выход которого является вы-. ходом устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения достоверности работы, в устройство введены блок контроля по модулю, реверсивный счетчик, элемент ИЛИ, блок формирования ошибки, коммутатор, регистр и блок сравнения, причем первый, второй, третий и четвертый выходы синхронизатора соединены соответствен"> но с первым входом. реверсивного счетчика, с первым, вторым и третьим входами коммутатора первый выход 45 которого соединен со вторым входом шифратора и первым входом блока формирования ошибки, вход устройства соединен с первыми входами регистра и блока сравнения, первый и второй 50 выходы которого соединены соответственно с четвертым и пятым входами коммутатора, второй выход которого соединен с третьим входом шифратора, пс вым входом элемента ИЛИ и вторым входом регистра, выход которого соединен со вторым входом блока сравнения,. выход шифратора соединен с входом блока контроля по модулю, выход которого соединен со вторым входом реверсивного счетчика, выход которого соединен со вторым входом блока формирования ошибки, первый выход блока формирования ошибки является вторым выходом устройства, второй выход блока формирования ошибки соединен со вторым входом дешифратора и шестым входом коммутатора, третий выход которого является третьим выходом устройства, второй выход дешифратора соединен со вторым входом элемента ИЛИ, выход которого соединен с третьим входом реверсивного счетчика.

2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок формирования ошибки содержит схему сравнения, регистр уставки, счетчик и дешифратор, причем первый и второй входы схемы сравнения являются соответственно первым и вторым входамиблока, выход регистра уставки соединен с третьим входом схемы сравнения, выхбд которой соединен с входом счетчика, выходы счетчика соединены с входами дешифратора, первый и второй выходы которого являются первым и вторым выходами блока.

3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что коммутатор содержит первый, второй и третий элементы И, выходы которых являются соответственно первым, вторым и третьим выходами коммутатора, первый, второй и третий входы коммутатора соединены соответственно с первыми входами первого, второго и третьего элементов И; второй вход первого элемента И соединен с четвертым входом коммутатора, вторые входы второго и третьего элементов И соединены с пятым входом коммутатора, шестой вход которого соединен с третьим входом третьего элемента И.

ИСточники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 541163, кл. G F 5/02, 1976.

2. Авторское свидетельство СССР

М 480075, кл. G 06 F 5/00, 1975 (прототип).

840877

Составитель И. Сигалов

Техред Н.Бабурка Корректор В. Бутяг, Редактор Н. Лазаренко

Тирам 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Чосква, Ж-35, Раушская наб., д. 4/5

Заказ 4766/71. филиал ППП Патент, г. Уигород, ул. Проектная, 4