Преобразователь двоично-десятичного кода"12222" b последовательный код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ ф

/ г

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 280879 (21) 2814335/18-24 (5)) рА с присоединением заявки Но ,(23) П ио итет

G 06 F 5/02

Государственный комитет

СССР по делам изобретений и открытий р р

Опубликовано 2306.81.Бюллетень М 23 (53)УДК 681 325 (088. 8) Дата опубликования описания 2306.81 ( ( (72) Автор изобретения

A.È. Журавлев.) ."

Рязанский завод счетно-аналитических машин (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА 12222 В ПОСЛЕДОВАТЕЛЬНЫЙ КОД

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах для преобразования информации.

Известен преобразователь параллельного двоично-десятичного кода в унитарный код, содержащий регистр, хранения кода, элемент И, элемент

ИЛИ и элементы задержки (1).

Недостаток этого преобразователя состоит в том, что применение фиксированных элементов задержки пои равномерном распределении импульсов в пачке выходного кода не позволяет произвольно изменять частоту следования импульсов опроса.

Наиболее близким к предлагаемому изобретению по технической сущности является преобразователь двоичнодесятичного кода 12222 в последовательный код, содержащий входной регистр, группу элементов ИЛИ, группу элементов И, первые входы которых соединены с тактовым входом преобразователя, вторые входы соединены с прямыми выходами соответствующих

-элементов ИЛИ группы, первый и второй элементы ИЛИ, причем выходы элементов И группы соединены с первыми входами соответствующих элементов ИЛИ группы и соответствующими входами второго элемента ИЛИ, первый вход первого элемента ИЛИ соединен с выходом первого элемента

И группы, а выход первого элемента

ИЛИ является информационным выходом преобразователя, инверсный выход

i"го элемента ИЛИ группы (1=1-;(n-1)), где п число разрядов преобразуемого кода соединен с третьим входом (i+1)-oro элемента. И группы, единичные выходы разрядов регистра соединены со вторыми входами соответствующих элементов ИЛИ группы (2).

Недостаток известного преобразователя состоит в сложности схемного решения, заключающегося в необходимости введения дополнительной группы элементов И и управляющего триггера.

Кроме того, существенным недостатком является необходимость жесткой фиксации разрядов кода 2222 при заполнении регистра, в зависимости от значения кода. Например, для кода, соответствующего десятичному числу

4, необходимо распределить информацию в виде 01100, где крайний левый разряд соответствует весу 1, т.е. заполнение регистра ведется

ЗО фиксированно, слева — направо. В то

840878

Формула изобретения

d0

65 же время во многих случаях записывается код в виде 00011.

Такое ограничение отсутствует в предлагаемой схеме.

Цель изобретения — упрощение устройства и расширение его функциональных воэможностей, заключающихся в обеспечении воэможности регулиро1 вания частоты опроса.

Поставленная цель достигается тем, что в преобразователь двоичнодесятичного кода 12222 в последовательный код, содержащий входной регистр, группу элементов ИЛИ, груп- пу элементов И, первые входы которых соединены с тактовым входом преобразователя, вторые входы соединены с прямыми выходами соответствующих элементов ИЛИ группы, первый и второй элементы ИЛИ, причем выходы элементов И группы соединены с первыми входами соответствующих элементов

ИЛИ группы и соответствующими входами второго элемента ИЛИ,.первый вход первого элемента ИЛИ соединен с выходом первого элемента И группы, а выход первого элемента ИЛИ является информационным выходом преобразователя, инверсный выход i-ro элемента

ИЛИ группы (i=1 †: (n-1)), где п — чис" ло разрядов преобразуемого кода сое,динен с третьим входом (i+1) -oro элемента И группы, единичные выходы разрядов регистра соединены со вторыми входами соответствующих элемен тов ИЛИ группы, включен элемент И, прямой вход которого соединен с единичным выходом триггера первого разряда регистра, инверсный вход соединен с выходом второго элемента ИЛИ, входом установки единицы триггера первого разряда регистра.и вторым входом первого элемента ИЛИ, прямой выход 1-го элемента ИЛИ группы соединен с третьим входом (i+1) -ого элемента ИЛИ группы, выходы элементов

И группы соединены с входами установ» ки нуля соответствующих разрядов регистра, прямой выход и-ого элемейта

ИЛИ группы является выходом окончания преобразования.

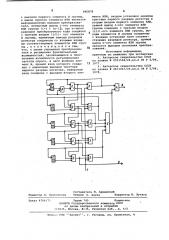

На чертеже представлена блоксхема преобразователя. .Пробразователь содержит входной регистр 1, состоящий из триггеров, группу элементов ИЛИ 2, группу элементов И 3, первый и второй элементы

ИЛИ 4 И 5, дополнительный элемент

H б, вход 7 опроса преобразователя, информационный выхбд 8 преобразователя и сигнальный выход 9 преобразователя.

Преобразователь работает следующим образом.

Если в левый значащий триггер с весом 2 входного регистра 1 зацисана 1, то при поступлении

1 ервого импульса опроса по входу 7 а второй вход элемента И группы соответствующего разряда, на выходе элемента ИЛИ 4 формируется одиночный импульс., который поступает на информационный выход 8. При этом импульс с выхода соответствующего эле5 мента И группы 3 обнуляет опрашива емый триггер регистра с весом 2, а импульс с выхода элемента ИЛИ 5 устанавливает в 1 триггер 1/» весом 1, входного регистра и пост,пает на инверсный вход элемента И 6, предотвращая ложное срабатывание элемента И 3 группы разряда с весом 1 . После окончания импульса опроса все элементы И 3 группы разрядов с весом 2 по третьему входу закрыты запрещающим потенциалом. При поступлении второго импульса опроса последний пройдет через элемент И 3 группы разряда с весом 1 и через элемент ИЛИ 4 на информационный вы20 ход 8. При этом триггер с весом 1 обнуляется.

Таким образом, каждому значащему разряду регистра с весом 2 соответствуют два импульса на выходе ин25 формационной шины 8.

Далее аналогично происходит опрос следующего элемента И 3, соответствующего ближайшему справа значащему разряду с весом 2 .

Выходной код выдается в виде пачки импульсов, равномерно распределенных во времени.

После опроса последнего элемента

И 3 группы входной регистр принимает

35 нулевые значения во всех Разрядах, и на выходе правого крайнего элемента

ИЛИ группы 2 формируется сигнал "Конец преобразования, который поступает непосредственно на сигнальный выход 9 преобразователя.

40 Таким образом, структура устройства позволяет при небольшом количестве оборудования получить на выходе последовательный код в виде пачки импульсов, равномерно распределенных

45 во времени при любом распределении информации в значащих разрядах с весом 2 входного регистра.

Преобразователь двоично-десятичного кода 12222 в последовательный. код, содержащий входной регистр, группу элементов ИЛИ, группу элементов И, первые входы которых соединены с тактовым входом преобразователя, вторые входы соединены с прямыми выходами соответствующих элементов ИЛИ группы, первый и второй элементы ИЛИ, причем выходы элементов И группы соединены с первыми входами соответствующих элементов ИЛИ группы и соответствующими входами. второГо элемента ИЛИ, первый вход первого элемента ИЛИ соединен

840878

Составитель М. Аршавский

Техред 3. фанта Корректор В. Бутяга

Редактор Н. Пушненкова

Заказ 4766/71

Тираж 745 Подписное

ВНИИПИ Государственного, комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ппп Патент, г. Ужгород, ул. Проектная, 4 с выходом первого элемента И группы, а выход первого элемента ИЛИ является информационным выходом преобразователя, инверсный выход i-ого элемента

ИЛИ группы (1=1 †. (п-1)), где п-число разрядов преобразуемого кофа соединен с третьим входом (i-;1) — ого элемента

И группы, единичные выходы разрядов регистра соединены со вторыми входами соответствующих элементов ИЛИ группы, отличающийся тем, что, с целью упрощения преобразователя и расширения функциональных возможностей, заключающихся в обеспечении возможности регулирования частоты опроса, в него включен элеМент И, прямой вход которого соединен с единичным выходом триггера первого разряда регистра, инверсный вход соединен с выходом второго элемента ИЛИ, входом установки единицы триггера первого разряда регистра и вторым входом первого элемента ИЛИ, прямой выход i-ого элемента ИЛИ группы соединен с третьим входом (i-; 1) -ого элемента ИЛИ группы, выходы элементов И группы соединены с входами установки нуля соответствующих разрядов регистра, прямой выход и-ого элемента ИЛИ группы является выходом окончания преобразования.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке 9 2551548/24,кл.G 06 F 5/04, 1977.

2. Авторское свидетельство СССР по заявке У 2671067/24,кл.G 06 F 5/04, 1978.