Преобразователь прямого кода в дополни-тельный

Иллюстрации

Показать всеРеферат

ОПHGAHHt

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-еу (22) Заявлено 250178 (21) 2572994/18-24

Союз Советсннк

Соцналнстнческнк

Феслублнк

«ii 840879 (5!)М. Кл.з

G 06 F 5/04

Н 03 К 19/08 с присоединением заявки Йо

Государственный комнтет

СССР но яелам нзобретеннй и открытнй (23) Приоритет

ОпубЛиковано 2306.81. Бюллетень Но 23 (53) УДК 681.325.5 (088. 8) Дата опубликования описания 2306,81 (72) Авторы иэобретени я

Г-.А. Подольский, Л.Б. Родин и A.È. Со ййн-=C

Ф t ы

1 (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПРЯМОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ

Изобретение относится к вычислительной технике, служит для преобразования прямого кода в дополнительный н может быть использовано в арифметических устройствах и других устройствах обработки цифровой информации.

Известны преобразователи прямого кода в дополнительный, построенные на триггерных регистрах tll.

Однако известные преобразователи обладают недостаточной надежностью работы.

Наиболее близким к предлагаемому является преобразователь прямого кода в дополнительный, построенный на логических элементах и сумматоре (2) .

Однако схема такого преобразователя достаточно сложна.

Цель изобретения — упрощение устройства.

Цель достигается тем, что в преобразователе прямого кода в дополнительный, содержащем при преобразовании (и+1)- разрядного кода и элементов И-НЕ и и-разрядный сумматор, шина каждого 1-го разряда входного кода (2414n) соединена со входом (1-1)-го элемента H-HE и со входом

i-го разряда сумматора, с другим, входом которого соединен выход i-ro элемента И-НЕ, вход n-ro элемента

И-HE подключен к шине управляющей константы, выход первого элемента

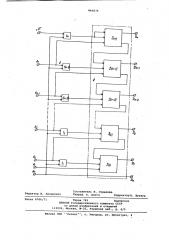

И-НЕ и шина первого разряда входного кода подключены ко входам первого разряда сумматора, шина знака входного кода подключена ко входам всех элементов И-НЕ. . На чертеже представлена функциональная блок-схема преобразователя прямого кода в дополнительный. устройство содержит и элементов

1-1 -: 1-и И-НЕ и и-разрядный сумматор 2 (2-1 †. 2-n). Первая шина знака

АЕ входного кода А.(-A > соединена со входами всех элементов 1-1 †. 1-п ИНЕ. Вторая шина первого разряда А4 входного кода подключена ко входу первого разряда сумматора 2-1, 1-ая .шина каждого последующего разряда входного кода А;(2CiW) подключена ко входу (i-11-ro элемента И-HE u ко входу i-го разряда сумматора 2.

Один вход n-ro элемента И-НЕ подключен к (п+1)-ой шине управляющей константы 0, а выход и-го элемента

И-НЕ подключен дополнительно ко входу переноса и-го разряда сумматора.

840879

Преобразователь работает следующим образом.

ВМОднОЙ разрядный код А=А А .,A в прямом коде поступает на первые входы соответствующих разрядов сумматора 2 и со сдвигом влево на один разрядниа первые входы элементов б

И-HE. Пди.поступлении положительного числа ецио знаковый разряд !А ="О) блокирует элементы И-НЕ, что при подключении выхода n-ro элемента И"НЕ ко входу переноса и-го разряда сумма-. fO тора эквивалентно подаче на вторые входы всех разрядов сумматра 2 сигналов 0, при этом иа выходах сумматора выдается входной разрядный код без преобразования„ т.е. D=A. (5

При поступлении отрицательного числа знаковый разряд его кода (Ao=1) разрешает работу всем элементам И-НЕ, и на входы сумматора поступают входное число в прямом коде и удвоенное (эа счет сдвига влево на один разряд) число в инверсном коде с выходов эле- ментов И-НЕ, причем с выхода младшего (n-го) элемента И-НЕ сигнал 1 подается на второй вход и на вход переноса младшего (n-го) разряда сумматора 2. Сумматор 2 в этом случае выдает выходное число в дополнительном коде, так как

D A-.2A =-A.

При необходимости преобразования ЗО информации, представленной в обратном коде, на вход и-го элемента И-НЕ постоянно подается сигнал 1 (вме-, сто сигнала 0 ).

Предлагаемая схема преобразователя проста и позволяет уменьшить объем оборудования и 1 отребляемую им мощность.

Эориула изобретения

Преобразоватеяь прямого кода в дополнительный,-содержащий при преобразовании (n+1)-разрядного кода и элементов И-НЕ и и-разрядный сумматор, о T:ë и ч а ю .шийся тем, что, с целью упрощения устройства, шина:каждого 1-ro разряда входного кода (2414йь) соединена со входом (i-:1)-го элеМента И-НЕ и со входом

i-ro разряда сумматора, с другим входом которого соединен вход i-ro элемента И-НЕ, вход n-ro элемента

И-НЕ подключен к шине управляющей константы, выход первого элемента

И-НЕ и шина первого разряда входного кода подключены ко входам первого разряда сумматора, шина знака входного кода подключена ко входам всех элементов И-НЕ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 259472, кл. G 06 F 5/02.

2. Папернов A.A. ЛОгические основы цифровой вычислительной техники. М., "Советское радио", 1972, с. 1бЗ, рис. 18 (прототип).

840879

Составитель И. Горелова

Техред 3 . Фанта Корректор В. Вутяга

Редактор В. Лазаренко

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4766/71

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4