Устройство для вычисления экспоненциальныхфункций

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВТИЛЬСТВУ

Союз Советских

Социалистических

Республик

< 440893 (61) Дополнительное к авт. сеид-ву— (22).Заявлено 06.0178 (21} 2568044/18-24

Р1 М g> 3

G 06 E 7/544 с присоединением заявки ¹

Государственный комитет

СССР но делам изобретений и открытий (23} Приоритет

Опубликовано 230681. Бюллетень Н9 23 . (53) УДК 681. 325 (088.P) Дата опубликования описания 230681 (54 ), УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭКСПОНЕНЦИАЛЬНЫХ

ФУНКЦИЙ г,(с) - ф - (2) а(М у

Ift — Я

b(a)

dt сф) Прнчам а(О) аа, Ь(о) Изобретение относится к вычислительной технике.

Известно устройство для вычисления экспоненциальных функций, содерmagee два счетчика, группу элементов

И, элемент ИЛИ (1).

Однако известное устройство имеет ограниченные функциональные возможности.

Наиболее близким по технической, сущности к предлагаемому является уст. ройство для вылисления экспоненциальных функций, содержащее два делителя частоты, каждый из которых содержит счетчик, блок сравнения, управляющий 15 счетчик-регистр, причем счетные вхо.ды делителя частоты являются входом импульсной последовательности устройства, частотный вьнюд каждого де-лителя соединен с входом управляюще- 20

ro счетчика-регистра другого делителя, причем один иэ управляющих счетчиковрегистров работает на сложении, а второй - на вычитании (2

В исходном состоянии в вычитающем счетчике первого двоичного делителя частоты находится код числа а(о) ал, а в суммирующем счетчике второго дво ичного делителя частоты находится код числа b(o) Ьв . На входы двоич- 30 ных делителей частоты поступает одна и та же частота f0 . Частота т„, на выходе первого двоичного делителя частоты определяется выражением

f (t) а частота на выходе второго двоичноzo делителя частоты определяется выражением где а(t) Ь(t) - числа, соответствующие коду в управляющем счетчике первого и второго двоичных делителей соответственно. Поскольку частота f<(t) поступает на суммирующий вход управляющего счетчика второго . двоичного .делителя частоты, а частота f<(t) .на вычнтающий вход управляющего счетчика первого двоичного делителя част тоты, то известная схема описывается следующей системой управления

840893

Преобразбвав (3), получаем а() (+) = о () 4t)(t) (w)

ae = о (), Ь(() = 0 (9) откуда следует, что 0

6 (с4ь) й1 или с(® 4(t) = о" = с о" о (Б) 10

Определив из (б) Ь(е) и подста- 15 вив в (4), получаем

Вп (+) аорто — — =-Уo () с) с4(t)

Решив (7) методом разделения переменных, получаем

Ц= с(о (е)

<4 оЬо

Поступив аналогично со вторым уравнением системы (4), получаем, (,) ц Хо (3)

4obo

Таким образом, при поступлении на вход устройства тактовой частоты за время t = t, т.е. при поступлении N импульсов частоты fz I N> = 30 д t>l, в управляющих счетчиках двоичных делителей частоты формируются, в соответствии с (8) и (9), коды чисел

3S

МА й;( (10) = х

Однако известное устройство обладает черезмерной сложностью и недостаточной точностью, обусловленной большой погрешностью округления из-за применения двоичного делителя часто45 ты с постоянной времени системы, 1 равной, как следует из (8) и (9), л !! о цель изобретения †. упрощение устройства и повышение его точности.

Поставленная цель достигается тем, что устройство, содержащее сумм )рующий и вычитающий счетчики, перв ®о и вторую группы элементов Й, при этом входы управления первой группы элементов И соединены соответственно с выходами первой группы вычитающего счетчика, а входы управления второй группы элементов И вЂ” с-.выхо- @) дами первой группы суммирующего счетчика, дополнительно содержит два операционных блока и два элемента ИЛИ, причем первые входы операционных блоков, соединены со входом импульс- у5

Сложив уравнения в системе (4), получаем ной последовательности устройства, вторые входы первого и второго операционных блоков ""îåäèíåíû с выходами соответственно первого и второго элементов ИЛИ, выход первого операционного блока соединен со счетным входом суммирующего счетчика, а выход второго — со счетным входом вычитающего счетчика, вторая группа выходов суммирующего счетчика соединена с.информационными входами первой группы элементов И, вторая группа выходов вычитающего счетчика с информационными входами второй группы элементов И, выходы первой и второй групп элементов И соединены соответственно с входами первого и второго элементов ИЛИ.

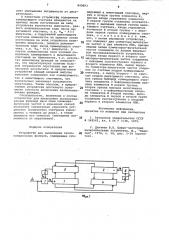

На фиг. 1 схематично изображено предлагаемое устройство;. на фиг. 2 операционный блок.

Устройствб содержит суммирующий счетчик .1, вычитающий счетчик 2, группы элементов И 3 и 4, элементы ИЛИ

5 и б, операционные блоки 7 и 8.

Каждый операционный блок содержит триггер 9, элемент И 10, элемент

ИЛИ 11, элемент задержки 12. При этом первый вход элемента ИЛИ является пер-. вым входом операционного блока, второй вход элемента ИЛИ соединен с выходом элемента задержки, а выход элемента ИЛИ соединен с первыми входами элемента И и триггера и является выходом операционного блока, второй вход триггера является вторым входом операционного блока, выход триггера соедйнен со вторым входом элемента И, выход которого соединен с выходом элемента задержки.

Устройство работает следующим образом.

В исходном состоянии в вычитающем счетчике 2 находится код числа.

A l tg-- О = а, а в суммирующем счетчике 1 находится код числа i3 t = ot=

bî На первые входы операционных блоков 7 и 8 поступает тактовая частота ГО, С выхода блока 7 частота поступает на вход суммирующего счетчика 1. Счетчик 1 с группой 3 схем совпадения предстаВляет собой двоичный умножитель частоты, управляемый кодом числа A (t) вычитающего счетчика 2, поэтому частота f на выходе элемента ИЛИ 5 определяется выражением 5 ® — 1 (12)

Ь N,ù где й, = 2 — коэффициент пересчета счетчиков 1 и 2;

n — количество двоичных разрядов счетчиков 1 и 2;

A (t) — код числа вычитающего счетчика 2.

Вычитающий счетчик 2 с группой 4 схем совпадения представляет собой

Сложив уравнения в системе (24), получаем

d8(t} dA(t) щ ). + g(t) — =p

@t dt откуда следует, что

d (A„S)

5 д+ или A(t) ° B(t) Const ap bp, где а = A(t))k=p ) bp = В (t)l =g

О

Определив из (25) В (t) и подставив

10 в первое уравнение системы уравнений (24), получаем

840893 < — 1 (15) Б A(t} й1

15 или А()

А(Ц < О Во

Проинтегрировав (27), получаем

20 . п А(1)= — 0 m + ( цp p,откуда у ЕО. тп

A(t} где С вЂ” постоянная. интегрирования.

25 При с О, А(t.) а, поэтому

C- Впаои

Ъ епА(}- — +е ао

Rp )(m+

f kb ™, (19}

0 откуда р Ищ

A()=a,g " откуда

%р Nm у = . (9)

Так как частота f< поступает на вход вычитающего счетчика 2, а частота à — на вход суммирующего счет- чика 1, то числа А (t) и В (t), соответствующие кодам вычитающего счетчика 2 и суммирующего счетчика 1, соответственно равны

A(t) = Н„, - g К dt (9a) о

В (t) = f> dt, (ХМ о где t — текущее время.

Для определения А(t) и В(t) необходимо решить уравнения (20) и .(21).

Продифференцировав (20) и (21), .получаем следующую систему уравнений

d A(t) д 6 а ь(} 3 (2а)

dt

Подставив (1б) и (19) в (22), получаем

55 А() а,,. (.13)

85(t) Rp Nw

A(t) или

65 двоичный умножитель частоты, управляемый кодом числа В (t) суммирующего счетчика 1. Поэтому частота на выходе элемента ИЛИ б определяется вЫражением

4 и

Ю где f — частота на выходе блока 8.

Так как частота Гз поступает на

° второй вход блока 7, то в соответствии с фиг. 2,.частота f6- на ее выходе определяется выражением

%5= 0+ 5-% (14) или, с учетом (12 }

Аналогичным образом, так как частота f< поступает на второй вход блока 8, то, в соответствии с фиг.2, частота 6 на ее выходе определяется выражением у = +у - (л)

6 О 6 4 или, C учетом (13), dА (t)

ЬЖ. =- pN (24) .б

ЬЬ-) д = 1о (м дВ() Решив аналогичным методом второе уравнение системы (24) уравнений, получаем

В()=Ь,Е " (Зо) Таким образом, в течение времени

t = t>, при поступлении на вход устройства й„ импульсов частоты fy l N =

t }, в соответствии с (29) и (30), в вычитающем счетчике ? и суммирующем счетчике 1 формируются соответственно коды чисел

« xNщ

- A(t)Q=+ аОЕ

М йш („) Как следует из (29) и. (30) постоянная времени ь системы в предлагаемом устройстве для вычисления экспонейциальных функций равна

Сравнивая выражения (11);и (12) видим, что в предлагаемом устройстве для вычисления экспоненциальных функций постоянная времени t системы уменьшена, что позволяет повысить точность высисления функций (31) за

840893

Формула изобретения счет уменьшения погрешности от дискретизации.

В известном устройства содержимое суммирующего счетчика изменяется на едийицу после поступления "на вход устройства количества импульсов, равного дополнительному коду числа вычитающего счетчика, .т.е. N> А(t) импульсов, а содержимое вычитающего счетчика изменяется на единицу после поступления на вход устройства количества импульсов, равного дополнительному коду числа суммирующего счетчика, т.е. N - В(t) импульсов. В случае невыполнения этих условий содержимое суммирующего и вычитающего счетчиков не изменяется, т.е. резуль- тат вычисления функций не изменяется, что характеризует наличие большой погрешности округления при вычислении результата. В предлагаемом устройстве каждый входной импульс Щ изменяет содержимое как суммирующего, так и вычитающего счетчиков, что значительно уменьшает погрешность округления. Таким образом, в предлагаемом устройстве достигнуто повы- 5 шение точности вычисления .экспоненциальных функций.

Следовательно, включение в состав устройства для вычисления экспоненци- альных функций двух схем сложениявычитання частот и изменениЕ связей позволяет значительно упростить устройство (количество счетчиков уменьшилось с четырех до двух), а также повысить его точность (уменьшена погрешность от округления).

Устройство для вычисления экспо- 40 ненциальных функций, содержащее суммирующий и вычитающий счетчики, первую и вторую группы элементов Й, причем входы управления элементов

И первой группы соединены соответственно с,выходами первой группы вычитающего счетчика, входы управления элементов И второй группы - с выходами первой группы суммирующего счетчика, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит два сумматора-вычитателя частот и два элемента ИЛИ, причем . первые входы сумматоров-вычитателей частот соединены со входом импульсной последовательности устройства, вторые входы первого и второго сумматоров-вычитателей частот соединены с выходами соответственно первого и второго элементов ИЛИ, выход .первого,сумматора-вычитателя частот соединен со счетным входом суммирующего счетчика, а выход второго — со счетным входом вычитающего счетчика, вторая группа выходов суммирующего счето чика соединена с информационными входами элементов И первой группы, вторая группа выходов вычитающего счетчика - c-информационными входами элементов И второй группы, выходы элементов И первой и второй групп соединены соответственно с входами первого и второго элементов ИЛИ.. Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 369565, кл. G 06 F 7/38, 1970.

2. Данчеев В.П. Цифро-частотные вычислйтельные устройства. M., "Энергия", 1976, с. 58, рис. 2-19 (прототип).

840893

ЖааР

Составитель Г. Плешев

Техред Н.Ковалева Корректор В. Бутяга

Редактор Г. Волкова

Заказ 4767/72 Тираж 745

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное " Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4