Время-импульсный функциональный преобра-зователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

< >840898

К АВТОРСКОМУ СВИДИадЬСТВУ (61) Дополнительное к авт. саид-ву— (22) Заявлено 280579 (2)) 2773164/18-24 (53)М. Кл.з

G F 7/60 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений и открыти и (23) Приоритет

Опубликовано 230681. Бюллетень ¹ 23

Дата опубликования описания 230681 (53) УДК 681. 325 (088.8) (72) Авторы изобретения

А.А. Астафьев, С.Г. Быценко, Н.И. Иопа, В.Н. Лсктюхин и В.A. Шаров

Рязанский радиотехнический институт и Рязаиский. завод "Теплоприбор" (71) Заявители (54) ВРЕМЯ вЂ” ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ

ПРЕОБРАЗОВАТЕЛЬ

Rx ах 7 ("- Qк) . 25 т — т»0

T К вы» т т„— ту„

Изобретение относится к вычисли-. тельной технике и может быть использовано как функциональный преобразователь время-импульсных сигналов и как устройство деления временных интервалов, необходимое, например, для реализации логометрического алгоритма компенсации влияния диэлектрических свойств среды на показания уровнемера.

Известен время-импульсный функциональный преобразователь (ВИПФ), представляющий частотно-импульсную следящую систему, включающую в себя реверсивный счетчик, двоичный умножитель, блок умножения . — деления, импульсно-потенциальные элементы И, элементы НЕ и ИЛИ j1) .

На выходе устройства формируется временной поток прямоугольных импуль- 20 сов, среднее значение скважности которых пропорционально значению аппроксимирующей функции, (, 6м где О = —, ОХ = - — относительнь1е длительности щ выходного и входного сигналов; à — длительность входного импульоа;

Т вЂ” период следования импульсов;

F, F<> - высокостабильные опорные о< ° частоты;

Х=" — Ф"

-- о 01

Однако известное устройство имеет ограниченный класс воспроизводимых функций (только с положительной первой производной), что обусловлено представлением воспроизводимой функции в виде отношения полиномов первой степени с фиксированным коэффициентом у . Кроме этого, оно отличается большой погрешностью преобразования, обусловленной низким порядком степеней номиналов числителя (N) и знаменателя (и), в = л = ).

Известен также время-импульсный функциональный реобра, выполняющий преобразование вида

840898 где К вЂ” коэффициент пропорциональт ности;

Тх — текущий интервал времени первого канала;

Т вЂ” текущий интервал времени

М второго канала; т, T — начальные значения соответственно Т и Т

Х М

Известный преобразователь содержит усредняющие блоки УБ1, УБ2, ге нератор пилообразного напряжения (ГПН), схему сравнения (CC), триггер -10 формирователь (Ф) выходного интервала Т0 х Е27

Недостатками преобразователя являются низкая точность воспроизведения заДанной функции, обусловленная использованием ключевых элементов и операционных усилителей, наличием температурного дрейфа и временной нестабильностью, низкая технологичность, обусловленная использованием прецизи- 26 онных элементов и необходимость настройки.

Наиболее близким к предлагаемому по технической сущности является делительное устройство, содержащее Ре- 25 гистр, двоичный умножитель, счетчик делимого, триггер, первый элемент И, причем разрядные выходы регистра соединены с входами множителя двоичного умножителя, первый и второй входы первого элемента И соединены соответ- ственно с выходом двоичного умножителя и выходом триггера, а выход элемента И соединен с первым счетным входом счетчика делимого, выход которого соединен с единичным входом триггера ГЗ ., К недостаткам данного устройства относится узкий класс решаемых им задач.

Цель изобретения - расширение клас-40 са решаемых задач.

Поставленная цель достигается тем, что устройство, содержащее регистр, двоичный умножитель, счетчик делимого, триггер, первый элемент И, при- 45 чем разрядные выходы регистра соединены с входами множителя двоичного умножителя, первый и второй входы первого элеыента И соединены соответственно с выходом двоичного умножителя и выходом триггера, а выход элемента И соединеи с первым счетно входом счетчика делимого, выход которого соединен с единичным входом триггера, выход триггера является выходрм преобразователя, дополнительно содержит элементы И, два счетчика, формирующие триггеры и формирователь сигналов управления, при этом входы установки нуля первого и второго формирующих триггеров являются соответ- 60 ственно входами первого и второго операндов функционального преобразователя, входы второго и третьего элементов И соединены с разрядными выходами второго счетчика, импульсный 65 вход второго счетчика, вход импульсной последовательности двоичного умножителя, вход формирователя сигналов управления, первые входы четвертого и пятого элементов И соединены с входом импульсной последовательности функционального преобразователя, выходы второго и третьего элементов

И соединены соответственно с входами установки единицы первого и второго формирующих триггеров, вторые входы четвертого и пятого элементов И соединены соответственно с нулевым выходом первого формирующего триггера и единичным выходом второго формирующего триггера, выходы четвертого и пятого элементов И соединены соответ- ственно со вторым счетным входом счетчика делимого и импульсным входом первого счетчика, первый„ второи и третий выходы формирователя сигналов управления соединены соответственно с входом установки нуля второго счетчика, третьим входом четвертого элемента И и третьим входом пятого элемента И, четвертый выход формирователя сигналов управления соединен с входом установки нуля счетчика делимого и входои записи регистра, пятый выход формирователя соединен с входами установки нуля первого счетчика и двоичного умножителя и входом установки нуля триггера.

Кроме того, . формирователь сигналов управления содержит делитель частоты:, триггер и два элемента И,- при этом. счетный вход делителя частоты является входом формирователя сигналов управления, выход делителя частоты соединен со счетным входом триггера первыми входами первого и второго элементов И и является первым выходом формирователя, единичный выход триггера соединен со вторым входом первого элемента И и является вторым выходом формирователя, нулевой выход триггера соединен со вторым входом второго элемента И и является третьим вйходом формирователя, выходы первого и второго элементов И являются соответственно четвертым и пятым выходами формирователя..

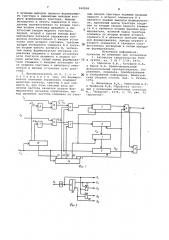

На фиг. 1 изображена схема функцио-. нального преобразователя; на фиг. 2 схема формирователя сигналов управленияр на фиг. 3 — временная диаграмма работы преобразователя.

Преобразователь содержит регистр

1, двоичный умножитель 2, счетчик 3 делимого, триггер 4, элементы И 5-9, счетчики 10 и.11, формирующие триггеры 12 и 13, формирователь 14 сигналов управления.

Схема формирователя сигналов управления содержит делитель частоты 15, триггер 1б, элементы И 17 и 18.

Входы первого и второго операндов устройства подключены к входам установки нуля триггеров 12 и 13, входы

840898

35 установки, единицы которых через элементы И б и 7, служащие для выделения кодов т„о и 1 т д, подключены к разрядным выходам счетчика 10. С выходов

"J." и "0" формирующих триггеров 12 и

13 сигналы поступают на вторые входы двух трехвходовых элементов И 8 и 9, на первые входы которых подается опорная частота Fä, с входа импульсной последовательности преобразователя, которая одновременно подается на вход ДУ 2, на вход счетчика 10 и вход формирователя 14 сигналов управления.

Выходы элементов И 8 и 9 подключены ко входам двух счетчиков 3 и 11. Выход счетчика 3 подключен к установочному входу триггера 4. Разрядные 15 выходы счетчика 11 подключены ко входам регистра 1, выходы которого подключены к входам ДУ 2. Выход ДУ 2 подключен ко входу элемента И 5, выход которого подключен к первому Щ импульсному входу счетчика 3. Второй вход элемента И 5 подключен к выходу триггера 4, являющемуся выходом преобразователя.

С выходов формирователя 14 сигналов управления поступают импульсы управления: g — для обнуления счетчика 10; 9, g поступают на третьи входы элементов И 8 и 9 для определения моментов прохождения сигналов;

gg — для обнуления счетчика 3 и, одновременно, для записи в регистр 1 кода счетчика 11; g+ — для обнуления счетчика 11 и ДУ 2 й, одновременно, для установки триггера 4 в исходное состояние.

Предлагаемый ВИФП является устройством циклического действия.

Цикл работы устройства состоит из

2-х тактов. Работа устройства поясняется временными диаграммами на 4О фиг. 3.

В первом такте на выходе триггера

12 формируется импульс отрицательной полярности (ж), длительноСть которого равна Разности тх — тхо. при 4 этом величина Т определяется моменх том прихода входного сигнала (д), а длительность Т о — моментом выделения кода T (е). В течение первого такта на вход счетчика 3 (з) поступает. число импульсов, равное

М., = Fo Тт - Fg (Т)(- Тхо)

Х МО

2 <0 F (Т - Т 0) 10 Ь поскольку т = - 1 о Ьз

ЫО 0" З т - р 10 где п„о — разрядность счетчика 10; и — разрядность счетчика 3.

Счетчик 3 заполняется до величины (10 а — Мь.„ ) (л). Во втоРом такте происходит формирование импульса положительной полярности длительностью ц) .Т вЂ” Т (д-ж), заполняемого импульса сами опорной частоты, поступающими на вход счетчика 11 (и). В этом счетчике образуется код N > Га (Т - Т о), который переписывается в регистр 1 65 и преобразуется в частоту следования !

М импульсов г = Ы,р (к). В начале

2ns второго такта с приходом импульса

94 триггер 4 устанавливается в нулевое состояние, в результате этого импульсы частоты Г проходят через элемент И 5 на-первый вход счетчика 3.

Импульсы частоты Г „ заполняют счетчик 3 (и) до максимального значения (л) и импульс переполнения устанавливает триггер 4 в "единичное" состояние, запрещая дальнейшее прохождение импульсов частоты Га„и завершая формирование выходного сигнала Тзь,„(м) преобразователя.

Таким образом, для счетчика Й1 имев э П .10 — И + Тз„„Г = 1O

3 — з

1-й такт 2-й такт

Отсюда

" х (T> Т ) в Тх -Тхо 2"«

Жи, т -т о 3 0

Тх- Тхо 2

=k. г -т о.

Формула изобретения

1. Время — импульсный функциональный преобразователь, содержащий регистр, двоичный умножнтель, счетчик делимого, триггер, первый элемент И, причем разрядные выходы регистра соединены с входами множителя двоичного умножителя, первый и второй входы первого элемента И соединены соответственно с выходом двоичного умножителя и выходом триггера, а выход элемента И соединен с первым счетным входом счетчика делимого, выход которого соединен с единичным входом триггера, выход триггера является выходом преобразователя, о т л и ч аю шийся тем, что, с целью расширения класса решаемых задач, в него дополнительно введены элементы И, два счетчика, формирующие триггеры и формирователь сигналов управления, при этом входы установки нуля первого и второго формирующих триггеров являются соответственно входами первого и второго операндов функциональ-ного преобразователя, входы второго и третьего элементов И соединены с разрядными выходами второго счетчика, импульсный вход второгс счетчика, вход импульсной последовательности двоичного умножителя, вход формирователя сигналов управления, первые входы четвертого и пятого элементов И соединены с вхбдом импульсной последовательности функционального преобразователя, выходы второго и третьего элементов И соединены соответственно с входами установки единицы первого и второго формирующих триггеров, вторые входы четвертого и пятого элементов И соединены соответственно

840898 с нулевым выходом первого формирующего триггера и единичным выходом второго формирующего триггера, выходы четвертого и пятого элементов И соединены соответственно со вторым счетным входом счетчика делимого и импульсным входом первого счетчика.

5 первый, второй и третий выходы формирователя сигналов управления соединены соответственно с входом уста новки нуля второго счетчика, третьим входом четвертого элемента И и третьим входом пятого элемента И, четвертый выход формирователя сигналов управления соединен с входом установки нуля счетчика делимого и входом за,.писи регистра, пятый выход формирова- 15 ! теля соединен с входами установки нуля первого счетчика и двоичного умножителя и входом установки нуля триггера.

2. Преобразователь по п. 1, о т- 2О л и ч а ю шийся тем, что формирователь сигналов управления содержит делитель частоты, триггер и два элемента И, при этом счетный вход делителя частоты является входом формирователя сигналов управления, выход делителя частоты соединен со счетным входом триггера первыми входами первого и второго элементов И и является первым выходом формирователя, единичный выход триггера соединен со вторым входом первого элемента И и является вторым выходом формирователя, нулевой выход триггера соединен со вторым входом второго элемента И и является третьим выходом формирователя, выходы первого и второго элементов И являются соответственно четвертым и пятым выходамн формирователя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 363990, кл. С 06 Г 7/39, 1973.

2. Одиноков В.Ф., Астафьев А.А ° и UJapoa В.А. Время-импульсный функциональный преобразователь. Управление, передача, преобразование и отображение информации. Межвузовский сборник статей. Вып. 3, Рязань, 1976.

3. Мельников A,A., Рыжевский А .Г. и ТриФонов E.Ô. Обработка частотных и временных импульсных сигналов.

М., "Энергия", 1976, с. 70, рис. 52 (прототип).

840898 и

10 -М„

Составитель Г. Плешев

Текред 3 . Фанта Корректор B. Бутяга

Редактор Н. Лазаренко

Подписное

Заказ 4767/72 Тираж 745

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент". r. Ужгород, ул. Проектная, 4