Устройство для вычисления интегра-лов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к аат. сеид-ву(22) Заявлено 1603.76 (21) 2335236/18-24 (51)М. Кл.з

G 06F 7/64 с присоединением заявки МЗ

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 2306.81.Бюллетень М 23

Дата опубликования описания 230М1 (53) УДК 681. 325 (088.S) (72) Авторы изобретения

В.И. Жабин, В.И. Корнейчук, В.П. Тарасенко и A.À. Щербина

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалист ческбй революции

Э (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ИНТЕГРАЛОВ

Изобретение относится к вычислительной технике и может быть применено в цифровых моделирующих устрой1 ствах для вычисления интеграла на интервале (О, Х1 от функции, представ-5 ленной многочленом.

Известно устройство для вычисления интегралов, содержащее регистр подынтегральной функции, сумматоры и регистр, в котором накапливается результат P1).

Однако это устройство имеет большое время вычисления интеграла.

Наиболее близким qo технической сущности к предлагаемому является 15 устройство для вычисления интегралов, содержащее блок управления, накапливающий блок и и решающих блоков, каждый из которых содержит арифметический узел, сумматор остатка, ре- 20 гистр остатка, регистр порядка и блок элементов И-НЕ, причем группа ,выходов блока управления соединена группой входов арифметического узла, группа выходов которого подключена 25 к первой группе входов сумматора остатка, вторая группа входов которого соединена с группой выходов регист ра остатка, первая группа выходов которого подключена ко входу регист- 30 ра порядка и первому входу блока элементов И-НЕ, группа выходов которого подключена к .соответствующей группе входов накапливающего блока(2

Недостатком известного устройства является низкое быстродействие.

Цель изобретения — увеличение быстродействия устрой тва для вычисления интегралов на интервале (О, Х) от функции, представленной многочленом.

Поставленная цель достигается тем, что каждый из и решающих блоков дополнительно содержит К выходных сумматоров и коммутатор, а накапливающий блок содержит два дешифратора, и сумматор, причем первая rруп— па выходов сумматора остатка i-ro решающего блока (где i 1, 2, ...и) соединена с первой группой входов коммутатора того же блока, вторая, третья ..., (K+1) группы входов коммутатора подключены к соответствующим группам выходов K выходных сумматоров, первые группы входов которых соединены с первой группой выходов сумматора остатка, а вторые группы входов выходных, сумматоров подключены к группе выходов регистра порядка, старшие разряды каждого

840901 из К выходных сумматоров соединены с соответствующими входами блока элементов И-НЕ, группа выходов которого подключена к четвертой группе входов коммутатора, группа выходов которого подключена к первой группе входов регистра остатка, вто, рая группа входов которого соединена со второй группой выходов сумматора остатка, группы входов накапливающего блока через первый дешифратор, сумматор, и второй дешифратор связаны с группой выходов накапливающего блока.

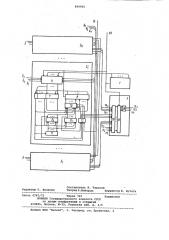

На чертеже изображена структурная схема устройства для вычисления интегралов. 15

Устройство содержит блок 1 управления, и решающих блоков 2 и накапливающий блок 3.

Блок управления может быть выполнен как кольцевой сдвиговый регистр Щ или как счетчик с дешифратором.

Каждый решающий блок 2 содержит арифметический узел 4, ко входам которого подключены входные шины 5.„, 52, 5 и 6„, 6,, 6, а также выходы блока 1 управления. Выходы узла 4 подведены ко входам младших разрядов сумматора 7 остатка, ко входам которого со сдвигом на один разряд влево (т.е. в сторону старших разрядов) подключены выходы регистра 8 остатка, выполненного на триггерах с внутренней задержкой. Выходы старших разрядов сумматора 7 соединены со входами выходных сумматоров 9 и

9 и коммутатора 10, соединенного

35 со входами старших разрядов регистра 8, а выходы остальных младших разрядов сумматора 7 связаны со входами остальных разрядов регистра 8.

Выходы регистра 11 порядка соедине- 4Q ны со входами róììàòaðîâ 9, связан-= ных со входами коммутатора 10, причем ко входу сумматора 9 выходы регистра 11 подведены со сдвигом влево на один разряд. КРоме того„ 45 выход знакового разряда сумматора 7 подключен к управляющему входу реги стра 11 и к первому входу блока элементов И-НЕ 12, выполняющего систему переключательных функций.

Ко второму и третьему входам блока

12 подведены выходы знаковых разрядов сумматоров 9„ и 9, а с четвертым входом, соединена шина 13 признака инвертирования. Первый, второй и третьей выходы блока 12 соединены соответственно с выходными шинами 14„, 14, 14, блока 2,а три управляющих входа коммутатора 10 связаны соответственно со вторым, первым и четвертым выходом. Накапливающий блок @)

3 содержит сумматор 15, выходы которого через первый дешифратор 16. связаны с выходными шинами 14 всех ,блоков 2 и входными шинами 17,, 17 17 начального условия, а выходы трех старших разрядов сумматора 15 через второй дешифратор 18 соединены с выходными шинами 19„, 19,. 19. накапливающего блока 3. Синхронизирующая шина 20 подключена к цепям сдвига в блоке 1 управления, к управляющему входу узла 4 и к цепям приема кода на регистр,8 во всех блоках 2, и к цепям сдвига сумматора 15 в накапливающем блоке 3.

В исходном состоянии (цепи установки исходного состояния на чертеже не показаны) в блоке 1 управления единица находится в крайнем левом положении. В каждом i-ом блоке 2 в регистре 11 записано число i. В регистре 8 и сумматоре 15 записаны нули.

В. каждом j-ом цикле на входные шины 5 каждого блока 2 поступает очередная цифра у. числа а; Х = У (т.е. численного значения в точке Х

i-го члена подынтегральной функции), а на входные шины 6 поступает очередная цифра х числа Х. В устройстве числа подаются на входные шины и формируются на выходных шинах последовательно, начиная со старших разрядов, в избыточном двоичном коде с цифрами -2, -1, О, +1, +2, причем единица на первой и второй шинах имеют вес соответственно 2 и 2", а третья шина знаковая. При этом с выходов узла 4 на вход сумматора 7 поступает число, равное у Х + х- . „, 3 3 5 где Х Y.., — числа Х и У, представленные соответственно только j u j-1 старшими цифрами. Это число складывается в сумматоре 7 с содержимым регистра 8 и знак полученной суммы управляет выдачей кода из регистра

11 таким образом, что еслй эта сумма отрицательна, то на сумматоры 9 выдается прямой код числа хранимого на регистре 11, в противном случае выдается дополнительный код. Кроме того, на сумматоры 9 поступает содержимое старших разрядов сумматора 7. Блок 12, анализируя состояние знаковых разрядов сумматоров 7, 9„, 9 и шины 13 признака инвертирования вырабатывает управляющий сигнал для коммутатора 10 и очередную цифру Z. результата (т.е. числа

Ь„. „ Х"+", являющегося численным значением в точке Х i+1-го члена .первообразной функции, представлен1 ной многочленом), которая,.выдается на выходные шины 14 блока 2. Так, если значения знаковых разрядов сумматоров 7 и 9 совпадают, то формируется цифра результата Zj, равная по модулю двум, и коммутатор 10 ко входам старших разрядов регистра 8 подключает выходы сумматора 9 . Если предыдущее условие не выполняется, но совпадают значения знаковых разрядов. сумматоров 7 и 9,, то формируется цифра Z, равная по модулю 840901 единице, и коммутатор 10 подключает ко входам старших разрядов регистра 8 выходы сумматора 9„ . Если же не выполняются оба предыдущие условия, то формируется цифра Z, равная нулю, и коммутатор 10 ко входам регистра 8 подключает старшие разряды регистра сумматора 7. При отсутствии сигнала на шине 13 знак цифры результата Z формируется рав-.

7 ным знаку числа на сумматоре 7, в противной слччае знак Е противоположен знаку кода сумматора 7. В накапливающем блоке 3 в каждом цикле вычисления происходит сложение цифр, поступающих по входным шинам начального условия 17 и цифр с выходов блоков 2. Результат накапливается в сумматоре 15 и в каждом цикле в трех его старших разрядах формируется очередная цифра численного значения интеграла. Схемы 16 служат для преобразования цифр из прямого кода в код удобный для работы сумматоров (например, дополнительный), а схема 18 на выходе блока 3 — для обратного преобразования. В конце цикла следует. сигнал в шине 20, по которому в блоке 1 единица сдвигается на разряд вправо, во всех блоках 2 в регистры 8 заносится код, сформированный на входе этих регистров, в сумматоре 15 значение знакового разряда записывается в соседний младший разряд, а в остальных разрядах происходит сдвиг на один разряд в сторону старших разрядов.

Время вычисления интеграла на интервале (О, Х) от функции, представленной многочленом, в предлагаемом устройстве не зависит от Х, причем задержка появления старшей цифры результата составляет пять циклов, т.е. для получения значения интеграла с точностью да и разрядов, необходимо выполнить и+5 циклов вычисления.

В известных устройствах, время вычисления только одного члена .суммы превышает время вычисления интеграла в предлагаемом устройстве. Следовательно, предлагаемое устройство по меньшей мере в К раз превосходит по быстродействию известные, где K — количество членов суммы, зависящее от заданной точности вычисления и от величины интервала ин,тегрирования.

Формула изобретения

Устройство для вычисления интегралов, содержащее блок управления

15

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР

Р 469980, кл. G Об J 1/02, 1974.

55 2. Авторское свидетельство СССР

Р 388278, кл. G 06 J 1/02, 1972 (прототип). накапливающий блок и и решающих. блоков, каждый из которых содержит арифметический узел, сумматор остат ка, регистр остатка, регистр порядка и блок элементов И-НЕ, причем группа выходов блока управления соединена с группой входов арифмети-, ческого узла, группа выходов которого подключена к первой группе входов сумматора остатка, вторая группа входов которого соединена с группой выходов регистра остатка, первая группа выходов которого подключена ко входу регистра порядка и первому входу блока элементов И-НЕ, группа выходов которого подключена к соответствующей группе входов накапливающего блока, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия; каждый иэ и решающих блокоВ дополнительно содержит K.âûõîäíûõ сумматоров и коммутатор, а накапливающий блок содержит два дешифратора, и сумматор, причем первая группа выходов сумматора остатка i-ãî решающего блока (где — 1, 2, ... n) соединена с первой группой входов коммутатора того же блока, вторая, третья, ..., (К+1) группы входов коммутатора подключены к соответствующим группам выходов

k выходных сумматоров, первые группы входов которых соединены .с первой группой выходов сумматора остатка, а вторые группы входов выходных сумматоров подключены к группе выходов регистра порядка, старшие разряды каждого иэ K выходных сумматоров соединены с соответствующими входами блока элементов И-НЕ, группа выходов которого подключена к четвертой группе входов коммутатора, группа выходов которого подключена к первой группе входов регистра остатка, вторая группа входов которого соединена со второй группой выходов сумматора остатка, группы входов накапливающего блока через первый, дешифратор, сумматор и второй дешифратор связаны с группой выходов накапливающего блока.

Составитель В. Тарасов

Техред Н.Майорош Корректор В. Бутяга

Редактор Г. Волкова

Заказ 4767/72 Тираж 745

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб. д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4