Вычислительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ()840902 (61) Дополнительире к авт. свид-ву— (51)М. К,.з (22) Заявлено .06.0178 (21) 2568046!18-24

G 06 F 7/68 с присоединением заявки ¹

Государственный комитет

СССР. ио делам изобретений и открытий (23) Приоритет (53) УДК 681. 325 (088.Ц) Опубликовано 230681.Бюллетень No 23

Дата опубликования описания 23.0681

Р.А. Воробель, В. Б. Дудыкевич и Б.A. ПопОв (72) Авторы изобретения физико-механический институт AH Украинской СР и Львовский ордена Ленина политехнический." институт

I (71) Заявители (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике.

Известно устройство, содержащее преобразователь код-частота, счетчики импульсов, блок сравнения кодов, регистр сомножителя, элементы И 11 .

Недостатками известного устройст.ва являются ограниченные функциональные возможности и сложность.

Наиболее близким по технической .сущности к предлагаемому является вы числйтельное устройство, содержащее два двоичных делителя частоты, каждый из которых состоит из регистра, блока сравнения кодов и счетчика, 15 два счетчика, элемент И и элемент запрета, соединены со счетными входаМи первого и третьего счетчиков (.2), Для выполнения операции сложения двух чисел Х и У в счетчик результа- 20 та записывается число Х, а в счетчик-регистр вносится число у в дополнительном коде. Счетчики первого и второго двоичных делителей частоты устанавливаются в нулевое состояние, а в регистры первого и второго двоичных делителей частоты заносится единица в младшие разряды. Тактовые импульсы проходят через двоичные делиХели на счетчик результата и счетчик- 34 регистр до тех пор, пока на счетчикрегистр не будет передано число У, переводящее его в нулевое состояние.

В этот момент срабатывает дешифратор нулевого состояния, закрывает элемент запрета и тем самым прекращает поступление тактовой частоты на входы двоичных делителей. В счетчике результата при этом формируется число Х + У, за время, равное

С 9 ° (s) где Т0 — период частоты F .

Работа устройства в режиме вычитания отличается от режима сложения занесением в счетчик-регистр прямого кода числа У. Тогда, в мОмент запира" ния элемента запрета потенциалом эле мента И, в счетчике результата формируется число N = Х + N — У = Х вЂ” У, где N = 2 — коэффициент пересчета

tl

GATI счетчика-регистра и счетчика результата. Этот результат формируется за время, равное Shit

° Для умножения двух чисел Х и У перед началом операции сомножитель Х записывается в регистр первого двоичного делителя, а дополнительный код числа У вЂ” в счетчик-регистр; счетчики двоичных делителей и счетчик ре840902 зультата устанавливаются в нулевое состояние, а в регистр второго двоичного делителя частоты заносится единица. Тогда на выходе счетчика-регистра формируется последовательность импульсов с периодом Т» Х. После пос.тупления У импульсов в счетчик-регистр за время

Tg (3) в счетчике результата формируется число

N= г ° то х.v=x Y (4)

При выполнении операции деления в исходном состоянии счетчики двоич-. ных делителей и счетчик результата находятся в нулевоМ состоянии. В регистр первого двоичного делителя 15 заносится единица, в регистр второго двоичного делителя — код числа У, а в счетчик-регистр - дополнительный код числа Х. Тогда после поступления Х импульсов в счетчик-регистр 20 с выхода первого двоичного делителя частоты, .за время (s) в счетчике результата формируется код числа

N — О.Х Т = — (6) Х (0 Ч

Недостатками известного устройства являются черезмерная сложность и низкое быстродействие.

Цель изобретения — повышение быстродействия и упрощение устройства.

Поставленная цель достигается тем, что в устройство, содержащее дваз5 регистра операндов, два счетчика, элемент И, элемент запрета, причем выходы первой группы первого счетчика соединены соответственно с входа-. ми элемента И, выход которого соединен с входом управления элемента

40 запрета, информационный вход которого является входом импульсной последовательности устройства, дополнительно введены две группы элементов

И, два операционных блока, два эле- 45 мента ИЛИ, при этом первые входы операционных блоков соединены с выходом элемента запрета, вторые входы, первого и второго,.операционных блоков — с выходами соответственно пер- 50 вого и второго элементов ИЛИ, выходы операционных блоков соединены со счетными входами соответственно первого и второго счетчиков, выходы второй глупцы первого счетчика и выходы второго счетчика соединены соответственно с информационными входами первой и второй групп элементов

И, входы управления которых соединены соответственно с выходами первого и второго регистров операндов, 40 а выходы — со входами соответствующих элементов ИЛИ.

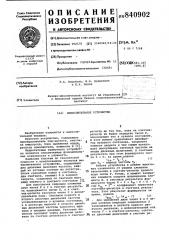

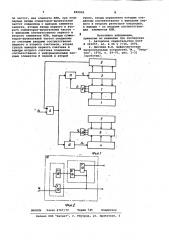

На фиг. 1 приведена схема устройства; на фиг. 2 - схема операционного блока. 65

Устройство содержит регистры 1 и 2 операндов, счетчики 3 и 4, элемент И 5, элемент 6 запрета, группы элементов И 7 и 8; элементы ИЛИ 9 и 10; операционные блоки 11 и 12.

Каждый операционный блок включает триггер 13, элемент И 14, элемент

ИЛИ 15, элемент 16 задержки. При этом первый вход элемента ИЛИ является первым входом операционного блока, второй вход элемента ИЛИ соединен с выходом элемента задержки, а выход элемента ИЛИ соединен с первыми входами элемента И и триггера и является выходом операционного блока., второй вход триггера является вторым входом операционного блока, выход триггера соединен со вторым входом элемента И, выход которого соединен с входом элемента задержки.

Устройство работает. следующим образом.

На первые входы операционных блоков 11 и.12 при открытом элементе 6 запрета поступает тактовая частота F, Регистр 1 операнда с группой 7 элементов И, элементом ИЛИ 9 и счетчиком 3 представляет собой двоичный умножитель частоты, управляемый ко-. дом числа Z„ регистра 1, поэтому частота F на выходе элемента ИЛИ 9 on I ределяется выражением= т ят„, (7) где F — частота йа выходе блока 11;

Z - число, соответствующее коду в регистре 1; М„„ = 2 - коэффициент пересчета счетчика 3; и - количество разрядов регистра 1 и счетчика 3.

Так как частота F< поступает на второй вход блока 11, то, в соответствии с фиг. 2, частота F на его выходе определяется выражением

F2. FO+ FQ F1 откуда, с учетом (7), р ГO Nrn (&) .г,„

Регистр 2 с группой элементов И 8, элементом ИЛИ 10 и счетчиком 4 представляет собой двоичный умножитель частоты, управляемый кодом числа Z регистра 2. Поэтому частота F на выходе элемента ИЛИ 10 определяется выражением

3 4

2 (9) .4 N где F4 — частота на выходе блока 12 °

tl

N = 2 — коэффициент пересчета счетФ чика 4; п-количество двоичных разрядов регистра 2 и счетчика 4.

С выхода элемента ИЛИ 10 частота

F+ поступает на второй вход блока 12, поэтому, в соответствии с фиг. 2, частота Г4 на его выходе определяется выражением F4 = Г +. F4 - F, откуда, с учетом (9), . р Ш . (а)

Для выполнения операции сложения двух чисел Х и У, в исходном состоя840902

1О

Ч.A сл- F

20 сл 4 га, М„„Р

Формула изобретения нии в счетчик 4 записывается код числа Х, а в регистры 1 и 2 — код числа A. В счетчик 3 вносится дополни- . тельный код числа У,. а именно код числа М - У. После внесения кода чисfTl ла в счетчик 3 элемент И 5 открывает элемент б запрета и импульсы тактовой частоты Га поступают на первые входы блоков 11 и 12. После поступления У импульсов на вход счетчика 3, в соответствии с (8), за время лемент И 5 закрывает элемент 6 запета и тем .самым прекращает поступле- )$ ние тактовой частоты Ftl на первые входы блоков 11 и 12.

За время „ (11) в счетчике 4 формируется код числа, в соответст вии с (10), 25 т.е. сумма двух чисел Х и У.

Для выполнения операции вычитания двух чисел Х и У в исходном состоянии в счетчик 4 записывается код числа Х, а в регистры 1.и 2 — код числа A. В счетчик 3 вносится код числа У. После внесения кода в счетчик

3 элемент И 5 открывает элемент запрета, и импульсы тактовой частоты .,поступают на первые входы блоков 11 и 12. После поступления N» — У им- 35 пульсов с выхода блока 11 на вход счетчика 3, в соответствии с (8) за время

40 (М„;Ч) ь - „-й„„ элемент И 5 закрывает элемент 6 зайрета. За .это время, tat,lN в счетчике

4, в соответствии с (10), формируется код числа (И -Ч1A а п-Х- +Й,п="" 5() =х+1 „Р =Х вЂ”,; = 3 т.е. разница чисел Х и У.

При выполнении операции умножения двух чисел Х и У, в исходном состоянии код числа Х заносится в регистр

i код числа A заносится в регистр 2 и дополнительный код числа У, т.е

N - У заносится в счетчик 3. Пос111 ле занесения кода в счетчик 3 откры- 60 вается сигналом элемента И 5 элемент б запрета и импульсы тактовой частоты поступают на первые входы блоков

11 и 12. Как тольКо на вход счетчика

3 поступит У импульсов с выхода блока 65

11 за время, равное, в соответствии с (8), Ч.Х мн р ., о элементом И 5 закрывается элемент 6 запрета и в счетчике 4 формируется код числа

Fа - Nle (.X N t F A A (1Ь) ми 4 .н

I т.е. произведение двух чисел Х и У.

При выполнении операции деления числа Х на число У, в исходном состоянии код числа У заносится в регистр 2, код числа A заносится в регйстр 1 и дополнительный код числа

Х заносится в счетчик 3. После открытия элемента И 5 элемента б запрета тактовая частота поступает на первые входы блоков 11 и 12 и как только на вход счетчика .3 поступит

Х импульсов с выхода блока 11,,за время, равное в соответствии с (8)., «>). ел элементом И 5 закрывается элемент б запрета и в счетчике 4 формируется, в соответствии с (10), код числа

4 Ч г йп„ч т.е. частное от деления чисел Х и У.

Таким образом, предлагаемое устройство выполняет все четыре арифметические операции.

Сравнивая выражения (1, 3 и 5) соответственно с (11, 13, 15 и 17) видим, что в предлагаемом устройстве быстродействие выполнения операции сложения, вычитания, умножения н деления увеличено.

Следовательно, включение в состав устройства двух схем сложения-вычитания и изменение связей позволили существенно упростить устройство (количество счетчиков уменьшилось с четырех до двух), а также повысить

его быстродействие.

Вычислительное устройство, содержащее два регистра операндов, два счетчика, элемент И, элемент запрета, причем первая группа выходов первого счетчика соединена с входами элемента И, выход которого соединен со входом управления элемента запрета, информационный вход которого является входом импульсной последовательности устройства, о т л и ч а ю щ ее с я тем, что, с целью упрощения устройства, оно содержит две группы. элементов И, два сумматора-вычитате840902

Я иг.8

ВНИИПИ Заказ 4767/72 Тираж 745 Подписное филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 ля частот, два элемента ИЛИ, при этом первые входы сумматоров-вычитателей частот соединены с выходом элемента запрета, вторые входы первого и вто-, рого сумматоров-вычитателей частотс выходами соответственно первого и второго элементов ИЛИ, выходы сумматоров-вычитателей частот-соединены со счетными входами соответственно первого и второго счетчиков, вторая группа выходов первого счетчика и выходы второго счетчика соединены .соответственно с информационными вхо.дами элементов И первой и второй групп, входы управления которых соединены соответственно с выходами первого и второго регистров операндов, а выходы — со входами соответствующих элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. йвторское свидетельство СССР

В 310257, кл. G 06 G 7/16, 1970.

2. Дениев В.П. Цифрочастотные вычислительные устройства. И., "Энергия", 1976, с. 69-70, рис. 2-31 (прототип),