Ячейка памяти для регистра сдвига

Иллюстрации

Показать всеРеферат

«»841051

Союз Советскии

Социвлистическил

РеспубликОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТО РС ХОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 20.09.79 (21) 2825520/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. К .

G 11 С 19/00

Гесударетвеиимй кюмитет

СССР

Опубликовано 23.06.81. Бюллетень № 23

Дата опубликования описания 28.06.81 ио делам изабретений и. открытий (53) УДК 681.327..66 (088.8) (1

1 (72) Автор изобретения

С. А. Киселев

Всесоюзный научно-исследовательский институт охраны труда ВЦСПС (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

Изобретение относится к вычислительной и цифровой измерительной технике и может быть применено при конструировании различных устройств и приборов, в которых необходимо осуществить преобразование информации.

Известен регистр сдвига, содержащий в каждом разряде RS-триггер и три элемента И, шины передачи прямого и обратного кода. Этот регистр сдвига осуществляет сдвиг информации и ее обработку, например сложение (1).

Однако он не позволяет производить умножение двоично-десятичных чисел.

Наиболее близким из известных по технической сущности к предлагаемому изобретению является ячейка памяти для однофазного регистра сдвига, выполненная на

D-триггерах с внутренней задержкой (2).

Недостаток известной ячейки памяти —, невозможность осуществления операции умножения в двоично-десятичном коде.

Цель изобретения — расширение функ- 20 циональных возможностей ячейки памяти за счет обеспечения деления чисел в двоично-десятичном .коде.

Поставленная цель достигается тем, что в ячейку памяти для регистра сдвига, содержащую последовательно соединенные по

D-входу DRS-триггеры и тактовую шину, введены элемента И и дешифратор, выходы которого соединены с R- u S-входами DRS-триггеров, первые входы дешифратора подключены к выходам первого, второго и третьего

DRS-триггеров, второй вход дешифратора соединен с выходом первого элемента И, выход второго элемента И подсоединен к С-входам DRS-триггеров, первые входы элементов И соединены с тактовой шиной, вторые входы элементов И соединены со входами ячейки памяти, выходы четвертого DRS-триггера подключены к выходам ячейки памяти.

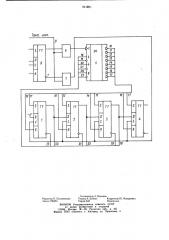

На чертеже представлена функциональная схема предлагаемой ячейки памяти.

Ячейка памяти содержит DRS-триггеры

1 — 4, дешифратор 5, элементы И 6 и 7, DRS-триггер 8 предыдущей ячейки памяти, тактовую шину 9, выходы 10 — 17 дешифратора 5, входы 18 — 23 дешифратора 5.

Ячейка памяти функционирует следующим образом.

В ячейке памяти находится число в двоично-десятичном коде. В том случае, если триг841051

4 тактовый импульс через элемент И 6 проходит на импульсный вход дешифратора 5, с выходов которого импульсные сигналы поступают на R- u S-входы DRS-триггеров 1 — 4 в соответствии с кодом числа на входах де5 шифратора 5. Установка DRS-триггеров 1—

4 производится согласно таблице.

lio

1000

1001

0110

1000

0100

0111

0101

0000

Использование элементов И и потенциально-импульсного дешифратора в регистре обеспечивает возможность деления чисел в двоично-десятичном коде 8 — 4 — 2 — 1 на

2, что позволяет упростить техническое ре- 2s шение схемы преобразования информации.

Формула изобретения

Ячейка памяти для регистра сдвига, содержащая последовательно соединенные по D-входу DRS-триггеры и тактовую шину, отличающаяся тем, что, с целью расширения функциональных возможностей ячейки памяти за счет обеспечения деления чисел з в двоично-десятичном коде, в нее введены элементы И и дешифратор, выходы которого соединены с R- u S-входами DRS-триггеров, 3 гер 8 предыдущей ячейки памяти находится в состоянии «О», тактовый импульс через элемент И 7 проходит на С-входы синхронизации триггеров 1 — 4 и производит сдвиг числа на один двоичный разряд.

В случае, если триггер 8 предыдущей ячейки памяти находится в состоянии «1», первые входы дешифратора подключены к выходам первого, второго и третьего DRSтриггеров, второй вход дешифратора соединен с выходом первого элемента И, выход второго элемента И подсоединен к С-входам DRS-триггеров, первые входы элементов И соединены с тактовой шиной, вторые входы элементов И соединены со входами ячейки памяти, выходы четвертого DRS-триггера подключены к выходам ячейки памяти.

Источники информации, принятые во внимание при экспертизе

1. Грицевский П. М. и др. Основы автоматики, импульсной и вычислительной техники.

«Советское радио», М., 1979 с. 160 — 163.

2. Букреев И. H. и др. Микроэлектронные схемы цифровых устройств. «Советское радио», 1975, с. 140 (прототип).

841051

Гаити имп.

Составитель А. Воронин

Редактор Н. Пушненкова Техред А; Бойкас Корректор Ю. Макаренко

Заказ 4780/81 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4